国家大基金首次入股具身智能,RISC-V+AI赋能具身智能新纪元。3月11日下午,湾芯沙龙邀你一起解锁底层算力密码!

一、产业范式重塑:AI时代的算力主权路径

在大模型长上下文推理及实时具身智能场景下,算力需求呈指数级增长。RISC-V与存内计算(CIM)的融合,不仅是技术层面的演进,更是实现算力主权与自主可控的非避让性战略支点。这种架构设计的底层逻辑源自中国传统的“算盘”理念——即将计算逻辑直接注入存储介质,实现计算与存储的物理一体化。在AI时代,通过架构创新而非单纯依赖先进制程突破,是国产算力实现“换道超车”的核心逻辑。存算一体架构能从根本上消除搬运开销,将能效比提升5-10倍,这使得在成熟工艺(如22nm)下实现等同于先进制程(如7nm)的算力密度成为可能,且成本可压缩约4倍。

二、 核心架构解析:微纳核芯 3D-CIM™ 与算力逻辑重定义

架构变革已从二维平面演进至三维垂直堆叠。微纳核芯(NCC)首创的 3D-CIM™ 技术体系,通过将存储单元与计算逻辑在三维空间内高密度集成,彻底重定义了物理互联的带宽边界。

2.1 3D-CIM™ 的技术核心

●带宽与 KV Cache 优化: 3D-CIM™ 提供的内部有效带宽远超外置 HBM3 方案,将 KV Cache 访问延迟压缩至极限,极大优化了大模型推理中的首字延迟(TTFT)。

●99/1 算力分配: 在 RV-CIM™ 异构架构中,99% 的张量(Tensor)计算由 CIM 阵列原位完成,而剩余 1% 的标量(Scalar)/控制流逻辑则由 RISC-V CPU 处理,实现了计算资源的最优配置。

●物理指标: 据微纳核芯公布的数据,相比传统架构,3D-CIM™ 实现了 4 倍以上的算力密度提升和 10 倍以上的功耗降低。

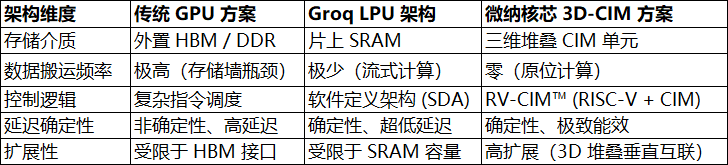

2.2 核心算力架构对比分析

微纳核芯的CIM架构相比传统GPU以及Groq 语言处理单元(LPU)架构,有如下优点。

2.3 物理互联、经济性与能效评估

3D-CIM™的核心在于利用混合键合(Hybrid Bonding)和垂直通孔(TSV)技术,将计算层与存储层紧密集成。

●跨代制程红利: 3D-CIM™可以在 22nm成熟工艺 下实现比肩7nm先进制程 芯片的算力密度。该方案可将单位算力的成本降低约4倍 ,极大缓解了对先进制程设备及工艺的依赖。

●能效比飞跃: “原位计算”消除了总线上的长距离搬运,实现 5-10倍的能效比提升 。需指出的是,虽然未来实验室阶段的近阈值RRAM(阻变存储器)存算芯片可达到55.21至88.51 TOPS/W的极端能效,但当前基于SRAM/DRAM的3D-CIM已足以在商用层面支撑边缘大模型的部署。

三、RISC-V与存算一体的协同效应:开源指令集在专用加速中的角色

如果说3D-CIM是强劲的动力引擎,那么RISC-V指令集则是最灵活的“控制平面”。其模块化特性使其成为存算一体架构天然的搭档,有效避免了SoC设计中的“集成地狱(Integration Hell)”。

3.1 异构架构(RV-CIM™)逻辑拆解

在RV-CIM™模型中,资源配置遵循最优效率原则:

●99%的任务(张量计算): 由高密度的CIM阵列负责,实现极致吞吐。

●1%的任务(复杂逻辑调度): 由RISC-V CPU负责。 这种架构不仅提供了丰富的工具链支持,更通过“软件定义硬件”实现了灵活性。例如, 清微智能(TsingMicro)的可重构(RPU)技术 在DeepSeek等模型推理中实现了3倍的能效提升,能够动态适配快速迭代的AI算法。

3.2 高性能演进与Turnkey方案

国产RISC-V内核已进入高性能阵列时代。 进迭时空(SpacemiT)K3 (符合RVA23标准)和 希姆计算NPC架构 ,通过支持FP8精度及1024位向量并行计算,构建了理想的算力底座。相比碎片化的IP授权,这种“交钥匙(Turnkey)”方案显著降低了下游厂商的开发门槛。

四、国产半导体价值链图谱:异构协作的深层网络

中国已构建起从基础 IP、芯片设计到系统软件的紧密协作矩阵,形成了以 RISC-V 为底座、CIM 为核心加速器的异构算力集群。

4.1 高性能演进矩阵

●进迭时空 (SpacemiT): 其发布的 K3 芯片 是全球首颗符合 RVA23 标准的量产 RISC-V 芯片,主频达 2.4GHz 。K3 搭载 8 颗支持 1024 位宽向量并行计算的 X100 大核,并率先支持原生 FP8 精度。其单核性能对比 ARM A76,能够流畅运行 30B 至 80B 参数模型。

●算能科技 (Sophgo): 凭借其高性能 RISC-V 处理器,其 SRA3-40 服务器已实现对 DeepSeek “满血版”(非量化)模型的本地部署支持,是智算中心国产化替代的关键力量。

●希姆计算 (Stream Computing): 基于 NeuralScale NPC 架构 的 STCP920 计算卡,在电信、金融等级别的长视频理解与高并发 OCR 场景中展现了卓越的 DSA(领域专用架构)优势。

4.2 存算一体先行者

●清微智能 (TsingMicro): 依托 RPU(可重构计算) 技术实现“软件定义硬件”。在 DeepSeek 等推理任务中,其能效比提升 3 倍,成本降低 50%,标志着 CIM 已具备替代 GPU 的商用价值。

●千芯科技: 专注于端侧多模态,其 AT690 芯片通过集成的芯来科技 U900 内核,在 22nm 工艺下实现了 24 Tops/W 的稀疏优化能效比。

4.3 生态基石

●芯来科技 (Nuclei): 作为本土 RISC-V IP 龙头,其 NACC (Micro-NPU) 为存算一体芯片提供了标准化的协处理接口。

●隼瞻科技(Wingsemitech):提供面向DSA(领域特定架构)的 RISC-V 专用处理器IP及NPU端侧AI 解决方案,以及ArchitStudio 和 Wing Studio 等敏捷开发EDA设计平台。

●软件适配: 麒麟软件 与澎峰科技 通过优化底层算子库与操作系统内核,确保了架构在 Linux 及 OpenHarmony 上的稳定运行,实现了软硬件的解耦与兼容。

五、战略协作与生态整合:兆易创新入股的资本信号

最近,微纳核芯官宣获得超亿元B轮战略融资,国产IC设计头部企业兆易创新(GigaDevice)也战略投资微纳核芯,这一举措并非单纯的财务投资,而是存储巨头向下游算力市场的深度卡位。

●国产 LPU 研发路径: 兆易创新利用其 NOR Flash/DRAM 资源,配合微纳核芯的 3D-CIM™ 架构,致力于开发具有极致 Token 生成速率的国产化 LPU。

●市场份额目标: 兆易创新计划于 2027-2028 年推出 DRAM 存算一体芯片,目标直指 全球 18% 的市场份额 。预计届时每部 AI 手机中存算一体存储的价值量将达到 18 美元。

●战略价值: 该合作完成了“感、存、算、控、连”五位一体生态的闭环,为中国企业在端侧 AI 手机、AI PC 等千亿级蓝海市场中夺取主导权奠定了基础。

六、高价值应用场景分析:从云端实时到边缘感知

6.1 云端长上下文与多智能体(AI Agents)

3D-CIM™ 架构通过“原位 Cache 处理”解决了大模型向 128K/1M 上下文演进时的显存带宽饥渴。在支撑大规模智能体集群时,终端与云端的成本配比通常维持在 1:2 至 1:3 之间,有效降低了系统的 TCO(总体拥有成本)。

6.2 移动终端与个人助手

在 AI 手机场景下,基于存算一体的移动终端可实现 100-500ms 的低延迟感知响应。

●案例: 搭载 3D-CIM™ 的终端可实现“帮我订一张明早 9 点去深圳的最优机票,并预订公司附近五星级酒店”的本地闭环操作。小米 MiMo-V2-Flash 模型在此类架构支持下,推理效率达 150 tokens/秒,成本仅为闭源模型的 2.5%。

6.3 物理智能(具身机器人)

具身机器人对“感知-决策-控制”三位一体的实时性要求极高。

●毫秒级响应: 进迭时空 K3 芯片通过专用的双实时核与 10 路 CAN-FD 接口,在处理 30B 参数大模型时输出速率达 15 tokens/秒,首字延迟(TTFT)控制在 1 秒以内,确保了机器人电机动作在毫米级的精准控制。

七、产业挑战与未来展望:构建标准化算力底座

7.1 关键技术挑战

●工艺良率: 目前 3D 堆叠工艺良率约 60% ,预计 2027 年需通过工艺优化提升至 80% 以上以降低规模化成本。

●精度控制: 在实现高能效的同时,存内计算需解决模拟/数字混合信号在复杂任务下的精度损失问题。

7.2 标准化机遇

2025 年启动的“全球首个 RISC-V 存算一体标准”标志着中国正从技术的跟随者向定义者转变。该标准通过下设的 算子库、扩展指令集、工具链验证、生态推进 四个子工作组,旨在解决软件生态碎片化问题,实现软硬件全链路的标准化解耦。

7.3 未来三年趋势预测

1.架构融合深度化: RISC-V 内核将与 CIM 单元实现“颗粒级”融合,形成原生 AI 处理器。

2.3D 堆叠常态化: 3D-CIM™ 将成为高性能推理芯片的标配,彻底缓解对 HBM 高端制程的依赖。

3.具身智能爆发: 物理智能硬件将成为存算一体芯片最大的增量市场,推动机器人从单任务向通用服务进化。

结论:定义AI 算力的“中国方案”

“RISC-V + NPU + 存算一体”的融合,是中国半导体产业在地缘政治挤压下,基于底层架构创新给出的必然回答。通过微纳核芯、兆易创新、进迭时空、算能科技等企业的深度协同,中国正利用 3D-CIM™ 与 RISC-V 的灵活性,在成熟制程上构筑起足以对标国际先进制程的算力护城河。这不仅是解决存储墙瓶颈的突破口,更是保障中国在AI下半场竞争中拥有自主、高效且可持续算力主权的核心战略。

![[生态进展] VSCode RISC-V 插件正式支持进迭时空(SpacemiT)AI 拓展指令集](https://xtechcon-static.oss-cn-chengdu.aliyuncs.com/xtimes/xtimes/images/2026-03-02/69a57ce3423bf.jpeg)