动态随机存取存储器(DRAM)芯片除了存取晶体管外,还包含许多其他晶体管,以确保DRAM存储器的完整功能。这些外围晶体管必须满足严格的要求,从而避免“复制粘贴”常规逻辑晶体管的工艺流程。

当前DRAM芯片架构提出的一项关键要求是外围晶体管能够承受550-600℃及以上的热处理。本系列文章的第一部分《DRAM是怎样炼成的?》重点介绍了DRAM基础知识和外围电路,而本部分将详细介绍DRAM外围晶体管,解释从平面高k/金属栅极晶体管到FinFET等不同代热稳定外围晶体管技术。

DRAM外围:从基于SiON的栅极叠层到高k/金属栅极

2018年之前,DRAM外围晶体管主要采用平面逻辑MOSFET技术制造,并采用多晶硅/SiO2或多晶硅/SiON栅极。为了维持DRAM的每比特成本趋势线,这些技术不如用于高性能逻辑的晶体管先进。

然而,为了跟上后续DRAM存储器性能提升的步伐,外围器件亟需改进技术。最明显的解决方案是转向采用高k/金属栅极叠层的平面晶体管架构——这一转变早在2007年就已在逻辑技术的量产中实现。

自2007年左右以来,imec及其合作伙伴一直在积极探索与DRAM兼容的高k/金属栅极晶体管,并向存储器行业提出了多种材料和集成方案。如今,几乎所有搭载DRAM存储器的设备都采用了基于高k/金属栅极的平面外围晶体管技术,而imec在这一领域已保持超过15年的技术领先。

以下是对一些拟议的材料、模块和集成方案的概述,它们的制造复杂性和性能水平各不相同。

高k/金属栅极集成:热稳定的先栅极和后栅极集成流程

imec演示的潜在早期推广解决方案之一基于先栅极集成方法,即在高温源漏结激活退火之前沉积金属栅极。nMOS和pMOS的栅极叠层可通过使用不同的功函数金属和层厚度(例如,n型晶体管采用TiN/Mg/TiN,p型晶体管采用TiN)分别进行优化。

关键参数之一是获得一个有效功函数,其数值对nMOS而言足够低,对pMOS而言足够高,从而确保良好的Ion和Ioff之比。研究人员通过对栅极叠层进行掺杂(pMOS和nMOS采用不同的掺杂剂)实现了阈值电压的偏移。

掺杂材料的选择及其集成也为提高栅极叠层的热稳定性和实现DRAM芯片所需的不同Vth提供了途径。与面向逻辑的解决方案相比,通过采用更厚的栅极叠层,满足了DRAM对低栅极漏电流的特定要求。

图1:平面高k/金属栅极外围晶体管的先栅极集成方法的关键制造步骤示意图。(来源:PSS)

Imec还成功演示了一种热性能改进的后栅极集成方法,也称为替换金属栅极(RMG)流程。在后栅极流程中,首先沉积一个覆盖多晶硅的虚拟栅极,并保持其原位,直到进行结激活退火。随后,用目标金属栅极替换该虚拟多晶硅。

优化的源漏结

源漏结对于确保MOSFET晶体管的功能至关重要。它们是通过在源漏区域创建掺杂梯度而形成的。随着导电沟道长度的不断缩短,超浅结对于确保沟道良好的静电控制至关重要。然而,对于外围晶体管而言,DRAM退火过程中的热处理会导致掺杂剂的非预期扩散,因此需要更复杂的工艺流程来维持所需的掺杂梯度。

这个问题可通过改变结注入方案来解决,例如使用预非晶化注入和结共注入。Imec演示了几组适用于各种阈值电压目标的优化结。

热稳定的硅化物工艺

对于所有晶体管而言,保持源漏接触电阻尽可能低是一个普遍挑战。源漏触点是通过将金属与源漏区相接触,在界面处形成肖特基势垒来实现的。

为了确保低电阻,通常采用两种技术:(1)对源漏区进行重掺杂;(2)对源漏区进行完全硅化——硅化物是通过接触金属与掺杂硅发生反应形成的。

然而,传统上用于逻辑器件的镍(铂)硅化物无法承受与DRAM相关的退火温度。Imec提出了一种基于镍铂(NiPt)的热稳定硅化物模块,通过实施额外的注入和退火步骤来稳定硅化物,从而实现低接触电阻。

基于FinFET的热稳定性外围平台

汽车、人工智能(AI)和机器学习(ML)等应用对DRAM存储器提出了日益严苛的要求,推动了对外围晶体管在速度、可靠性与能效方面的进一步提升。一种可行的发展路径是借鉴逻辑器件的发展思路,从平面高k/金属栅极晶体管转向FinFET结构。

早在2011年,在研发充分验证了鳍状沟道晶体管在性能上的显著优势后,逻辑技术路线图便完成了这一转变:更高的Ion/Ioff、更优的短沟道控制、在更小尺寸下实现更大的驱动电流(由于沟道有效宽度更大)以及更低的功耗——同时控制成本。此外,使用高鳍片还能减少阈值电压失配,这对DRAM感测放大器特别有帮助。

与平面晶体管类似,DRAM 的特定要求使得无法直接采用为常规逻辑器件开发的FinFET工艺流程。为此,imec开发了一个基于FinFET的热稳定外围技术平台,该平台集成了针对DRAM优化的模块。业界已向其下一代DRAM产品提出了多种具有不同性能成本权衡的方案。

热稳定的先栅极和后栅极FinFET集成流程

2021年,imec首次实验性地演示了一种基于优化后的先栅极工艺、用于实现高k/金属栅极叠层的热鲁棒性FinFET集成流程。与传统的先栅极方法相比,改进的流程为nMOS和pMOS实现了具有相同厚度和相同功函数金属的栅极叠层。然后将所谓的Vth移位材料扩散到高k电介质中,以调整nMOS和pMOS器件的有效功函数。

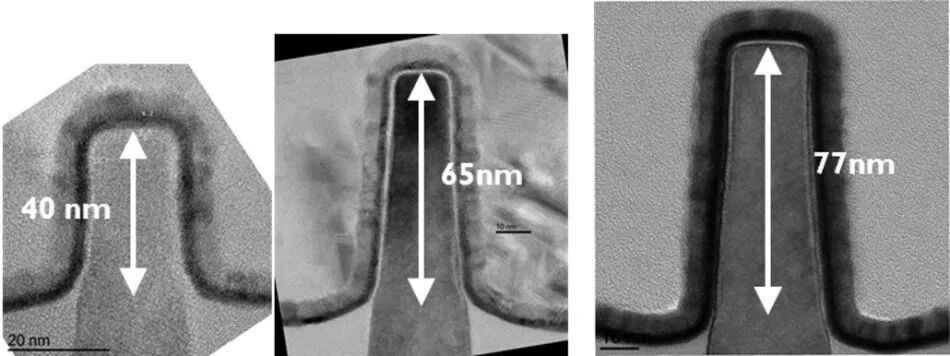

这种改进的先栅极方法降低了栅极不对称性,并提高了流程的热稳定性。通过采用该流程,研究人员展示了比平面高k/金属栅极方法更高的Ion/Ioff和短沟道控制。这些指标在经历DRAM专用退火后未出现退化。此外,还开发了更高鳍片(高度高达80nm)的版本,并改善了阈值电压失配和面积增益。

图2:高k/金属栅极FinFET鳍片制备示例的透射电子显微镜(TEM)横截面图像,显示鳍片高度分别为40nm、65nm和约80nm。(来源:imec)

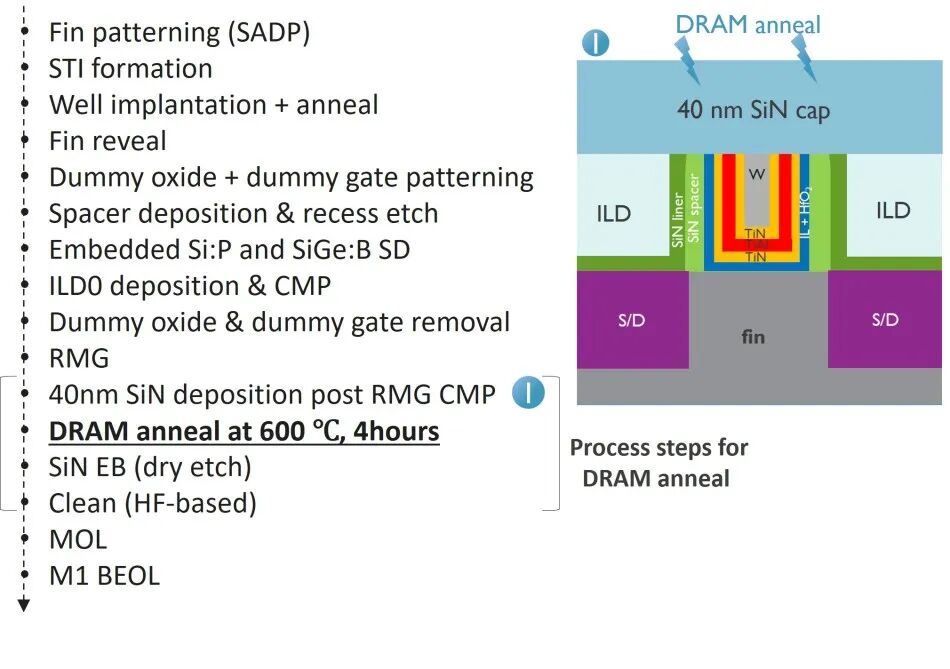

先栅极集成方法的一个缺点是阈值电压相对较高,这源于结激活期间高温退火对栅极叠层的影响。这个问题可以通过后栅极(或RMG)集成方法解决,但这种方法需要额外的工艺步骤。在2022年的IEDM展会上,imec展示了一种热稳定的FinFET后栅极工艺流程。

图3:针对热稳定FinFET提出的后栅极工艺流程的相关工艺步骤示意图。(来源:10.1109/IEDM45625.2022.10019422)

采用钼(Mo)基功函数金属、面向pMOS的优化型热稳定后栅极FinFET工艺流程

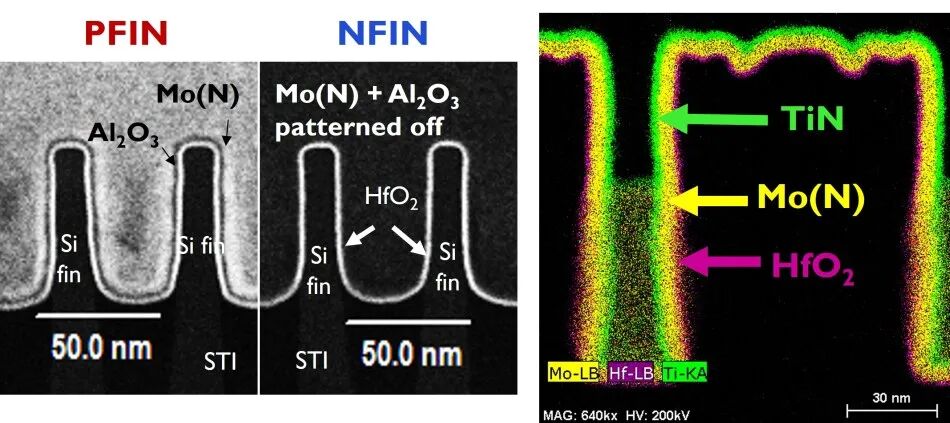

典型的后栅极工艺流程会使用不同的功函数金属制造nMOS和pMOS器件。在2024年的VLSI大会上,imec展示了在pMOS器件中采用新型Mo基功函数金属替代传统TiN基方法所带来的性能优势。新的栅极堆叠模块已成功集成到后栅极FinFET工艺流程中,并被证明具有良好的热稳定性。

集成Mo基p功函数金属的DRAM兼容工艺流程,为pMOS器件提供了足够低的Ioff电流和低阈值电压(0.12V)。FinFET还以热稳定的平面高k/金属栅极为参考进行了基准测试,结果表明,在相同的Si占位面积下,Ion(在目标Ioff条件下)提高了三倍。这些结果使热稳定的后栅极FinFET工艺流程成为10nm以下DRAM外围逻辑器件的有力候选方案。

图4:左侧和中间是环形振荡器上鳍片的TEM图像,右侧是栅极元素映射图(EDS),显示了CMOS图案化和Mo基p功函数金属叠层良好的共形性。(来源:VLSI 2024)

热稳定性铌(Nb)基金属触点,具有低接触电阻

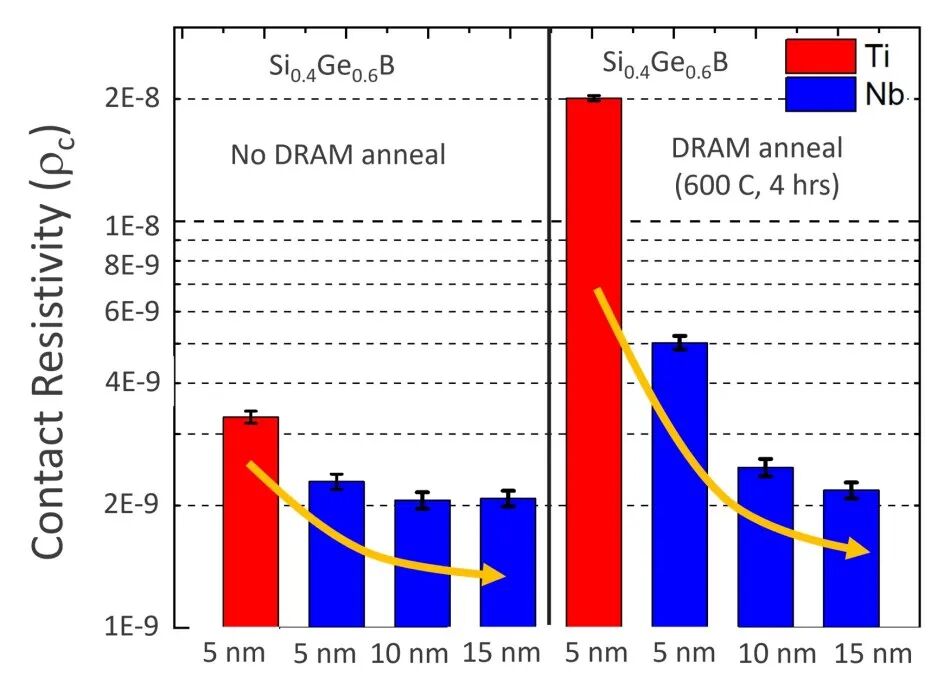

在早期基于平面高k/金属栅极的外围晶体管研究中,imec的研究人员通过改善掺杂分布和添加预非晶化注入来降低源漏接触电阻。在2024年的IEDM上,imec推出了一种不同的方法:用Nb取代pMOS器件中传统的钛(Ti)接触金属。

Nb基接触模块的热稳定性首次得到验证。此外,将其集成到后栅极FinFET平台时还观察到了卓越的性能:创纪录的低接触电阻、更低的总寄生电阻以及更大的Ion。

图5:Ti基和Nb基接触模块(不同厚度)在DRAM退火前后的接触电阻率的对比。(来源:IEDM 2024)

领先DRAM量产

在业界量产十年前,Imec便率先开发出了外围晶体管技术。在其最新的研发成果中,Imec展示了一个面向产业需求、具备热稳定性的FinFET平台,以满足10nm以下DRAM的要求。目前,imec已开发出多种技术方案,作为下一代DRAM产品的潜在候选方案,分别提供不同级别的制造复杂度与晶体管性能。

长远来看,为了延续DRAM的微缩路径,Imec设想了更具颠覆性的概念。其中之一就是在单独的晶圆上构建外围电路,并使用先进的晶圆键合技术将其与存储器阵列集成。虽然这种方法需要额外的工艺步骤,但其真正的优势在于降低了对热稳定性的要求,因为外围电路现在可以与存储器阵列分开制造。

近期,imec已启动针对这一新型DRAM架构的外围晶体管研发工作,其研究方向基于对平面晶体管和FinFET技术的深入理解。

作者:Imec公司技术客户总监Alessio Spessot和CMOS器件技术总监Naoto Horiguchi

THE END

2025-08-24

2025-08-24

2025-08-23

2025-08-23

2025-08-22