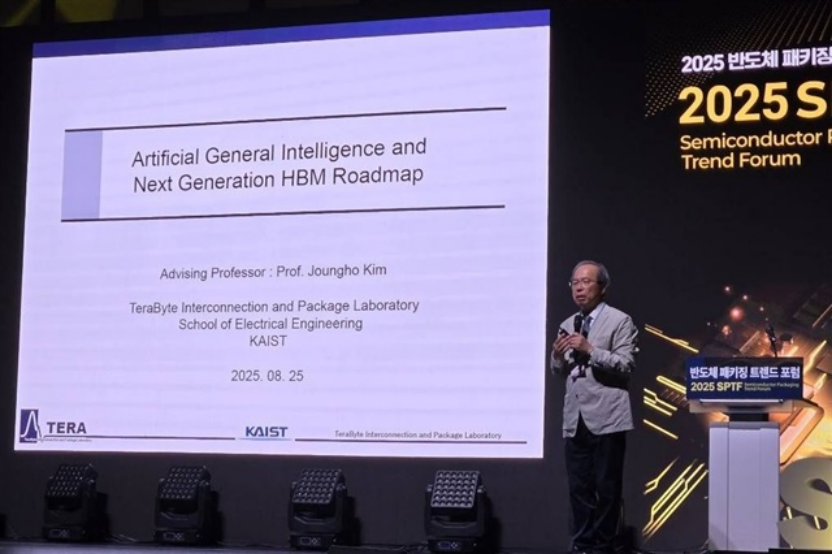

Joungho Kim概述 HBM 技术未来发展方向。图片来源:Daniel Chiang

随着人工智能与高性能计算的快速发展,与 GPU 搭配的高带宽内存(HBM)已成为半导体行业的关键竞争领域。韩国科学技术院(KAIST)电气工程学教授、被誉为韩国 “海力士 HBM 之父” 的Joungho Kim强调,混合键合、高带宽闪存(HBF)及内存内计算等新兴技术,将对未来内存设计起到决定性作用。

在半导体封装趋势论坛上,Joungho Kim预测,智能体 AI(agentic AI)时代的数据处理需求可能较当前增长 100 倍;当物理 AI 应用普及后,工作负载甚至可能激增 1000 倍,这就要求 GPU 所搭配的 HBM 容量实现同比扩张。要满足这些需求,不仅需要更高的带宽,还需增加内存垂直堆叠层数,并大幅提升硅通孔(TSV)数量。

混合键合成关键技术

未来 HBM 设计可能需要数十万甚至数百万个硅通孔。为支持如此高的密度,线路间距需大幅缩小。Joungho Kim认为,传统热压键合设备将难以跟上需求,混合键合技术因此变得不可或缺。目前键合间距仍处于数十微米级别,而下一代技术必须达到 1 微米级别。

他还解释道,仅靠垂直堆叠无法满足未来需求,HBM 还需向水平方向拓展,并与 CXL、PCIe 等新兴互连标准集成。他将这种未来架构比作高层公寓楼 —— 内存层通过垂直与横向连接,共同满足激增的带宽与容量需求。

散热、容量与新型内存挑战

针对未来 HBM 设计中的散热挑战,Joungho Kim建议,从 HBM6 开始,内存 “公寓楼” 将通过顶层类似 “天桥”(sky-bridge)的中介层连接;在中介层上方安装 GPU 计算单元,并采用外部冷却方式,以实现高效散热。

Joungho Kim补充称,仅靠 DRAM 无法满足激增的容量需求,GPU 还需 LPDDR、高带宽闪存(HBF)等其他类型内存的辅助。尤其是基于堆叠 NAND 的 HBF,可能成为 HBM6 之后的转折点 ——NAND 可将容量提升 10 至 100 倍。例如,10 片 128 层 NAND 裸片堆叠即可达到 1280 层,这一突破已引发SanDisk等企业的浓厚兴趣。

计算向内存迁移

Joungho Kim表示,仅提升带宽与容量还不够,延迟也必须降低 —— 数据从 HBM 传输至 GPU 仍需耗时。他提出的解决方案是:通过 3D 结构将两者更紧密结合,并在 HBM 内部直接嵌入部分计算能力。

这一变革将使 HBM 能够压缩数据流量、在堆叠内部修复错误,并接管部分 GPU 功能。金贞镐称,这种内存内计算(compute-in-HBM)方式将成为下一代内存发展的核心支柱。

HBM6 理论架构图。图片来源:韩国科学技术院(KAIST)

*原文标题:

South Korea’s HBM pioneer highlights hybrid bonding and compute-in-memory trends

*原文媒体:DIGITIMES Asia

芯启未来,智创生态