点击蓝字 关注我们

本文将介绍在低功耗设计早期阶段极具价值的可量化指标——时钟门控效率(Clock Gating Efficiency)。它不仅是评估RTL代码质量的关键指标,更是指导工程师进行功耗优化的重要方法。

时钟门控效率:早期功耗优化的可靠抓手

在芯片设计的RTL阶段,许多功耗相关的指标(如线网电容等)都难以精确量化。然而,时钟门控效率却是一个可量化、可追踪、且与最终功耗高度相关的少数指标之一。

芯片中连接触发器的时钟网络会持续翻转,产生大量动态功耗。时钟门控技术在时钟路径上添加一个“开关”(时钟门控单元)。当触发器的数据输入端没有变化时,这个开关会切断时钟信号,阻止其无谓翻转。而时钟网络是功耗大户,因此这也是降低功耗最有效的手段之一。

在修改RTL代码或使用优化工具后,只要时钟门控效率得到提升,那么最终测得的动态功耗值几乎必然呈现下降趋势,为工程师提供了一条明确的优化路径。

三大核心指标:直观、简单、高效

业内虽然存在多种评估方法,但以下三个指标因其直观、简单、有效而被广泛采用:

1.静态时钟门控效率 (Static Clock Gating Efficiency, SCGE)

![]()

该指标计算了设计中触发器被门控的比例,当触发器被门控的比例越高,设计中时钟翻转浪费的功耗越少,因此该指标越高越好。同时,此数据不依赖于波形或信号活动率,能够很好地反映RTL设计中触发器的门控情况。

2.动态时钟门控效率 (Dynamic Clock Gating Efficiency, DCGE)

![]()

该指标计算了时钟信号被门控的周期个数占比,当被门控的时钟周期越多,那么无效的翻转就越少,从而达到节约功耗值的目的。DCGE越高,说明在当前工作场景下,时钟门控的收益越大。

3.数据感知时钟门控效率 (Data-aware Clock Gating Efficiency, DACGE)

![]()

数据感知时钟门控效率在动态时钟门控效率的基础上,考虑了触发器D引脚的翻转周期,从而更综合的考虑了触发器输入的影响。

这三个指标并非全部,但它们是最直观、简单、有效的优化手段。每一个被门控的触发器都有各自的DCGE和DACGE,同时整个设计也有平均的SCGE、DCGE和DACGE,以供设计者更好了解每一个触发器的门控效率。DCGE和DACGE依赖于信号活动率,在不同的信号活动率具有不同的门控效率。

如何优化三大指标?

理解了指标,下一步是如何提升它们。这需要区分两种不同的工具流程:

1.逻辑综合

EDA综合工具一般可以完成基础优化,其目的是为保证优化后的电路与原始设计在逻辑上等价(LEC),在综合阶段通过解开电路中带MUX的逻辑环路,并插入门控时钟单元而达到门控的目标。

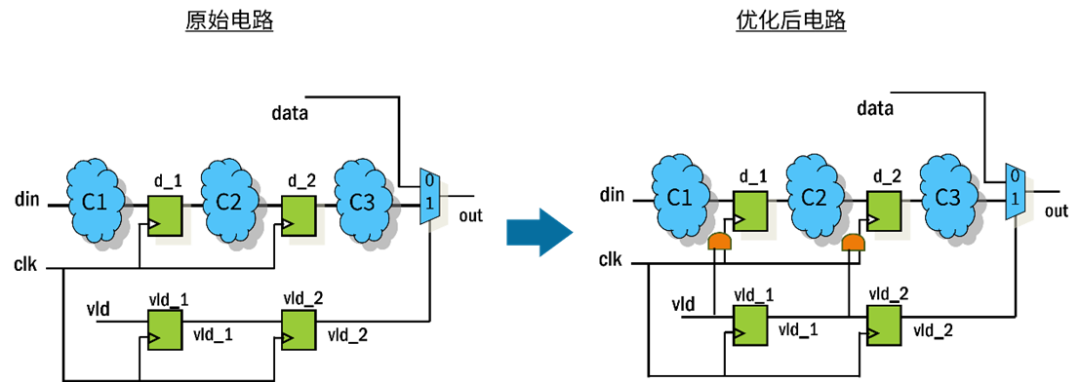

2. 进阶优化

专门的功耗优化工具可以处理综合工具不会察觉的功耗优化机会。如上图,专门的功耗优化工具通过分析电路拓扑结构,识别出当数据路径被多路选择(MUX)信号旁路时,该路径上的信号翻转是无效的,会造成功耗浪费。工具利用MUX的控制信号状态,判断并生成门控逻辑,以关闭相关路径上触发器的时钟信号,从而发现传统综合工具无法捕捉的门控机会,进一步提升时钟门控效率,实现更深层次的功耗优化。

当然,这只是众多优化方式中的一种,电路中还存在着其他丰富的优化机会等待探索。

从分析到优化: 英诺达ERPA与ERPE的协同作战

时钟门控效率不是一个新概念,但它在设计早期阶段的指导价值常常被低估。通过英诺达的ERPA(RTL级功耗分析工具)和ERPE(低功耗设计优化工具),工程师可以将这一优化流程融入到设计里:

英诺达ERPA与ERPE在RTL阶段的功耗探索流程

功耗诊断

英诺达的ERPA是用于早期功耗水平评估的EDA工具,通过自研的综合引擎,在读入RTL代码后,会自动处理时钟门控电路插入流程,提高时钟门控效率的各个指标,工程师可以查看每个触发器以及整个设计层面的指标结果,从而分析RTL代码中可以优化的点。

功耗调优

ERPE工具是功耗优化的引擎,通过更复杂的逻辑去探索电路结构,从而找到综合工具无法发现的,更深层次的门控机会。这款工具不仅可以列出所有门控的触发器信息,更会提供RTL代码修改建议,预测修改后的时钟门控效率变化,以及预测功耗的节约值。

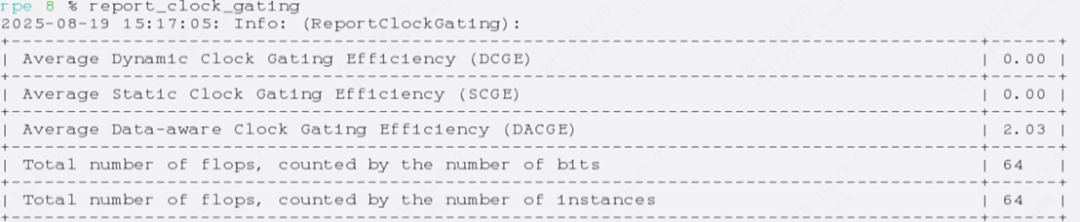

如下图,为ERPE工具优化RTL代码后的结果,综合后的触发器个数为64,且DCGE以及SCGE的值为0,表示综合过程找不到任何时钟门控的可能。但通过ERPE工具对代码优化后,将SCGE以及DCGE的结果提升到了100%,同时整体功耗下降了90.26%。

report_clock_gating打印结果

report_sequential_enable打印结果

时钟门控效率是低功耗设计早期阶段极具价值的可量化指标,掌握时钟门控效率,可以高效地降低功耗。从使用ERPA测量初始的SCGE、DCGE,到利用ERPE进行深度优化并获取具体的RTL修改建议,整个流程环环相扣,让功耗优化不再是“玄学”,而是由数据驱动的精准工程实践。

关于英诺达

英诺达(成都)电子科技有限公司是一家由行业顶尖资深人士创立的本土EDA企业,公司坚持以客户需求为导向,帮助客户实现价值最大化,为中国半导体产业提供卓越的EDA解决方案。公司的长期目标是通过EDA工具的研发和上云实践,参与国产EDA完整工具链布局并探索适合中国国情的工业软件上云的路径与模式,赋能半导体产业高质量发展。公司的主营业务包括:EDA软件研发、IC设计云解决方案以及IC设计服务。

推荐阅读

05-27

05-27

05-19