前言

当端侧 AI 应用迎来爆发式增长,从语音识别到图像分析,从智能家居到工业控制,多样化场景与有限硬件资源的矛盾日益凸显。如何在功耗、面积与算力需求间找到最优解?如何让专用处理器设计摆脱 “高门槛、长周期” 的困境?

2025年9月10日,在中国国际光电博览会(CIOE)的 “2025 年中国 RISC-V 生态大会” 分论坛上, 隼瞻科技创始人兼 CEO 曾轶先生带来了 “RISC-V 架构驱动的 AI 处理器自动化设计:领域专用场景的处理器敏捷开发方法” 主题分享,为行业痛点提供了破局思路。

当前,端侧 AI 应用场景呈现出丰富多样却又充满挑战的态势,语音识别、图像识别、视频分析、自然语言处理等各类应用场景碎片化严重,需求各不相同,同时 AI 模型种类繁多且不断演进,从 CNN、RNN、Transformer 到轻量化模型等层出不穷,架构复杂度持续攀升。更关键的是,硬件资源受限成为核心难题,功耗限制、面积约束以及对实时性的高要求,都对硬件的可编程性和扩展性提出了更高标准,而 AI 应用的多样性与对算力需求的持续增长,和端侧芯片在功耗面积上的约束形成了永恒的矛盾,在这样的背景下,计算架构需要在灵活性与高能效之间寻求平衡。

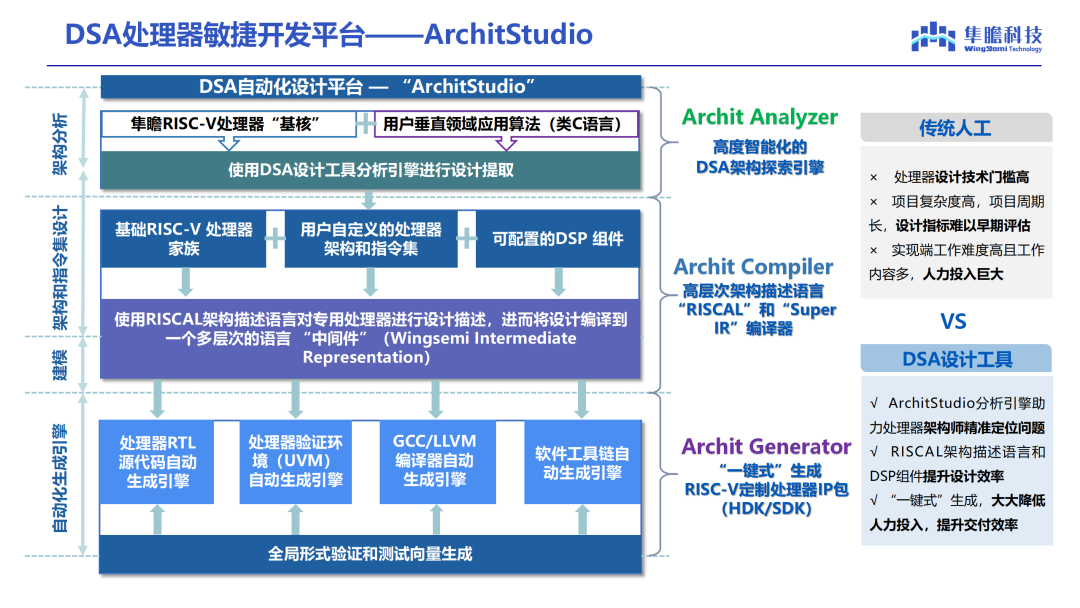

针对上述难题,隼瞻科技提出了领域专用架构(DSA)的创新解题思路,曾轶再会上强调需将需求 “左移” 与方案 “右移”—— 领域专用处理器需求方通常对垂直领域应用场景和算法有深刻认识,但缺乏处理器设计的专业知识,而处理器提供方具备完整的处理器设计能力,却往往缺乏对垂直领域的专业理解,正是为了解决这一矛盾,隼瞻科技的 ArchitStudio 处理器敏捷开发平台应运而生。

ArchitStudio是一款高效自主面向DSA设计的EDA处理器敏捷开发平台,基于算法芯片化,场景架构化的理念,加速DSA的设计和落地,为以RISC-V定制处理器为核心的SOC设计方法学带来了革命级的改变。ArchitStudio集成 Archit Analyzer、Archit Compiler、Archit Generator 等核心组件,形成 “一栈式” 智能设计模式。其能力包括:

Archit Analyzer 的多种 Profiling 工具(如 IA 仿真、CA 仿真)精准定位设计瓶颈,结合 Pipeline Stall 分析提升特定算法执行效率,且能构建多维度功耗预测模型,优化能效比达 15%-30%

Archit Compiler 采用自研 RISCAL 语言和深度强化学习(DRL)算法,探索处理器微架构参数的高维设计空间,寻求性能、面积、功耗的 PPA 最优解

Archit Generator 的 “一键式” 生成引擎可自动生成 RTL 源代码、验证环境(UVM)、GCC/LLVM 编译器、软件工具链(SDK)等,将传统需数月甚至数年的开发周期缩短至数周,大幅提升交付效率

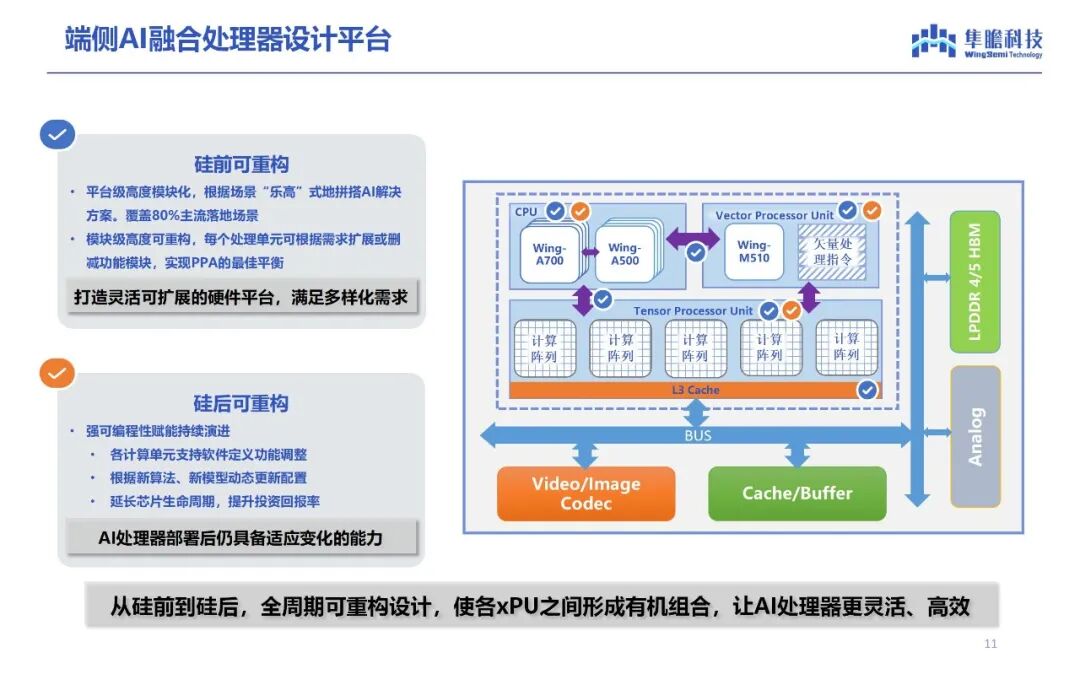

以端侧 AI 融合处理器设计平台为例,该平台在硅前具备高度模块化特点,可根据场景像搭乐高一样拼搭 AI 解决方案,覆盖 80% 主流落地场景,模块级高度可重构,每个处理单元能根据需求扩展或删减功能模块,实现 PPA 的最佳平衡,打造出灵活可扩展的硬件平台,满足多样化需求;在硅后,其强可编程性赋能持续演进,各计算单元支持软件定义功能调整,可根据新算法、新模型动态更新配置,延长芯片生命周期,提升投资回报率,从硅前到硅后,全周期可重构设计使各 xPU 之间形成有机组合,让 AI 处理器更灵活、高效。

自成立以来,隼瞻科技不仅为 AI、工业控制、汽车电子等领域提供了专用处理器解决方案,更在推动 RISC-V 生态国产化、标准化方面持续发力。未来,随着 RISC-V 架构的不断成熟与生态的持续完善,专用处理器设计将迎来更多创新可能。隼瞻科技也将继续深耕 RISC-V 领域,以技术创新推动行业发展,与更多合作伙伴携手,共同构筑 RISC-V 产业新生态,为中国处理器技术的突破贡献力量。

关于隼瞻科技

隼瞻科技是一家聚焦DSA处理器设计创新的高科技企业,致力于打造基于 DSA(专用指令集架构)的RISC-V技术体系。公司依托三大核心技术板块 —— 自主研发的RISC-V处理器核、高效敏捷的DSA处理器敏捷开发平台,以及可灵活定制适配多元模型的NPU模块,构建起高度模块化的解决方案体系。通过自由组合的产品架构,精准响应AIOT、DSP、5G 网络、汽车电子、人工智能等复杂芯片场景的差异化需求,为行业提供兼具性能与灵活性的解决方案。