之前文章介绍过SURF开源库,今天我们就展开讲讲SURF,重点介绍能为我们带来哪些便利。

SURF(SLAC Ultimate RTL Framework) 是斯坦福线性加速器中心(SLAC National Accelerator Laboratory)开源的大型 VHDL 库与 FPGA/ASIC 通用设计框架,它为复杂数字系统开发提供了丰富的基础 IP 模块。该项目由 SLAC 的 TID-ID 电子系统部门维护,适用于 Xilinx、Intel FPGA 以及 ASIC 的数字逻辑设计。

📌 什么是 SURF?

SURF 是一个用 VHDL 实现的 IP 库和设计框架,包含大量常见模块,可直接用于 FPGA 或 ASIC 设计中,目标是让硬件开发者能够快速构建可靠的系统。该库包含:

-

以太网协议栈 IP:支持 IPv4, ARP, DHCP, ICMP, UDP 等协议

-

AXI4 / AXI4-Lite / AXI4-Stream 基础设施:包括 crossbar、DMA 引擎、FIFO、桥接等

-

设备驱动与外围接口库:支持 ADC, DAC, I2C, SPI, UART 等常见设备

-

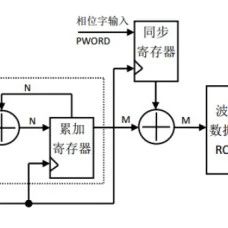

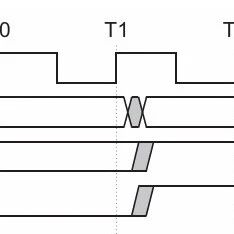

同步库:跨时钟域同步解决方案

-

包装好的 FPGA 厂商模块:如时钟管理、DNA 读取、IPROG 等

-

SLAC 特定协议支持:如 CoaXPress 等协议支持

总之,SURF 是一个可复用的 RTL IP 集合与通用逻辑框架,可极大缩短 FPGA/ASIC 的开发周期。

🔧 适用范围

SURF 不仅仅是头文件的集合,它是一个系统级库,适合以下场景:

✅ 通用 FPGA 设计加速

将常见协议、总线与硬件结构封装成 IP,可直接在工程中复用,而不必从零开始设计。

✅ ASIC/数字芯片设计

由于 SURF 完全采用 VHDL 编写,它也适用于 ASIC 设计流程,方便在硅实现前做一致性测试与验证。

✅ 高速网络与数据采集系统

拥有完整的 UDP/IP 以太网库及 DMA 结构,适用于数据流密集、需要高带宽的系统,如科学仪器、DAQ 等。

🔍 库结构与内容

SURF 的代码组织结构非常清晰,各类基础组件均有对应目录:

📦 Ethernet Library

提供链路层以上完整的 IP 栈模块:MAC、帧解析、UDP/IP 支持等。

📦 AXI 系列库

支持不同 AXI 协议族,包括

AXI4:主从接口、DMA、FIFO 等

AXI4-Lite:轻量控制总线

AXI4-Stream:高带宽数据流管线

📦 Serial Protocols

包含 I2C、SPI、UART、线码以及 JESD204B 等常见串行通信协议的 VHDL 实现。

📦 设备库

提供对常见器件的接口/控制逻辑,如 ADC、存储器与时钟设备驱动。

📦 Board/Vendor Support

包括厂商特性挂钩与 FPGA 专用约束集成内容,可直接部署到特定板卡。

关于其他文件,大家自行探索~

🛠 构建与验证支持

SURF 并非只有 RTL 源码,还配合了丰富的构建与自动化测试支持:

Makefile 与 Ruckus 支持:SURF 使用 Makefile 与 SLAC 自研的 Ruckus 构建系统进行源管理、编译、测试与文档生成,一体化提升开发效率。

GHDL + cocotb 验证:使用 GHDL 做逻辑仿真,配合 cocotb 进行基于 Python 的测试,使得开发验证更现代化。

CI/CD 集成:通过 GitHub Actions 自动运行语法检查、回归测试、文档生成等流水线,为代码质量保驾护航。

这种现代工程实践大大提升了团队协作质量,并让开源社区用户更容易参与贡献。

开源链接

https://github.com/slaclab/surf

🧠 结语

如果你正在进行复杂 FPGA/ASIC 的数字设计开发,并希望提高效率、降低重复设计成本,SURF 是一套成熟、可复用、工程级的基础架构库。无论是协议栈、AXI 总线、同步机制还是高速数据流处理,它都能为你的项目提供坚实的基础。

SURF 结合了多年科研与工程经验,是 FPGA/ASIC 开发者不可多得的开源资源。