近日,中国科学院软件研究所智能软件研究中心工程师阎明铸当选 Sail RISC-V Model 项目协作者(Collaborator)。Sail RISC-V Model是RISC-V国际基金会(RVI)唯一的RISC-V认证标准模型,Collaborator则是该项目PR的审核者。作为此项目唯一一位来自中国的Collaborator,阎明铸的入选,源于其团队长期以来对RISC-V形式化验证研究的深耕与高质量社区贡献,这不仅是对其个人技术能力与专业素养的认可,更体现了中国科学院软件研究所在RISC-V形式化验证领域的国际影响力。

作为 RISC-V 生态的核心基础设施,Sail RISC-V Model 的权威性与实用性贯穿芯片设计、合规验证、生态共建全流程,其价值在产业落地中愈发凸显。RVI采用“会员驱动”运作模式,多数RISC-V项目由会员单位人员共同主导项目开发,RVI则多以项目管理与市场营销工作为主。在此开发模式下,RVI 只为三个核心项目直接配备全职工程师深耕研发,其中指令集手册用于维护统一的RISC-V指令集架构规范,Sail RISC-V Model和RISC-V Architecture Test用于验证RISC-V芯片是否符合规范。

RISC-V Instruction Set Manual (指令集手册) RVI 全职工程师 2 人

Sail RISC-V Model (形式化模型) RVI 全职工程师 2 人

RISC-V Architecture Test (ACT,架构合规测试) RVI 全职工程师 1 人

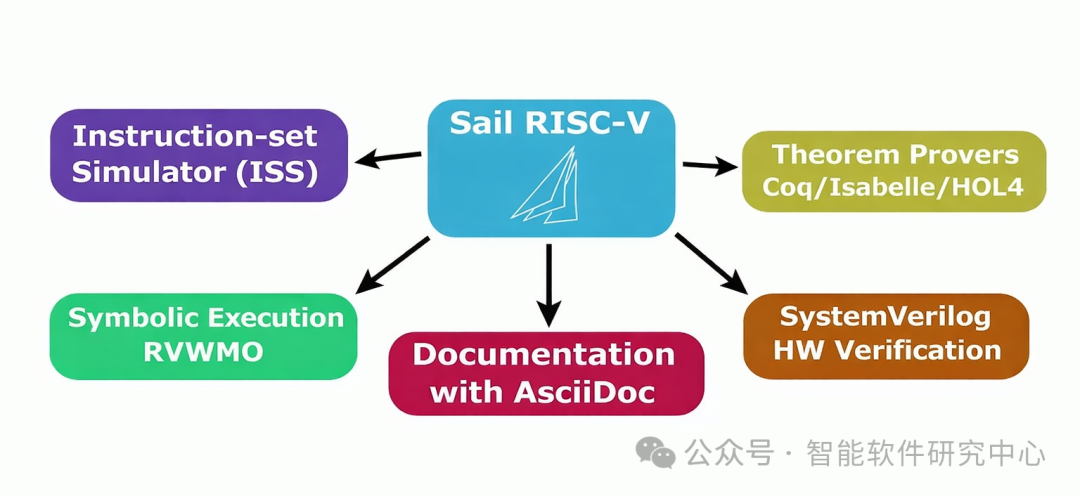

Sail RISC-V Model 是RVI推出的RISC-V指令集架构(ISA)形式化规范。项目汇聚了来自剑桥大学、RVI 工程师、中国科学院软件研究所、Codasip / SCI、Harvey Mudd College等团队的全球行业精英进行协同开发。Sail RISC-V Model采用专为描述指令集语义而设计的Sail语言编写,完整界定了RISC-V指令的汇编格式、编码解码规则及执行语义,为架构实现提供了精准统一的代码级参照。

为确保代码准确性,Sail RISC-V Model项目采用严格的协作者(Collaborator)管理机制,确保代码质量与架构一致性。所有贡献者(含核心贡献者)均无直接推送代码权限,代码合并需同时满足两项硬性要求,即至少获得 2 名 Collaborator 的Approve以及在公示期内无人提出反对意见。Collaborator 作为项目代码质量与架构规范的核心把关者, 具有代码合并的审核投票权,保障了项目代码质量的稳定性与整体架构的一致性。

阎明铸正式受邀成为Collaborator

作为RVI重点投入全职研发力量的三大核心项目之一,Sail RISC-V Model凭借严谨的形式化定义,正在成为整个RISC-V生态中不可或缺的核心基础设施以及行业公认的权威测试验证工具(如RVI RISC-V 芯片 RVA23 唯一认证工具),其价值贯穿芯片设计、合规认证全流程,为生态标准化提供了关键支撑。

对于硬件厂商, Sail RISC-V Model既为芯片设计提供精准的指令集语义代码级实现,可作为硬件厂商的标准化参考蓝本以规避自研偏差,又是RISC-V架构的“黄金模型”,其权威性高于Spike模拟器及厂商自研模拟器,是官方架构合规测试(ACT)的核心依据,芯片未通过基于该模型的合规认证将影响产品市场适配性。

对于 RISC-V 生态, Sail RISC-V Model同样能从多角度提供支撑。在指令集迭代方面,所有RISC-V扩展草案在提交公开审查前,均需提供对应的Sail伪代码实现,这已成为指令集规范落地的前置核心环节之一。从规范基础软件栈角度来看,Sail RISC-V Model为编译器、模拟器、操作系统内核及各类芯片设计提供统一的代码级参照准则,保障生态组件间的兼容性。此外,凭借严谨的形式化验证能力与灵活的可配置性,Sail RISC-V Model可满足不同类型、不同场景下RISC-V设备的验证需求,提升芯片可靠性从而赋能芯片验证。对于开发者来说,Sail代码正逐步融入RISC-V官方指令集手册,已成为全球RISC-V开发者理解架构语义、开展技术研发的必备参考材料。

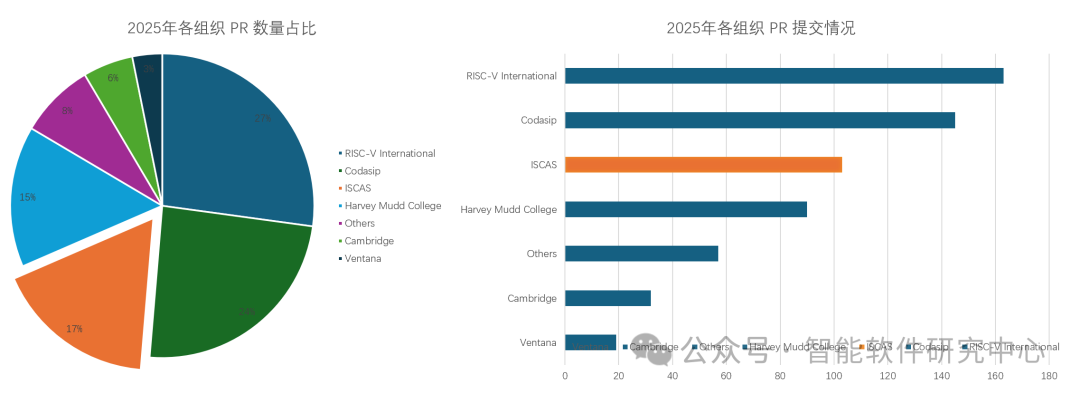

团队(图中标注为ISCAS)以技术为主线,积极投身 Sail RISC-V Model 项目社区建设,深度参与功能支持、缺陷修复及性能改进等全维度工作,覆盖功能优化、扩展适配、文档完善等关键领域,以扎实稳定的技术输出赢得了国际社区广泛认可。2025年团队在扩展指令集实现领域提交了 17 个RISC-V扩展的Sail RISC-V Model实现、提交数量位居全球第二,仅次于RVI官方团队。

2025年团队(图中标注为ISCAS)提交PR 117 个,排名全球第三,涵盖项目重构、缺陷修复、回调接口支持等各类场景,全方位彰显了团队在该领域的综合研发实力与全球领先地位。

当前,Sail RISC-V Model 已构建起完备的配置系统,能够精准适配RISC-V架构的多样特性需求,全面覆盖不同厂商的多样化实现场景。全球范围内,Rivos、Ventana、Andes、Qualcomm等知名企业及学术机构均积极参与项目贡献,并且已经有多款主流芯片产品, 包括玄铁C908/C910、进迭时空X60/X100、StarFive JH7110/Dubhe-90等,均依托该模型开展合规性验证工作,充分印证了其核心产业价值。团队将以此次当选为契机,持续深耕 Sail RISC-V Model 领域,聚焦三大方向精准发力:

全力适配 RVA23 标准,助力RVI芯片认证计划顺利落地

扩展技术边界,探索模拟器外设支持、性能优化、多核适配等关键技术,覆盖更多复杂芯片验证场景;

深化国际社区协作,积极参与架构标准研讨,持续输出高质量技术贡献,巩固全球领先的贡献地位。

未来,团队将以开发者和审核者的身份充分发挥桥梁纽带作用,推动国内厂商需求与国际社区研发高效衔接,助力我国RISC-V芯片企业提升合规认证效率、降低研发成本,为产业高质量发展提供核心技术支撑。