摘要

-

I/O架构必须从第一天就与计算机共同设计。 -

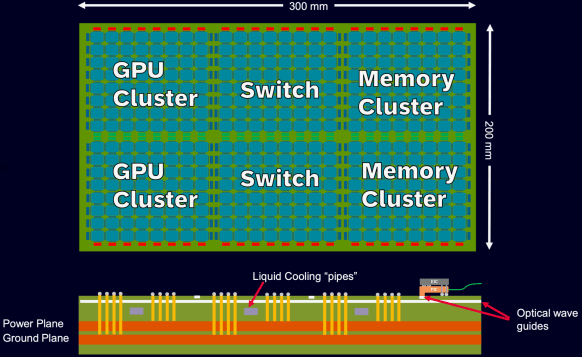

将SoC划分为异构小芯片(计算、EIC、PIC、激光器)直接影响功率传输、楼层规划、互连拓扑和系统可扩展性。 -

成功的CPO设计需要架构师从多物理学角度思考,在封装/系统层面平衡电信号、热稳定性、光学行为和机械约束。

人工智能数据中心正开始用共封装的光学器件取代铜材料,以期降低每比特的能耗并提升带宽。

使用CPO的优点在于,它将光连接的位置更靠近ASIC、GPU或CPU,减少了对长且低效的电痕迹的需求。虽然其本身功率并不低,但CPO提供了极低的每传输比特的能耗——这是衡量数据中心效率的关键指标。

CPO 不使用传统的远程可插拔收发器,而是将光子引擎直接集成到同一个封装基板或同一个模块内,使电信号在多模组装中只能传输几毫米,而不是通常从芯片到前板的PCB上传输15到30厘米。

这是 AI 领域的一块重要拼图。根据麦肯锡公司的数据,到 2030 年,满足全球 AI 需求将需要 5.2 万亿美元的数据中心投资。因此,解决电力和带宽挑战对于确保超大规模企业实现最佳投资回报至关重要。在 CPO 采用方面处于领先地位的是博通、英伟达、英特尔、Marvell 和 Ayar Labs,它们拥有各种技术和产品,这些技术和产品由 GlobalFoundries、IBM、英特尔晶圆厂、Tower Semi 和台积电等晶圆厂提供支持。EDA 工具供应商 Cadence、Keysight EDA、西门子 EDA 和 Synopsys 也推出了 CPO 工具。

“超大规模企业正在引领我们所看到的变革,”托尼·马斯楚安尼(Tony Mastroianni)观察道,他是 西门子EDA 的3D IC解决方案工程高级总监。“异构集成使我们能够超越摩尔定律的限制。虽然我们已经使用硅插片十多年了,但它们的尺寸是有限的。然而,新的有机和玻璃中间体正在出现,使全面板大小的基板能够容纳大量的硅,甚至可以容纳一米一米。对人工智能的需求加剧了对于性能的要求,而效率往往被置于次要位置。现在要实现这样的性能需要巨大的电力,相当于核反应堆,这使得能源消耗成为一个关键挑战。I/O带宽是另一个主要问题,而这些正是CPO有效解决的问题。"

其他人也同意。“共同封装的光学器件因其高带宽和低比特功耗而被选择,尽管它们并不一定是整体低功耗技术,激光器具有硬件效率,但环形谐振器需要通过小加热器不断加热,以保持光子IC的温度。虽然总功率并不低,但每比特的能量(以皮焦耳计)很高,这使得在考虑带宽时效率很高。”马克·斯温宁(Marc Swinnen)说。

图1:模拟环形共振器。来源:Synopsys

CPO的基本原理

对于芯片架构师和工程师来说,CPO有很多方面。

“任何关注系统架构——整个系统——在数据传输过程中的情况的人,都需要根据其他重要考量因素来考虑自己将使用何种技术,例如,每焦耳所包含的比特数就反映了你为生成一个比特的数据传输所消耗的能量量。人工智能数据中心对电力需求巨大,因此降低能耗极具挑战性,因为你需要消耗大量的电流。对于为人工智能数据中心设计计算节点的客户而言,一块仅两英寸见方的芯片就可能消耗近 35,000 安培的电量。考虑到这样的电压水平,其电力消耗量是巨大的——每块芯片最高可达 35 千瓦。在先进封装设计(包括但不限于 CPO)领域,管理如此规模的电力是一项重大挑战。考虑到可能存在的数百万块此类芯片,支撑它们的能源需求可能需建设专门的发电厂,因为现有的解决方案已显不足。” Keysight EDA 高速数字设计部门负责人李熙秀指出。

DSP芯片是系统中功率消耗量最大的组件之一,因此设计人员往往力求尽量减少其使用量。李表示:“这一转变正促使人们探索 CPO 技术,该技术可实现对光学的直接转换,而无需依赖传统的 DSP 或 ASIC,从而提升了效率,从系统架构师的视角来看,这带来了诸多挑战,因为芯片设计如今必须同时考虑电气和光学因素。人们对 EO、OE 和 eOe 系统(即电气与光学信号之间的转换)的兴趣日益浓厚。归根结底,这些发展是由 AI 数据中心对能源的无限需求所驱动的,使得向更高效解决方案的过渡显得情有可原。”

与此同时,对于在EIC和PIC之间驱动信号所需的功率也存在一些担忧。Synopsys的首席产品经理朗·林指出:“这些系统需要专门的电压控制电路来驱动电流进入环,从而产生热量。这个过程本质上涉及施加功率以引起温度变化,这可能需要显著的能量。每个环可能消耗大约一到十毫瓦的功率。虽然目前的系统可能使用大约64个环,但有报告——例如来自DARPA项目——讨论在未来设计中整合数千个环。将光子电路扩展到这种程度将接近目前晶体管数量的水平,可能达到数百甚至数千个环。”

为这些环供电成为一个重大挑战。“例如,以每根1毫瓦的功率为1000个环供电,总共需要大约1瓦,”林说。“额外的电路,如带有众多放大器的电子集成电路,进一步增加了功耗,支持的组件如GPU和CPU,其功耗需求仍然很大。由于数据传输速率高,I/O功耗也很大,可能占总功耗的50%或更多。随着系统的不断扩展,确保足够的功率传输仍然是一个关键问题。”

与互连铜基相比,尺寸要小得多,但电力传输仍然是一个挑战。“传统上,电压调节器被放置在封装或PCB上,但现在通常将其集成到模具上,作为集成电压调节器(IVR)。对于具有不同电压的各种电力领域,如电路、光子学和电气元件,可能需要多个IVR。因此,这种复杂的系统在电力传输方面带来了显著的挑战,”林说。

CPO力学

CPO方法使用两个芯片——一个位于底部并直接安装在衬底上的光子设备,顶部堆叠一个小型SerDes,形成一个3D小芯片配置。

西门子的马斯楚安尼说:“这种组件物理上连接到一个插入器,插入器可以是硅的,但由于布线要求增加,通常用于更大的衬底,因此光纤直接连接到封装内的光子设备,代表了CPO的本质。通过以这种方式集成光纤,有效解决了功率问题,使SerDes能够高效地与小芯片通信。虽然将SerDes放置在底部似乎合乎逻辑,因为它与小芯片进行通信,但机械约束要求光子位于衬底上。位于上面的SerDes使用TSVs通过光子设备传输信号,促进了在衬底上的通信,类似于硅插入器。替代的插入器如有机桥或玻璃也提供了有趣的可能性。”

图2:多模组组合中光波导的位置。来源:西门子EDA/Chiplet Summit

虽然CPO设计显著降低了芯片上的I/O功率,但晶体管处理功率保持不变。他说:“以前的解决方案如HBM已经解决了存储器功率I/O问题,而CPO现在解决了与I/O相关的功率和带宽挑战。数据通过多个通道(通常在光纤内8到16个通道)流出芯片,以低功耗提供出色的带宽。需要一个激光源,目前正在进行的研究旨在将其集成到芯片本身上。此外,CPO通过消除对多个封装引脚的需求,缓解了传统的SerDes拥塞,从而释放了包括后端传输在内的功率传输障碍。虽然这种解决方案并不普遍适用,但代表了显著的进步,特别是对于构建巨型芯片的超大规模制造商来说。”

CPO设计的挑战

CPO超越了传统的纯电气的边界,直接将光学组件与高性能ASIC、CPU或GPU集成。这反过来需要一种专门的光电子设计方法来管理光和电在单一封装中的物理和功能融合。

对于芯片架构师和设计师来说,在以下几个方面必须提升技能:

- 异构小芯片集成。设计人员需要使用基于小芯片的架构来创建用于计算、存储和光子学的小型专用模具。先进的封装技术,如台积电的COUPE或英特尔的Foveros,将用于在一个系统中互连这些不同的材料。

- 消除信号瓶颈。由于光子引擎直接放置在ASIC旁边,因此消除了长损耗的铜迹,这可以节省高达30%的系统功耗。

- 热光联合设计。光子元件对温度非常敏感,因此设计团队必须进行复杂的多物理模拟,以管理高瓦数计算芯片的热流,使其不会在光学中引起波长漂移或对准误差。

- 硅光子学的发展。设计人员需要创建光子集成电路(PICs),使用标准的CMOS制造技术将调制器、探测器和波导集成到硅衬底上。

- 激光源管理。架构师和设计师必须决定是将激光直接集成在芯片上还是将其保持在外部。设计人员可以选择冗余激光设计或集成监测,以确保可靠性,因为激光器通常是堆栈中最不可靠的组件。

CPO的挑战与进展

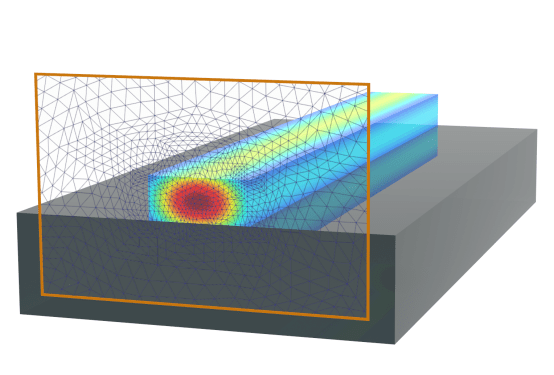

CPO增加了一系列多物理挑战。光子学信号可能会因温度变化而漂移,材料可能会直接影响光传播。波导可能会有大致相当于电子信号线边粗糙度的不规则性。所有这些都需要与系统设计的其他部分一起解决,而不是孤立解决。

图3:模拟光波导。来源:Synopsys

“我们需要所有工具协同工作,使用热应力翘曲剖面并将它们应用于光电路性能仿真,以前,这完全依赖于经验数据,但现在我们的仿真直接与实际系统测量挂钩。”Synopsys的林说。

这种集成是必要的,因为在模拟中,区分麻烦的影响和可以忽略的影响是很重要的。有时被忽略的影响比预期的影响更大,应该包含在建模过程中。

这正是大型EDA公司将注意力转向的地方。发展情况包括:

-

Cadence 正在与光子超级计算机开发商 Lightmatter 合作开发 CPO 解决方案,将 Cadence 的高速 SerDes IP 与 Lightmatter 的光学引擎集成在一起。这些公司正致力于与先进节点 CMOS 技术及标准封装工作流程的整合,旨在为下一代人工智能和 HPC 环境中高性能、可投入生产的 CPO 铺平道路。Cadence 还与 Tower Semiconductor 合作创建了一种异质集成流程,该流程支持使用 Tower 技术的 PIC/EIC 子系统的芯片到晶圆和晶圆到晶圆应用。 -

Keysight EDA于2025年10月完成了对Synopsys光学解决方案集团的收购,将先进的光学仿真工具集成到Keysight现有的EDA工具中。随后,Keysight EDA发布了用于小芯片和3D-IC设计的软件工具,用于仿真和验证共封装的光子学和电子学。 -

西门子EDA最近收购了Canopus AI,以将其基于人工智能的计量和检测功能整合到其EDA产品组合中,这直接影响到CPO制造,通过提高复杂光子集成电路的精度和产量来改善CPO的制造。1月,西门子扩大了与英伟达的合作,在其EDA工具中整合GPU加速技术,特别针对CPO所需的高密度互连的验证和布局优化。 -

Synopsys正在与Lightmatter合作,两家公司正在努力优化电光接口。Synopsys继续与台积电合作,并扩展了与英伟达的合作,以加速使用英伟达GPU加速计算的光学仿真和工程工作流程。

CPO的下一步工作

为了使CPO更加主流化,需要解决一些先进的包装问题。

“CPO 相较于传统封装方法,提供了更高的带宽密度、更低的功耗和更短的延迟时间,这对于下一代 AI 解决方案至关重要,”Presto 的 Pugo 指出。“2.5D 封装是 CPO 的基础,它能够使光子 IC 和电子 IC 与 GPU 或 ASIC 相结合。主要挑战包括 GPU/ASIC 附近的散热问题(如液体冷却冷板、微流体、微通道散热器等先进散热管理技术)、实现更高精度的光学耦合、提高激光可靠性、提高制造良率以及降低制造成本。其他挑战包括推动 CPO 模块外形规格的标准化、提高测试和验证的自动化程度,以及确保光学引擎(OE)在故障情况下的可维护性。解决这些挑战将有助于 CPO 在整个行业的更广泛应用。”

然后,从物理学的角度来看,检查包装揭示了一个复杂的信息流。“数据通过光纤电缆到达,光纤电缆连接到一个微透镜,将光聚焦到一个带有光栅的光子集成电路(PIC)上,光栅将入射光转换为电信号,然后PIC对这些信号进行初步处理。在这个阶段,PIC与EIC协同工作。微透镜将光引导到PIC,在那里进行处理、转换为电能,然后传输到EIC进行进一步的电子处理。这个接口随后连接到外部系统,完成信息路径。”Synopsys的Swinnen说。

光子IC中波导的折射率对温度高度敏感,这影响了性能。“为了管理这一点,系统被加热到稳定的高温——大约100度——因此微小的热波动可以忽略不计。内置加热器以保持这种稳定性,但热量仍然通过电子IC散发,因此热管理至关重要,”斯温宁说。

系统集成也受到影响,因为由光链构成的光子电路对温度变化高度敏感。因此,有必要设计一个多模CPO,以确保所有元件在其适当的温度范围内工作,而不会过度耦合。

结论

对于非常大型的 AI 巨型芯片而言,功率和带宽(而非计算能力)如今已成为制约因素。传统的高速电气 SerDes 技术因数据必须离开封装并跨越电路板而极其耗电。CPO 直接通过在内置封装中用光学路径取代长距离电气路径的方式解决了这一问题。这样一来,光子器件可与计算硅芯片集成在一起,使得数据几乎可以立即以光学方式离开芯片,从而大幅降低了 I/O 能耗,同时提供了巨大的带宽。与此同时,这还能通过消除大量高速电气 I/O 引脚、减少拥堵、使更多空间可用于电源传输以及支持先进技术(如背面电源传输)等方式,释放封装资源。

此外,还存在热学和机械方面的挑战,但这些挑战是可控的。尽管光子器件对温度和潜在的应力较为敏感,但问题并不在于原始的热量产生,而是温度稳定性。这些挑战可以通过设计技术加以解决,例如温度控制回路、精心的布局规划以及具备应力感知功能的封装技术,这些措施使得 CPO 成为可能。尽管 CPO 目前并非适用于所有芯片,但它对于大型、高 I/O 人工智能系统而言几乎不可或缺,因为它从根本上改变了原本难以应对的功率和带宽需求的可行性。

来源:https://semiengineering.com/cpo-is-extending-the-limits-of-whats-possible-in-ai-data-centers/,侵删