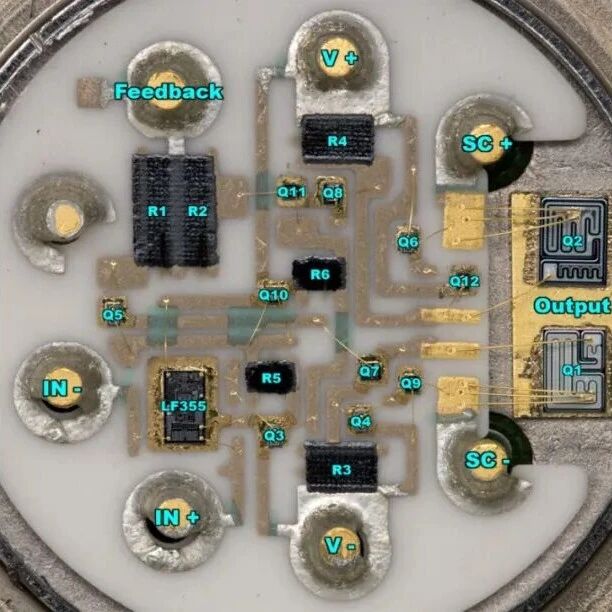

大多数运算放大器 (op amps) 都具有输入和输出静电放电 (ESD) 保护二极管,如图 1所示。这些二极管旨在防止器件测试和产品组装期间的 ESD 损坏。

ESD事件可能会将极高电流驱动到ESD二极管,但持续时间仅为纳秒。虽然ESD二极管设计用于承受ESD脉冲,但持续时间较长的电气过载事件将需要额外的外部元件。大多数输入ESD保护二极管设计为可承受10 mA的连续电流,但电气过载故障通常会导致电流远远超过10 mA的限值。

图1:运算放大器具有输入和输出ESD保护二极管。来源:德州仪器

限制运算放大器输入过载电流的一种常用方法是在每个电源上简单地添加一个输入限流电阻和一个瞬态电压抑制器 (TVS) 二极管(图 2)。电阻会限制输入电流,但部分过载电压仍会传导到电源上。TVS 二极管将保护电源免受通过 ESD 二极管传导的过载电压的影响。

您需要一个 TVS 二极管,因为许多稳压器既不具备吸收电流的能力,也无法快速响应以保护电源。保护运算放大器所需的电阻值取决于输入端过载信号的幅度。较大的过载信号需要较大的电阻。

图2中的示例使用一个10 kΩ电阻,将50 V过载信号电流限制在3.13 mA的安全水平。使用图2中的保护方案可能非常有效,但也存在一些局限性。

图2:上图所示的电气过载 (EOS) 保护方案采用了 OPA205 精密运算放大器。来源:德州仪器

由于运算放大器的输入偏置电流 (IB),电阻会引入直流失调误差。该误差会直接增加运算放大器的输入失调电压 (VOS ),从而限制电路的直流精度。电阻输入保护的另一个限制是电阻会产生热噪声。公式 1 计算噪声密度:

e nRin =√4xkxTxRin ( 1 )

然后,您应该将该噪声与运算放大器噪声谱密度规格进行比较。

在图2所示的示例中,输入噪声规格为7.2 nV/√ Hz,电阻产生12.8 nV/√ Hz的噪声。因此,总噪声将主要由保护电阻决定,并且远高于运算放大器本身的噪声。

e nTotal √(7.2 nV/√Hz) 2 + (12.8 nV/√Hz) 2 = 14.7 nV/√Hz (2)

图 3所示的结型场效应晶体管 (JFET) 输入保护方案能够实现可靠的输入保护,同时最大限度地减少 I B和电阻噪声引起的误差。当没有电流流过时,JFET 电路的电阻较低,但当有电流流过时,电阻会迅速增大。

图3: JFET输入保护电路在故障条件下的工作情况。来源:德州仪器

因此,在正常工作条件下,JFET 电路具有低电阻,并产生极小的噪声和 I B误差。在故障情况下,JFET 器件的阻抗会迅速升高,从而限制电流并保护电路。故障消除后,JFET 将恢复到正常的低阻抗状态。

您可以使用分立的JFET构建这种JFET电路,但它也集成在某些放大器中。通常,当您在放大器数据表中看到“输入过压保护”一词时,该保护是指JFET输入保护。使用集成保护可以节省PCB面积,节省设计工作量,并且通常可以降低总体成本。

JFET基础知识回顾

为了理解JFET的保护原理,我们先来回顾一下JFET的一些基础知识。本文将重点介绍P沟道JFET器件,但同样的方法也适用于极性相反的N沟道器件。您可以将JFET晶体管想象成一个压控电阻,其中沟道电阻由栅极-源极电压(V GS )和漏极-源极电压(V DS )控制。

重要的是要理解JFET工作在耗尽模式。栅极-源极结反向偏置,从而形成一个耗尽区,限制沟道电流(ID ) 。增加反向偏置电压将增大耗尽区,从而增加沟道电阻。当VGS = 0 V时,电阻最小,此时耗尽区非常小,如图4所示。

图4:电阻区与耗尽区的比较。来源:德州仪器

调整 V DS也会影响耗尽区。当 V DS较低时,沟道的作用类似于电阻,晶体管处于欧姆区或三极管区。在欧姆区,V DS的增加会导致漏极电流 (I D ) 成比例增加,就像在电阻上看到的那样(参见图 5左侧)。

当 VDS 较高时,沟道夹断,晶体管处于饱和区。在饱和区,流过晶体管的电流在很宽的漏源电压范围内保持相对恒定(见图 5 右侧)。

图5: P沟道JFET特性曲线,突出显示欧姆区和饱和区。来源:德州仪器

如前所述,对于JFET,栅极-源极结通常处于反向偏置状态。当处于正向偏置状态时,JFET将不再像晶体管一样工作,图5中的曲线也不再适用。在这种情况下,JFET将充当普通的PN结二极管,正向压降约为0.6 V,电流受外部元件限制。

一般来说,最好避免正向偏置工作模式,但在输入保护电路的情况下,当存在过应力信号时,其中一个晶体管将变为正向偏置。

JFET保护电路的工作原理

图 3 中的 JFET 输入保护电路显示了故障条件下的电路工作情况。本例将 +50 V 输入故障施加于采用 ±18 V 电源的运算放大器。晶体管 T1 充当正向偏置二极管,T2 充当处于饱和区的 JFET,V GS = 0 V。

假设保护电路中的晶体管采用图5所示的IV曲线,当V GS = 0 V且V DS > –1.5 V(饱和区)时, ID限制在约2.25 mA 。因此,JFET电路将输入电流限制在10 mA绝对最大电流规格以下,从而保护运算放大器免受损坏。V GS = 0 V时的电流定义为IDSS,因此运算放大器输入保护要求IDSS < 10 mA。

–50V 输入故障也会产生同样的效果,只是 T2 会变成正向偏置二极管,而 T1 会处于饱和区。在故障状态下,JFET 将充当限流电阻,当故障电压升高时,电阻会增大,并保持小于 10 mA 的恒定电流。

在正常工作期间,两个JFET晶体管都处于欧姆区,电阻相对较低。此外,在正常工作期间,流过JFET的电流将是运算放大器的输入偏置电流(范围通常在飞安到纳安之间)。您可以通过观察V GS = 0 V时ID曲线的斜率,以图形方式估算欧姆区电阻。

对于图5所示的晶体管,欧姆区电阻约为500 Ω (R DS = 1 V/2 mA = 500 Ω)。相反,在图3所示的故障条件下,JFET处于饱和区,其电阻约为13.7 kΩ。

重点在于,在正常工作条件下,JFET 电阻较小,因此热噪声较低(500 Ω 时)。在故障条件下,电阻较大,但在这种情况下,热噪声并不重要,因为放大器工作不正常,电阻只需保护运算放大器免受损坏。

为分立保护电路选择JFET

某些运算放大器(例如 OPA206)内置有 JFET 保护电路。如果放大器不包含 JFET,您可能需要自行构建保护电路。如果您担心热噪声或偏置电流引起的失调,则可能需要使用 JFET 保护电路。如果您不担心噪声和 I B误差,则只需使用一个较大的输入保护电阻,如图 2 所示。

假设您需要JFET输入保护,则应确认最大漏源饱和电流 (IDSS ) <10 mA,以便JFET在故障条件下充分限制输入电流。此外,由于两个JFET晶体管中的一个将具有正向偏置栅极源结,因此必须确认绝对最大正向栅极电流小于IDSS ( IGF < IDSS )。

确保漏极-栅极和源极-栅极电压不超过绝对最大值。最后,计算 V GS = 0 V 时的欧姆区电阻,以确认非故障条件下的电阻从误差角度来看是可以接受的。

成本和规格影响

为了了解集成和不集成JFET保护电路的运算放大器的额外成本和规格差异,我们来比较一下OPA205芯片和OPA206芯片。这两款器件使用完全相同的运算放大器,但OPA206集成了额外的JFET保护电路。在比较这两款器件的规格时,主要差异在于输入噪声和电气过应力规格。

OPA205 的噪声为 v n = 7.2 nV/√Hz,OPA206 的噪声为 v n = 8 nV/√Hz。噪声有所降低,但远低于大型限流电阻带来的噪声。保护电路允许 OPA206 的绝对最大额定值最高超出电源轨 40 V,而 OPA205 在没有外部保护的情况下仅允许超出电源轨 0.5 V。考虑到额外的电路,OPA206 的价格比 OPA205 高出约 0.07 美元。

要实现分立式 JFET 电路,您需要购买两个 JFET 晶体管。通常情况下,这两个器件是两个 SOT-23 封装,占用的 PCB 面积与运算放大器本身大致相同。此外,这两个器件的成本很可能超过集成解决方案中额外保护的成本。

因此,一般来说,最好在可用时选择集成选项,在没有集成解决方案可用的情况下选择分立 JFET 保护,并且从噪声角度来看简单的电阻解决方案是不可接受的。

使用集成 JFET 输入保护的运算放大器

在现代模拟系统中,运算放大器故障保护的需求已变得非常普遍。然而,这些系统通常也需要低噪声和高直流精度,而简单的电阻输入保护使得满足这一目标变得颇具挑战性。使用外部JFET保护是兼顾两者的良好方法。

然而,外部保护会增加成本和PCB面积。最佳解决方案是使用集成JFET输入保护的放大器,这样可以保护输入,保持良好的性能,并最大限度地减少成本和PCB面积。