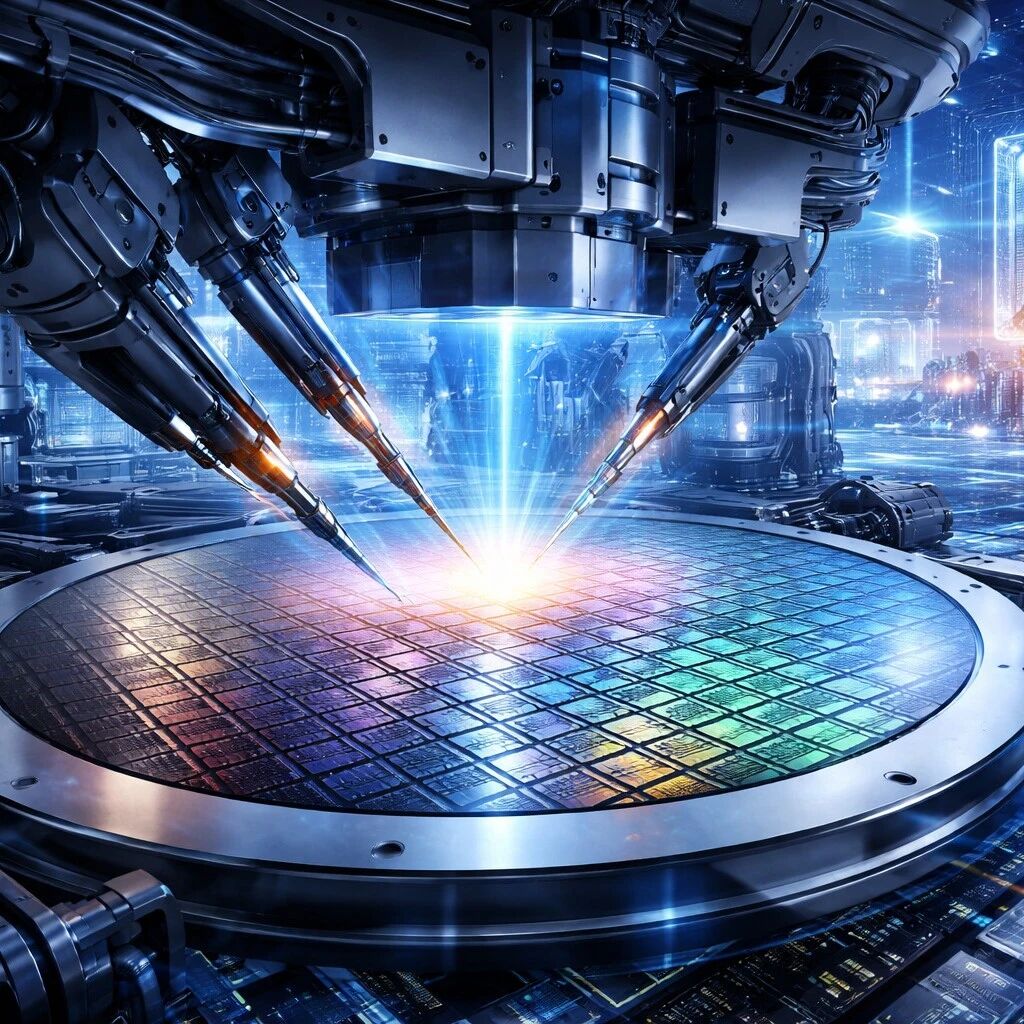

据韩国媒体报道,三星电子已成功制造出全球首款制程低于10纳米(nm)的“次10纳米”DRAM工程裸片,标志着存储器产业正式突破了长期以来的物理极限。

韩媒《The Elec》报道指出,长期以来,DRAM产业的微缩技术主要依赖10纳米级别的工艺(世代涵盖1x、1y、1z、1a、1b、1c至1d)。如今,三星正全力开发全新的“10a”工艺技术。市场分析指出,10a工艺将使线宽进一步缩小至9.5到9.7纳米之间,成为业界首个跨入个位数纳米级别的次10纳米(sub-10nm)工艺技术。

报道称,日前,三星在以10a工艺生产出晶圆后,通过测试晶粒特性,成功确认了工程裸片的诞生。目前,三星正计划通过调整工艺条件来迅速提升并确保良率。

报道表示,这项革命性突破的两大核心技术,在于首度应用了“4F2单元结构(4F Square Cell Structure)”以及“垂直沟道晶体管(VCT,Vertical Channel Transistor)”工艺。现今的DRAM产品普遍采用6F2结构(即3Fx2F的长方形区块),而全新的4F2结构则转变为更紧凑的方形设计(2Fx2F)。仅通过这项结构上的改变,就能将每个集成电路的单元密度大幅提升30%至50%,这不仅能提供更大的存储容量,更能有效降低功耗。

此外,新款DRAM在材料应用上也有所革新,舍弃了过去产品使用的硅(Si),转而采用铟镓锌氧化物(IGZO)等新型材料。由于新一代的存储单元更为狭窄,引入IGZO能有效减少漏电问题,确保数据的良好保存性。

根据三星的发展蓝图,搭载这些新技术变革的10a DRAM预计将于2026年完成开发,并将量产时间定于2028年。4F新结构将在10a世代率先采用,并于未来的10b与10c世代中持续优化。而后继的“10d”世代DRAM则预计将全面迈入“3D DRAM”技术领域,并计划于2029至2030年间问世。(文章来源:科技新报)

推荐阅读