电子计算机,顾名思义,其诞生就是为了计算,世界上第一台电子计算机通常被认为是 ENIAC(Electronic Numerical Integrator and Computer,电子数字积分计算机),它由美国宾夕法尼亚大学摩尔电气工程学院的约翰·莫奇利(John Presper Eckert)和约翰·莫奇利(John Mauchly)领导设计,于 1945年完成 并投入使用。

对于第一代电子计算机的ENIAC来说,其使用了约18,000个真空管,能够执行加、减、乘、除等复杂运算,没有键盘或打字机那样的交互界面,程序通过IBM打孔卡形式输入,ENIAC可以与IBM的制表机相连,将计算结果打印出来。

1947年,美国贝尔实验室的三位科学家——约翰·巴丁(John Bardeen)、沃尔特·布拉顿(Walter Brattain)和威廉·肖克利(William Shockley)发明了第一个点接触式晶体管,进一步推动了电子计算机的发展。

第一个点接触式晶体管

从20世纪50年代中期开始,晶体管取代真空管,催生了第二代计算机。1956年诞生的TRADIC是世界上第一台全晶体管计算机。相比于第一代,晶体管计算机在体积、速度、功耗和稳定性方面都取得了质的飞跃。这使得计算机开始走出纯粹的军事和科研领域,进入企业商务和大学,用于数据处理等更广泛的用途。随着这一转变,打印机、磁带、磁盘等现代计算机常见的外部设备也应运而生。

1958年,集成电路(IC)的发明将大量的晶体管、电阻、电容等元件集成到一片小小的硅片上,标志着计算机进入了第三代。这使得计算机变得更小、更快、功耗更低。 随后,大规模和超大规模集成电路(LSI/VLSI)技术的发展,最终在20世纪70年代催生了微处理器,将整个中央处理器(CPU)集成到单一芯片上,第四代计算机——个人计算机(PC)由此诞生。从IBM PC到苹果的Macintosh,计算机以前所未有的速度和规模进入办公室和家庭,彻底改变了社会面貌。

乔布斯与Macintosh

计算机硬件的飞速演进,对其与外部设备(外设)的通信能力提出了新的要求,直接推动了通信接口技术的变革。

第一代电子管计算机的输入输出设备非常有限,接口通常是为特定机器定制的。随着第二代晶体管计算机在商业领域的应用,连接打印机、存储设备的需求日益增长,推动了接口标准化的进程。为规范电传打字机等终端与调制解调器的通信,RS-232标准于1962年应运而生,因其通用性,在很长一段时间内成为计算机与外设连接的主要方式。

当然了,现在的PC上连接外设的串口已经被性能更高的USB接口所替代,但在工控领域,RS-232以及RS-485是一种常用的通信接口,甚至有些项目还会让人产生串口不足的焦虑  。

。

当需要连接的外设变多时,多个外设需通过共享媒介交换信息时,必须建立一套协调机制来确保数据同步和传输秩序,其核心便是通信各方共同遵守的规则,也就是我们常说的“通信协议”(Protocol)。

正是这种对规范化交互的追求,催生了数据通信接口标准。这些标准不仅定义了协议等软件层面的规范,也涵盖了总线电气特性、电缆规格等硬件要求。标准化的价值在于打破了供应商壁垒,使用户能够自由选择、组合不同厂商的设备,从而推动了整个技术生态的开放与发展。

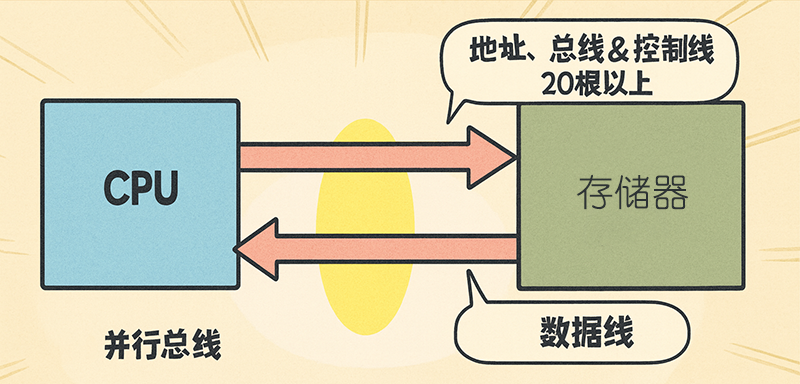

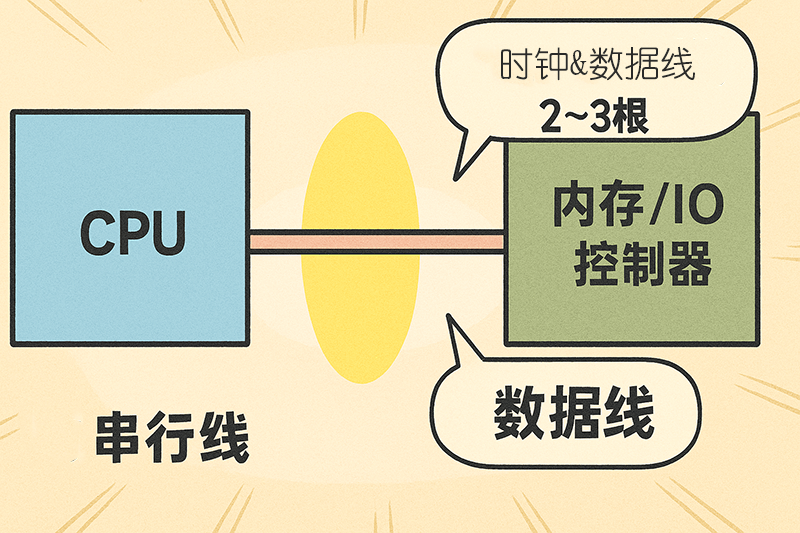

根据应用需求,通信策略可分为 串行 (Serial) 与 并行 (Parallel) 两大类。串行通信通过单一信道逐位传输数据,而并行通信则通过多条并行信道(如8/16/32/64位总线)同时传输多个比特位。

这两种方式的选择取决于具体的应用场景。并行总线凭借其高传输速率,成为访问内存、存取指令或数据的理想选择,但这通常需要10到40根不等的物理连线。相比之下,对于键盘、鼠标等速度要求不高的I/O设备,串行通信的优势便显现出来——仅需2到3根线即可完成连接,极大地简化了布线。

串行通信接口又分为像“I2C、SPI、UART、CAN”这类的相对低速率的串行接口,还有像“PCIE、USB、Ethernet、Infiniband、MIPI、HDMI”这类的高速串行接口。

老wu这里主要介绍的是嵌入式开发中常用的与外设通信的低速串行通信接口。

I²C总线

I²C总线最初是由飞利浦公司(现在的恩智浦半导体 NXP Semiconductors)在1980年代初提出的双线式时钟同步串行接口。其初衷是为了简化电视机内部芯片间的连接,它最大的特点是仅需双线即可实现强大的多设备通信能力,总线上可以存在多个主设备。

I²C总线操作

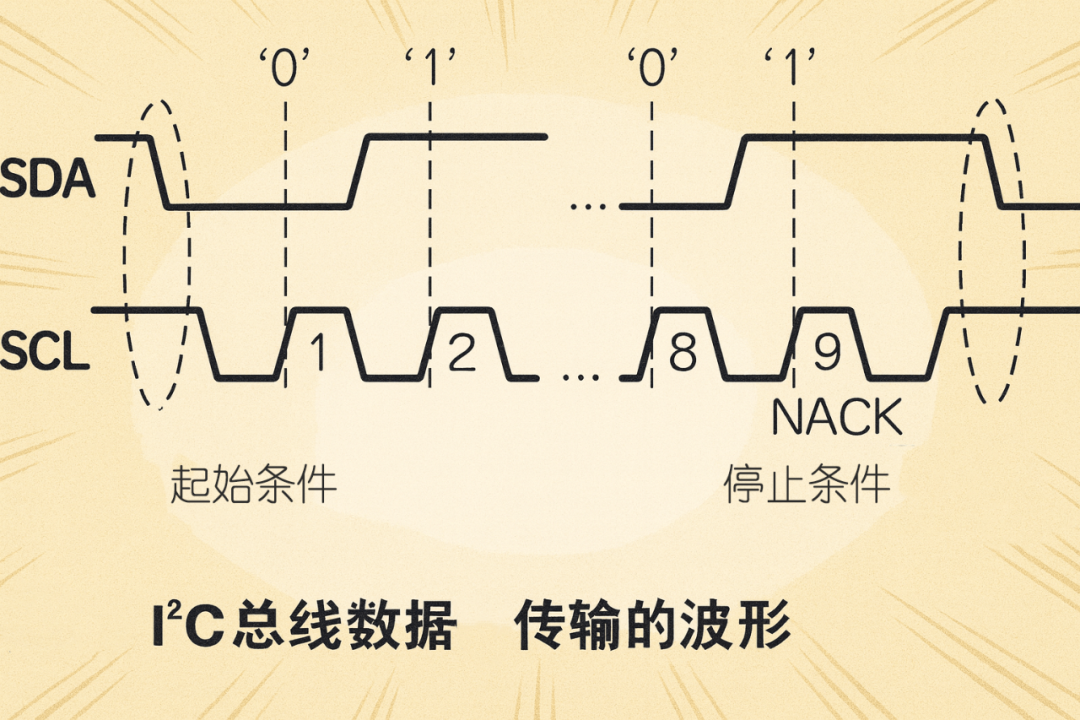

I²C总线通过SCL(时钟)和SDA(数据)这两条信号线进行数据传输。两条信号线都带有上拉电阻,并由开漏型端口驱动。与SPI不同,I²C总线没有芯片选择信号,每个从设备通过比较总线上由主设备发送的从机地址信息来判断是否与自身地址一致,如果一致则做出响应。

由于无法使用芯片选择信号来指示数据传输的开始或结束,因此必须通过SCL和SDA信号线来判断传输的开始或结束。为此,协议规定了在正常数据传输中不会出现的信号模式,即起始条件和停止条件。

I²C总线数据传输波形的示例

在I²C中,正常数据传输期间SDA的变化发生在SCL为“L”电平时,并在SCL的上升沿被接收。当SCL为“H”电平时,SDA的下降沿被视作起始条件,SDA的上升沿则被视作停止条件。

SPI总线

SPI(Serial Peripheral Interface),意为串行外设接口。它是由摩托罗拉公司在20世纪80年代中期率先提出的一种高速、全双工、同步串行接口。相比I²C,SPI的硬件结构更简单,协议开销更小,因此通常能达到更高的通信速率。(摩托罗拉半导体后来被飞思卡尔半导体并购,之后飞思卡尔又被NXP并购,PS:写这篇文章时老wu才发现,好家伙,现在NXP是手握了I2C和SPI协议的标准了  )。

)。

SPI主要用于电路板内设备连接,采用一个主设备控制多个从设备的模式。由于其接口相对简单,除了串行EEPROM外,也用于I/O设备等。

SPI总线的设备连接示例

SPI主要由四根信号线构成:

SCLK (Serial Clock): 串行时钟信号,由主设备产生,用于同步数据传输。 MOSI (Master Out Slave In): 主设备输出、从设备输入数据线。 MISO (Master In Slave Out): 主设备输入、从设备输出数据线。 SS/CS (Slave Select/Chip Select): 从设备片选信号,由主设备控制,用于选择与之通信的特定从设备。该信号通常是低电平有效。

SPI总线也被用作SD/MMC卡的简易访问接口(可在SD/MMC模式和SPI模式之间切换),是一种方便的串行访问接口。

数据传输过程如下:

片选: 主设备通过将特定从设备的SS/CS线拉低来选择要通信的从设备。

时钟生成: 主设备开始产生SCLK时钟信号,为数据传输提供同步节拍。

数据交换: 在每个SCLK时钟周期内,主设备通过MOSI线向从设备发送一位数据的同时,也通过MISO线从从设备接收一位数据,实现了全双工通信。这个过程可以看作是主从设备内部的两个双向移位寄存器在进行数据交换。

结束通信: 数据传输完成后,主设备将SS/CS线拉高,结束本次通信。

UART

UART (Universal Asynchronous Receiver/Transmitter),即“通用异步收发器”。与I²C和SPI依赖共享时钟线不同,UART的精髓在于“异步”——它在没有时钟线的情况下,实现了可靠的数据交换。

波特率 (Baud Rate): 定义了每秒传输的码元(在这里就是比特)数。例如9600波特率意味着每秒传输9600位,每位持续时间约为104微秒。双方的波特率必须尽可能接近(误差通常要求在2%以内)。 数据位 (Data Bits): 每帧传输的有效数据位数,通常是7位或8位。 校验位 (Parity Bit): 一种可选的、简单的错误检测机制,可以是奇校验、偶校验或无校验。 停止位 (Stop Bits): 在数据帧末尾的信号,用于标记帧的结束,通常是1位、1.5位或2位。

RS-232-C

RTS (Request to Send): DTE告诉DCE,“我准备好要发送数据了”。 CTS (Clear to Send): DCE回应DTE,“我已经准备好接收你的数据,你可以发送了”。

RS-485

RS-485(EIA-485)是RS-232的继任者,它只定义了物理层(电气特性),旨在克服RS-232在距离、速度和组网能力上的限制。

核心优势:差分信号

RS-485不使用相对于GND的电压来表示信号,而是使用两根信号线(通常标记为A和B)之间的电压差 。例如,当A线电压比B线高时表示逻辑'1',反之表示逻辑'0'。

这种差分方式具有极强的共模噪声抑制能力 。沿途感应到的噪声会同等地作用于A和B两根线上,但它们之间的电压差基本保持不变。这使得RS-485能够在长达1.2公里、充满电磁干扰的工业环境中稳定地进行高达10Mbps的通信。

多点半双工网络

RS-485总线允许连接多个收发器(标准规定最多32个,现在有高阻抗版本支持更多),形成一个多点网络。

由于所有设备共享同一对线,通信通常是半双工的,即在任何时刻,只能有一个设备处于发送状态。这需要上层协议来控制总线访问权,例如Modbus RTU协议就常运行在RS-485物理层之上。

在高速或长距离传输中,信号在传输线末端会发生反射,如同回声一样干扰正常通信。为了消除反射,必须在RS-485总线的两个最远端并联一个终端电阻(通常为120Ω,与传输线缆的特性阻抗匹配)。

CAN (Controller Area Network) 总线

CAN总线由德国博世(BOSCH)在1980年代为汽车应用开发,现已成为工业自动化的标准之一。它不仅仅是一个通信协议,更是一个复杂的系统,具备强大的错误检测和容错能力。

CAN网络上没有设备地址的概念。取而代之的是消息ID。每个节点广播带有特定ID的报文,网络上的其他节点根据ID来决定是否需要接收和处理这条消息。这种方式使得系统配置非常灵活,增删节点无需修改其他节点的软件。

非破坏性位仲裁机制

这是CAN最精妙的设计。多个节点可以同时开始发送报文。CAN定义了两种状态:显性('0')和 隐性('1') ,显性位可以覆盖隐性位。所有发送节点在发送每一位的同时都会监听总线。如果一个节点发送了隐性位却监听到显性位,它就知道有更高优先级的报文(ID值更小)正在传输,于是它会立即停止发送并转为接收模式。这个过程保证了最高优先级的报文总能无损地传输完毕,实现了高效的总线冲突解决。

强大的错误处理

CAN内置了多种错误检测机制,包括CRC校验、位填充(连续5个相同位后插入一个反转位以保证时钟同步)、帧格式检查等。

每个节点都有自己的错误计数器。当检测到错误或发送错误时,计数器会增加。当计数器超过一定阈值,节点会自动进入错误被动状态甚至离线状态,防止有故障的节点瘫痪整个网络。

物理层

最常见的是基于ISO 11898-2的高速CAN,使用差分信号,最高速率1Mbps,需要120Ω终端电阻。

还有ISO 11898-3定义的低速/容错CAN,速率较低(最高125kbps),但即使一根线断路也能继续通信。

CAN-FD

CAN-FD并非一个全新的协议,而是对经典CAN协议的扩展和增强,旨在提供更高的带宽。它通过两个核心改进实现了这一目标:

灵活可变的数据速率

CAN-FD最革命性的创新在于将一帧报文的传输分为两个速率阶段:

仲裁阶段 (Arbitration Phase): 包含帧起始、消息ID、控制场等部分。这个阶段的传输速率与经典CAN相同(如500kbps或1Mbps),以确保与总线物理特性和仲裁机制的兼容性。

数据阶段 (Data Phase): 包含数据载荷和CRC校验码。一旦仲裁结束,总线上只有一个节点在发言,此时不再需要严格的位同步来进行冲突检测。CAN-FD利用这个窗口期,将比特率切换到一个远高于仲裁速率的水平(例如2Mbps, 5Mbps,甚至更高)。传输完数据和CRC后,速率再切换回正常的仲裁速率。

这种速率切换由控制场中的一个新比特BRS (Bit Rate Switch) 控制。

更大的数据载荷

为了提高数据传输效率,CAN-FD将每帧的最大数据载荷从经典CAN的8字节大幅提升至64字节。这使得传输大量数据(如传感器原始数据、OTA固件包)的协议开销显著降低,效率提升了数倍。

为了保护更大的数据载荷,CAN-FD也采用了更强大的CRC校验算法(根据数据长度选择不同的CRC多项式)。

CAN-FD的兼容性问题:

这是一个至关重要的实践要点。虽然CAN-FD是对经典CAN的扩展,但一个只支持经典CAN的节点无法正确解析CAN-FD报文。当经典CAN节点在总线上看到一个CAN-FD报文(其控制场中有新的保留位被设置为'1')时,它会认为这是一个格式错误,并发送一个错误帧来干扰总线。

因此,CAN-FD网络必须由所有支持CAN-FD的节点组成。你不能在一个总线上混合使用经典CAN和CAN-FD节点。不过,好消息是,几乎所有的CAN-FD控制器都向下兼容,可以被配置成在纯经典CAN模式下工作,这为系统迁移提供了便利。

RS-485(EIA-485)是RS-232的继任者,它只定义了物理层(电气特性),旨在克服RS-232在距离、速度和组网能力上的限制。

核心优势:差分信号

RS-485不使用相对于GND的电压来表示信号,而是使用两根信号线(通常标记为A和B)之间的 电压差 。例如,当A线电压比B线高时表示逻辑'1',反之表示逻辑'0'。这种差分方式具有极强的 共模噪声抑制能力 。沿途感应到的噪声会同等地作用于A和B两根线上,但它们之间的电压差基本保持不变。这使得RS-485能够在长达1.2公里、充满电磁干扰的工业环境中稳定地进行高达10Mbps的通信。多点半双工网络 RS-485总线允许连接多个收发器(标准规定最多32个,现在有高阻抗版本支持更多),形成一个多点网络。 由于所有设备共享同一对线,通信通常是半双工的,即在任何时刻,只能有一个设备处于发送状态。这需要上层协议来控制总线访问权,例如Modbus RTU协议就常运行在RS-485物理层之上。

CAN (Controller Area Network) 总线

CAN总线由德国博世(BOSCH)在1980年代为汽车应用开发,现已成为工业自动化的标准之一。它不仅仅是一个通信协议,更是一个复杂的系统,具备强大的错误检测和容错能力。

CAN网络上没有设备地址的概念。取而代之的是消息ID。每个节点广播带有特定ID的报文,网络上的其他节点根据ID来决定是否需要接收和处理这条消息。这种方式使得系统配置非常灵活,增删节点无需修改其他节点的软件。

CAN-FD并非一个全新的协议,而是对经典CAN协议的扩展和增强,旨在提供更高的带宽。它通过两个核心改进实现了这一目标:

灵活可变的数据速率

CAN-FD最革命性的创新在于将一帧报文的传输分为两个速率阶段:

仲裁阶段 (Arbitration Phase): 包含帧起始、消息ID、控制场等部分。这个阶段的传输速率与经典CAN相同(如500kbps或1Mbps),以确保与总线物理特性和仲裁机制的兼容性。

数据阶段 (Data Phase): 包含数据载荷和CRC校验码。一旦仲裁结束,总线上只有一个节点在发言,此时不再需要严格的位同步来进行冲突检测。CAN-FD利用这个窗口期,将比特率切换到一个远高于仲裁速率的水平(例如2Mbps, 5Mbps,甚至更高)。传输完数据和CRC后,速率再切换回正常的仲裁速率。

这种速率切换由控制场中的一个新比特BRS (Bit Rate Switch) 控制。

更大的数据载荷

为了提高数据传输效率,CAN-FD将每帧的最大数据载荷从经典CAN的8字节大幅提升至64字节。这使得传输大量数据(如传感器原始数据、OTA固件包)的协议开销显著降低,效率提升了数倍。

为了保护更大的数据载荷,CAN-FD也采用了更强大的CRC校验算法(根据数据长度选择不同的CRC多项式)。

CAN-FD的兼容性问题:

这是一个至关重要的实践要点。虽然CAN-FD是对经典CAN的扩展,但一个只支持经典CAN的节点无法正确解析CAN-FD报文。当经典CAN节点在总线上看到一个CAN-FD报文(其控制场中有新的保留位被设置为'1')时,它会认为这是一个格式错误,并发送一个错误帧来干扰总线。

因此,CAN-FD网络必须由所有支持CAN-FD的节点组成。你不能在一个总线上混合使用经典CAN和CAN-FD节点。不过,好消息是,几乎所有的CAN-FD控制器都向下兼容,可以被配置成在纯经典CAN模式下工作,这为系统迁移提供了便利。