想象一下,你是个芯片设计师,雄心勃勃,想搞个超级巨无霸芯片,让计算力原地起飞!

结果,你刚撸起袖子,就被一盆冷水浇醒,光刻机这位“刻印大师”冷冷地说:“尺寸?别想了,最大就给你一块巧克力那么大!”

这块“巧克力”有多大呢?

大约 26mm x 33mm,也就是 858 平方毫米。

这就是芯片制造的核心工艺——光刻的“光照窗口限制”(也叫掩模版限制)。

简单说,光刻机一次曝光,最多只能雕刻这么大一块区域。想超纲?门儿都没有!

所以,看看那些“巨无霸”GPU们,在“巧克力”墙前都得乖乖低头:

A100 GPU: 826 mm² (内心OS:我尽力了!)

H100 GPU: 814 mm² (内心OS:再挤挤!)

B200 GPU (GB202): 750 mm² (内心OS:前辈们,我小点省电!)

所以,横亘在所有芯片前面,就有这么一道面积墙,掩模版限制最大就是26mmX33mm。

你想想,这尺寸跟巧克力差不多大。

如果你的芯片设计超出了这个范围,那就对不起,你得把一个大芯片“劈”成好几块小芯片(业内叫“小芯片”或“裸片”),然后分别制造,最后再通过复杂的封装技术把它们拼起来 。

这个就是2D的chiplet。

例如:AMD就是用chiplet的技术,实现了Core die 和 IO die的互联。从而实现了对英特尔的技术路线的超越。

这就好比你做个巨型拼图,不能一次性印出来,得把图案切成小块,分别印刷,最后再一块块粘起来。

芯片之间的数据传输,不再是“内部消化”,而是要跨越封装边界,甚至要通过外部总线(比如UPI,PCIe、NVLink,Infinity Fabric)。

这就像你家客厅和厨房之间隔了条马路,每次拿个菜都得过马路,能不慢吗?延迟蹭蹭往上涨,带宽还受限。

数据在芯片之间跑得越远,消耗的能量就越多。这就像你跑长途比跑短途更费油一个道理。

所以,光刻机的“光照窗口”就像一道无形的墙,把传统CPU的尺寸限制得死死的。

就算你突破了尺寸限制,还有个更要命的问题,那就是“冯·诺依曼瓶颈”。

这个概念是计算机科学的“老祖宗”冯·诺依曼提出来的,它描述的是处理器和内存分离的架构 。

在咱们的电脑里,CPU负责计算,内存负责存储数据。

它们之间通过总线连接 。

问题来了,CPU的计算速度越来越快,但数据在内存和CPU之间传输的速度却跟不上 。

这就导致CPU经常“等米下锅”,大部分时间都在等数据,而不是在计算 。

这就像一个超级大厨,刀工飞快,但食材每次都得从十里外的仓库运过来,那效率能高吗?

对于AI计算,这个问题尤其严重 。

现在的大模型动辄几十亿、上万亿参数,训练一次要处理天文数字的数据 。

这些数据需要在处理器和内存之间来回搬运,距离越远,延迟越高,能耗越大 。

训练一个大型语言模型可能要花几个月,消耗的电量比普通家庭同期用电量还多 。

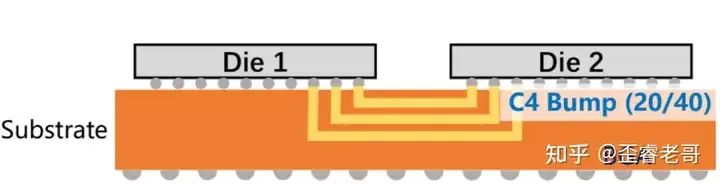

所以,对于AI芯片采用的就是,使用2.5D的chiplet。

例如 AI芯片,就是把多个HBM,和多个GPU封装在一起。

例如上图就是两个GPU,多个HBM通过底层硅基板(silicon interposer)互联在一起。

硅基板的好处就是比普通的基板,TSV的通孔更小,互联密度更大,能够实现更高带宽和更高密度的互联。

也就是说

在CPU目前是通过,2D的chiplet进行互联

而GPU领域,目前是通过2.5D的硅基板进行互联。

这些都是因为有光刻窗口限制,

目前没有办法制造超过858平方毫米的die。

其实仔细看这玩意的规模就知道,不是这样的。

包含 84 个相互连接的“裸片”(die),

每一行有12个。

一共7行。

一共84个die。

每个裸片的尺寸为 550 平方毫米。

84*550mm2=46200mm2,加上划片槽,就和WSE-2宣称的一样了。

所以,本质上,这玩意大芯片,就是一张wafer,把四周圆弧的部分切后,变成了一个DIE的阵列。

每个die的面积仍然在一个光照窗口之内。

但是WSE-2没有切割,他们创新的把划片槽的位置也用上了。

他们没有沿着这些线切割晶圆,而是在金属层中增加了额外的光刻步骤,以图案化“跨裸片导线”(cross-die wires)或“拼接线” 。

实际上就是用芯片制造工艺的RDL层。

RDL是集成电路上的额外金属层,用于将I/O焊盘引出到芯片的其他位置,从而简化芯片间的连接或分散焊球的接触点。

在先进封装中,RDL对于实现更高的互连密度、信号速度和电源效率至关重要,尤其是在AI应用中。

它们通常是晶圆级布线工艺的一部分,例如扇出晶圆级封装(FoWLP)或芯片-晶圆-基板(CoWoS)封装。

WSE-2用了RDL层实现了跨die的互联,这是算是一种不错的创新。

但是,具体到每个die,仍然受到面积墙的限制。

无论是传统的切割封装 (2D Chiplet),还是高级的叠叠乐 (2.5D Interposer),

抑或是 Cerebras 这种整片晶圆互联的黑科技 (Wafer Scale),

光刻机那一次曝光 26x33mm 的“光照窗口限制”,依然是当今单颗芯片裸片 (Die) 不可逾越的“面积墙”或“巧克力天花板”。

这就是芯片制造领域一个甜蜜(尺寸像巧克力)又苦涩(限制发展)的宿命.

设计师们只能在“巧克力块”内绞尽脑汁,或者想尽办法让这些“巧克力块”们能更高效地“聊天”。

想要一整块无限大的“巧克力”?

抱歉,光刻机大佬目前还不批这个条子!

▼ 德州仪器免费培训 最新DSP线下实操▼

点击晓成员报名