最近,我们看过了许多有趣的讨论与设计实例合作内容,这些设计都在构思使用便宜(而且造型可爱!)的瞬时接触式的单刀单掷(SPST)开关,来实现电源开关的电路。而最近,本刊长期投稿的作者R Jayapal提出了一个延伸设计也相当有趣,主题是控制相对较高的直流(DC)电压,他在设计中选择的目标电压是48伏特。

在实现高电压控制功能的过程中,Jayapal的设计选择切换的是输入电源的负端(Vss,也就是“接地”),而不是较为常见的正端(Vdd)。当然,这样的选择在物理上完全没问题(毕竟电子可不在乎这些区别!)。但因为这种做法不那么常见,我担心对某些使用者来说,这可能会带来无意的、甚至具破坏性的误接风险。

改以正电源轨为参考点的开关方式

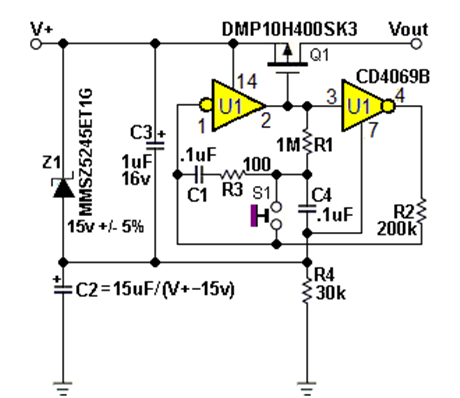

图1所示的电路则采取了不同的做法来避免上述问题。

图1:以V+电源轨为参考的Flip ON/Flop OFF电路。

注:若V+ < 15V,则请将R4设为0,并省略C2与Z1。请确保C2的额定电压大于(V+ – 15V),若V+ > 80V,则R4应大于4V+2。

图1的设计回归了一个早期的主题:使用P通道FET (PFET)切换正电源轨来进行电源控制,并通过一对无缓冲的CMOS反相器组成的T锁存器(toggle latch)来控制该FET。这项基本电路的设计曾在“

”(Flip ON Flop OFF without a Flip/Flop)一文中有详细描述。

此处的不同之处在于,整个电路的节点均以V+为参考,而非接地(GND)。此外,设计中加入了一颗齐纳二极管Z1,以合成一个局部偏压参考。因此,几乎可以兼容所有的输入V+电压,只要不超过Q1组件的Vds额定范围。当然,若这仍不够,市面上也有更高耐压等级的FET可供选择。

请务必将U1芯片中未使用的引脚输入接至V+,以避免可能会产生的不稳定。