LEF

相关文档已上传星球。

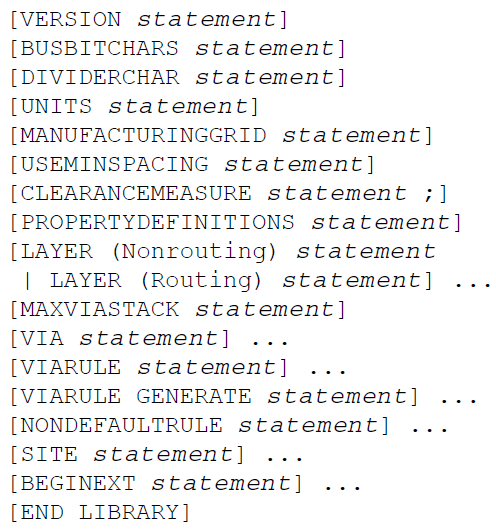

LEF即Library exchange format,是Cadence公司的物理库的描述格式。可以在单个LEF文件中定义所有物理库信息;然而,这会产生复杂且难以管理的文件,所以一般LEF分为tech lef跟cell lef两种;不论是哪个阶段的工具要使用lef都必须先读入tech lef再读入cell lef, 因为cell lef中要引用tech lef中定义的信息。tech lef部分包含有关所有金属连线的信息,工艺信息和相关设计规则,而cell lef部分包含与每个标准单元的几何形状相关的信息。

将上图中的LEF描述语句含义和案例汇集成如下表所示。

描述语句 | 含义 | 案例 |

VERSION | LEF文件的版本 | 5.6、5.7、5.8 |

BUSBITCHARS | 总线分隔符 | [] |

DIVIDERCHAR | 层次化设计的分隔符 | / |

UNITS | 定义设计中各种单位的database unit(数据库中的单位)和Standard International(国际标准单位)转换关系;类似于比例尺;LEF支持的数值是100, 200, 400, 800, 1000, 2000, 4000, 8000, 10000和 20000 | 2000 |

MANUFACTURINGGRID | 工艺生产格点,cell和routing需要保证的最小尺寸 | 0.0050 |

USEMINSPACING | 定义如何计算OBS(Obstruction,指cell内部的走线或blockage)的minimum spacing。 | OBS OFF |

CLEARANCEMEASURE | 定义SPACING 和SPACINGTABLE语句描述的object的spacing计算方法;常用的是MAXXY和EUCLIDEAN;MAXXY是按object最长的x轴方向间距或者最长的y轴方向间距来计算spacing;EUCLIDEAN是使用欧几里得间距计算object之间的spacing,即x2+y2的平方跟 | EUCLIDEAN |

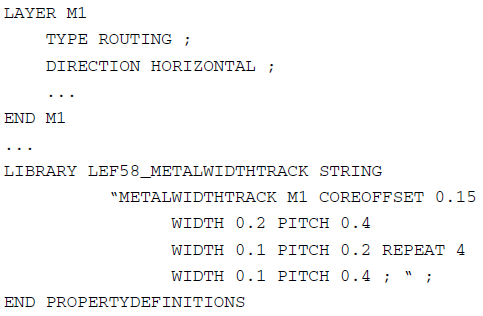

PROPERTYDEFINITIONS | 属性定义,用于各种MINSTEP rule、SPACING rule、ENCLOSURE rule、MAXEDGES rule等的描述语句中 |

|

LAYER | APR用到的各个层的定义,包括但不限于: 类型(TYPE) 间距(SPCING) 宽度(WIDTH) 面积(AREA) 中心距(pitch)等。 主要是用于约束router绕线规则和对绕线质量评估 |

|

MAXVIASTACK | 定义单个via上的最大stack via数量 |

|

VIA | 定义每种via的特征。 |

|

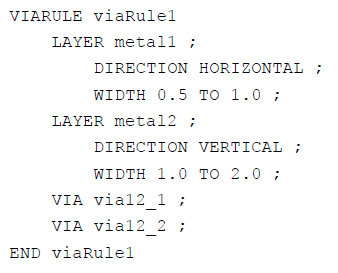

VIARULE | 定义在同一net的不同wire的intersection(交叉点)使用什么何种via。 |

|

VIARULE GENERATE | 定义via arrays(通孔阵列)类型的VIARULE。 |

|

NONDEFAULTRULE | 定义signal net(信号线)的wiring width(布线宽度)、design rule spacing(设计规则间距)和via size(via尺寸)。 |

|

SITE | SITE定义了placement(布局)使用的site(布局使用的die上的格点单元)。 |

|

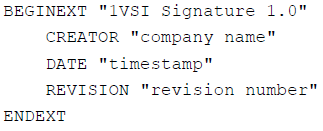

BEGINEXT | 向LEF文件添加自定义语法,不使用该语法的工具可以忽略该语法。 |

|

END LIBRARY | LEF文件结束语句。 | END LIBRARY |

Cell LEF语法和tech LEF类似,中包含单元库中各单元的信息,其分为两个部分:一部分采用SITE语句对布局最小单位定义,另一部分是采用MACRO语句对单元属性及几何形状的描述。

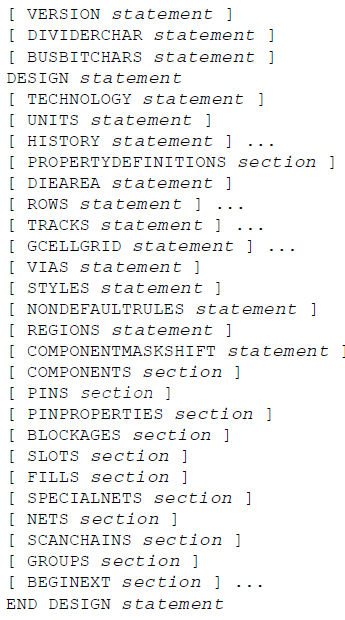

DEF

DEF即Design exchange format,用于以 ASCII 格式表示集成电路的物理布局信息。DEF文件与LEF文件密切相关。因此,正确显示物理设计需要这两个文件。 DEF 文件格式由 Cadence Design System 开发。每当我们需要将设计数据库(design database)从一个 EDA 工具转移到另一个 EDA 工具以进行进一步的物理实现(physical implementation)或分析时,我们都会使用 DEF 文件来转移设计数据。例如,PnR(placement and route)数据库上的 IR 分析或 PnR数据库上的 STA,我们以 DEF文件的形式传输设计数据库。

DEF文件包含电路的特定设计信息,它是物理设计期间任何时间节点的芯片设计的一种呈现方式。DEF文件可以传送逻辑设计数据和物理设计数据,也就说DEF文件可以既包含芯片的逻辑信息又包含芯片的物理信息。

DEF文件一般包含如下描述语句。

将上图中的描述语句含义和案例汇集成如下表。

描述语句 | 含义 | 案例 |

| |||

VERSION | DEF文件的版本 | 5.8 |

| |||

DIVIDERCHAR | 层次化设计的分割符 | / |

| |||

BUSBITCHARS | 总线分隔符 | [] |

| |||

TECHNOLOGY | 指定设计的工艺节点名称(technology name) | |

| |||

UNITS | 定义设计中各种单位的database unit(数据库中的单位)和Standard International(国际标准单位)转换关系;协议规定该值必须小于或等于tech LEF中指定的值,最好两边值一致,在某些先进工艺节点,如果两个值定义不一致,工具物理信息计算可能出现偏差或错误,例如VIA位置可能会偏移。 | 2000 |

| |||

HISTORY | 列出当前设计的历史记录 | |

| |||

PROPERTYDEFINITIONS | 属性定义;列出设计中使用的所有属性,所有在DEF文件中调用的属性,都必须提前在PROPERTYDEFINITIONS语句中声明。 |

|

| |||

DIEAREA | 描述设计的形状和大小 | DIEAREA ( 0 0 ) ( 100 100 ) ; DIEAREA ( 0 0 ) ( 0 100 ) ( 50 100 ) ( 50 50 ) ( 100 50 ) ( 100 0 ) |

| |||

ROW | 所有的标准单元都需要摆放在ROW上,所以在DEF中需要将所有用到的SITE都定义全,SITE从Tech LEF中读入。 |

|

| |||

TRACKS | 定义标准单元的绕线格点(routing grid) |

|

| |||

GCELLGRID | 定义基于标准单元的设计的gcell grid(gcell是布局布线工具计算绕线拥塞的最小单元) |

|

| |||

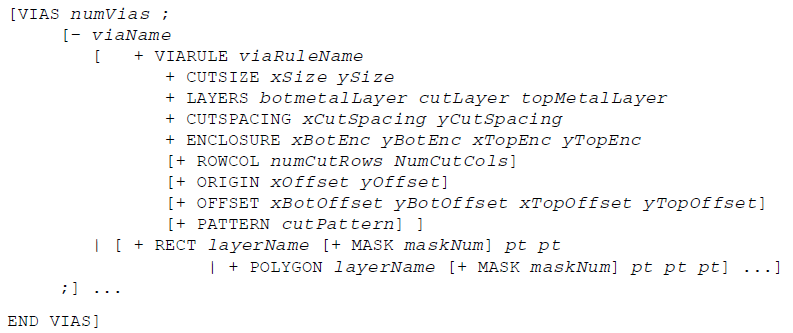

VIAS | 定义所有via的名称和几何形状信息 |

|

| |||

STYLES | 定义多边形,用于精确描述每个net wire端点的外部边界。 |

|

| |||

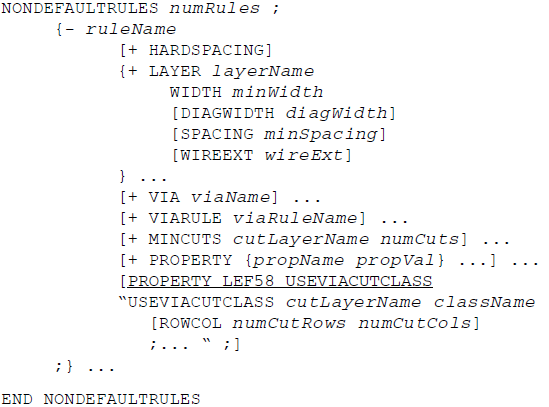

NONDEFAULTRULES | 定义tech LEF中没有定义但是在设计中使用的nondefault rules |

|

| |||

REGIONS | 定义设计中的region(包括FENCE 和GUIDE) |

|

| |||

| COMPONENTMASKSHIFT | 定义哪些绕线层可能会偏离初始的mask colors(掩模版颜色) | COMPONENTMASKSHIFT M3 M2 VIA1 M1 ; | |||

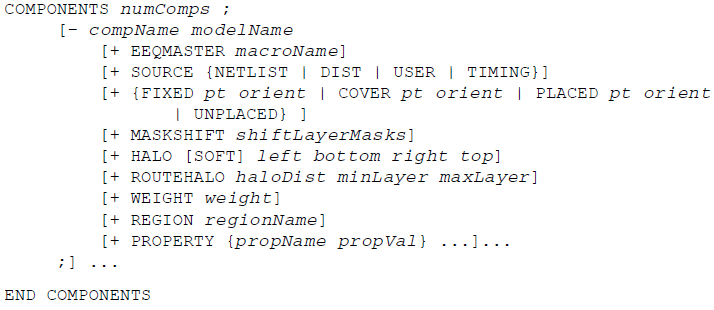

COMPONENT | 定义设计中的各种组件(标准单元、Macro等)的location和其他相关属性 |

|

| |||

PINS | 定义输入输出端口(IO Port) |

|

| |||

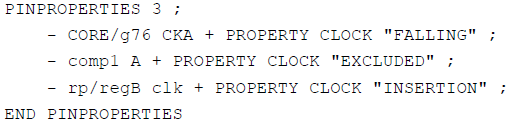

PINPROPERTIES | 定义设计中某些component pin(标准单元或Macro)的特性 |

|

| |||

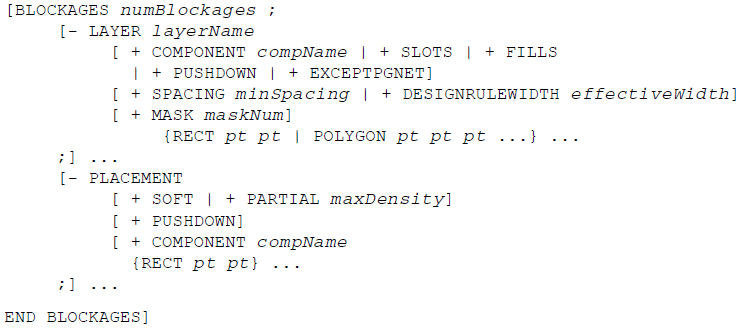

BLOCKAGES | 定义设计中的placement blockages和 routing blockages。 |

|

| |||

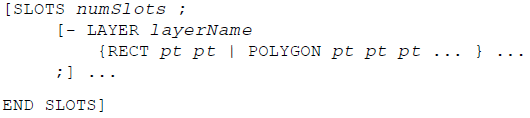

SLOTS | 定义形成线槽(the slotting of the wires)的多边形形状 |

|

| |||

FILLS | 定义设计中metal fills的形状 |

|

| |||

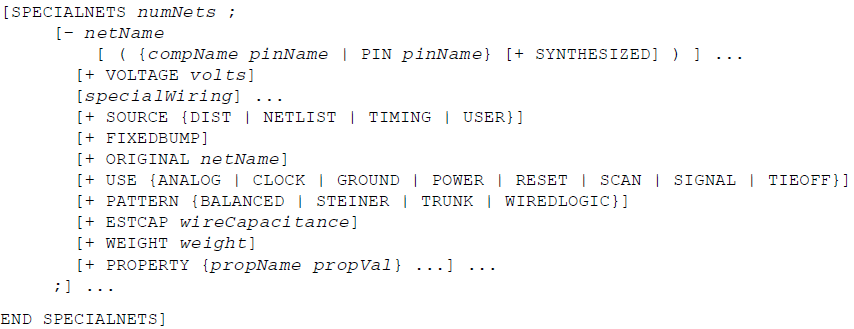

SPECIALNETS | 定义special nets(主要是电源和地)的逻辑连接和绕线信息 |

|

| |||

NETS | 定义nets的逻辑连接和绕线信息 |

|

| |||

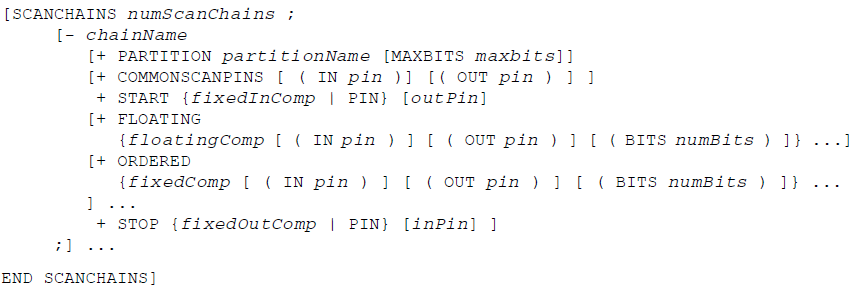

SCANCHAINS | 定义设计中的scan chains(扫描链)信息 |

|

| |||

GROUPS | 定义设计中的components group |

|

| |||

BEGINEXT | 添加自定义语法 |

|

| |||

END DESIGN | 结束语句 | END DESIGN |

| |||