衬底的缺陷控制,12吋晶圆对微管(Micropipe)、位错(如TSD、TED、BPD)等晶体缺陷的控制比8吋(200毫米)更难。这些缺陷会严重影响最终器件的良率和可靠性。放大尺寸时,保持整个衬底生长设备内部的温度场和气流场均匀度,从而获得低缺陷密度的晶体,是巨大的物理和工程挑战。

晶圆切磨抛:碳化硅硬度极高(莫氏硬度9.2,仅次于钻石),切割、研磨和抛光耗时耗力,且容易产生裂纹和表面损伤。12吋晶圆的加工一致性和全局平整度控制是巨大挑战。当然,各种新技术不断涌现,但无论用什么技术,12吋的切磨抛都要比8吋困难不少。

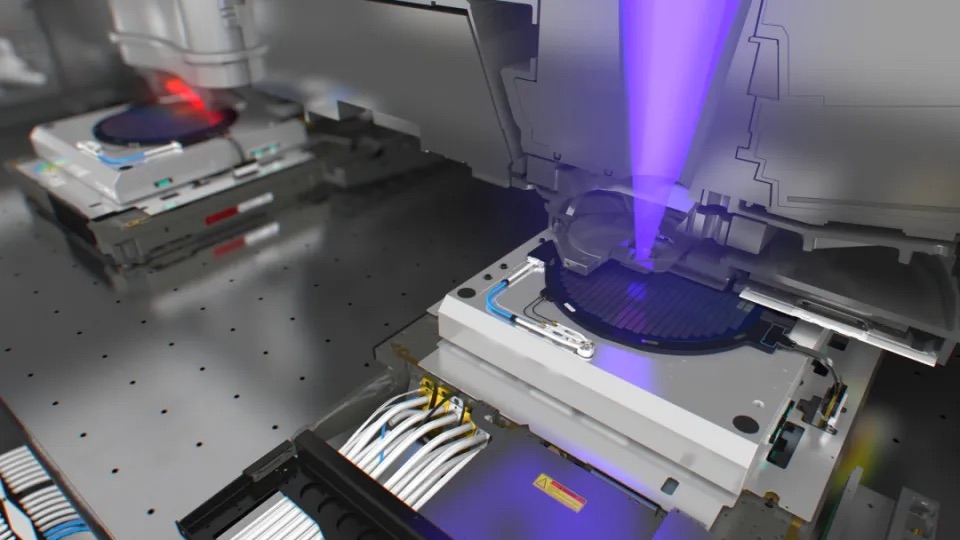

在衬底上生长出高质量、厚度和掺杂浓度均匀的外延层是制造器件的基础。对于12吋晶圆,要在整个巨大的面积上实现原子级精度的均匀外延,对反应室的设计、气流和温度控制提出了前所未有的要求。任何微小的不均匀都会导致器件参数离散,良率下降。

高温高能离子注入与激活,碳化硅的掺杂(如P型掺杂的铝)需要极高的能量和温度才能注入,并且需要在1600-1800°C的超高温度下进行退火激活。这个工艺本身就对设备的均匀性和工艺控制要求极高。在12吋晶圆上,实现均匀的高温处理和避免晶圆翘曲等会更加困难。

栅氧质量与可靠性,碳化硅MOSFET的沟道迁移率低和阈值电压不稳定的核心问题源于SiC/SiO2界面处的高密度界面态。在12吋晶圆上,要保证整个晶圆表面形成高质量、低缺陷密度的栅氧层,其均匀性和一致性是影响器件性能和良率的关键。

高精度光刻与刻蚀,虽然12吋产线可以利用成熟的硅基先进光刻设备,但碳化硅的刻蚀完全不同。由于其化学惰性高,需要更高能量的等离子体进行干法刻蚀。在12吋晶圆上实现高各向异性、低损伤、高均匀性的刻蚀是一个非常大的挑战。

金属化与互联,需要能够承受高温工作的金属系统(如难熔金属)。在12吋晶圆上实现低接触电阻、高均匀性的欧姆接触,以及可靠的互联,同样面临均匀性和应力控制的挑战。

来源:老周公号