【内容目录】

2.《光电CPO封装测试的挑战与未来AI产业发展》

3.《面向人工智能世纪的光互连技术与光计算芯粒 》

4.《光计算系统的可行路径与挑战》

5.《硅光微环调制器与大容量光子互连芯片 》

6.《智算时代的硅光技术趋势与挑战 》

7.《NOEIC光电器件封装与测试平台研究进展 》

8.《CPO 与Foundry 生态系加速光电芯片产业化进程 》

9.结语

光电芯片设计与封装技术论坛精彩回顾

光电芯片与封装设计论坛现场(图源:湾芯展现场)

2025年10月15-17日,在全国半导体行业万众瞩目的湾芯展上,一场别开生面的光电芯片设计与封装技术开放式论坛成功举办,主办方深芯盟联合业界知名光电芯片EDA公司-逍遥科技和深圳技术大学联合举办。大会邀请了逍遥科技CTO陈昇祐博士、SemiVision创始人陈熙先生、新加坡Creideas CTO林福江教授、光本位副总裁姚金鑫先生、松山湖材料实验室张巍巍博士、中兴光电子赵建国博士、国家信息光电创新中心李宗阳博士等业界知名专家齐聚一堂,围绕AI算力基础、光电芯片设计、光计算和光电共封装CPO的设计、封测和系统集成展开深度的技术交流。

演讲嘉宾围绕国产光电子产业链的上下游的材料技术瓶颈,工艺技术难点、全光路光学芯片设计工具等业界热门话题,以芯片设计技术为引,向业界展示了各自领导的专业团队的解决方案。驻足聆听会议人数达千人,演讲内容可以说是“理论与实践相结合,从材料到应用的全产业链解码”。

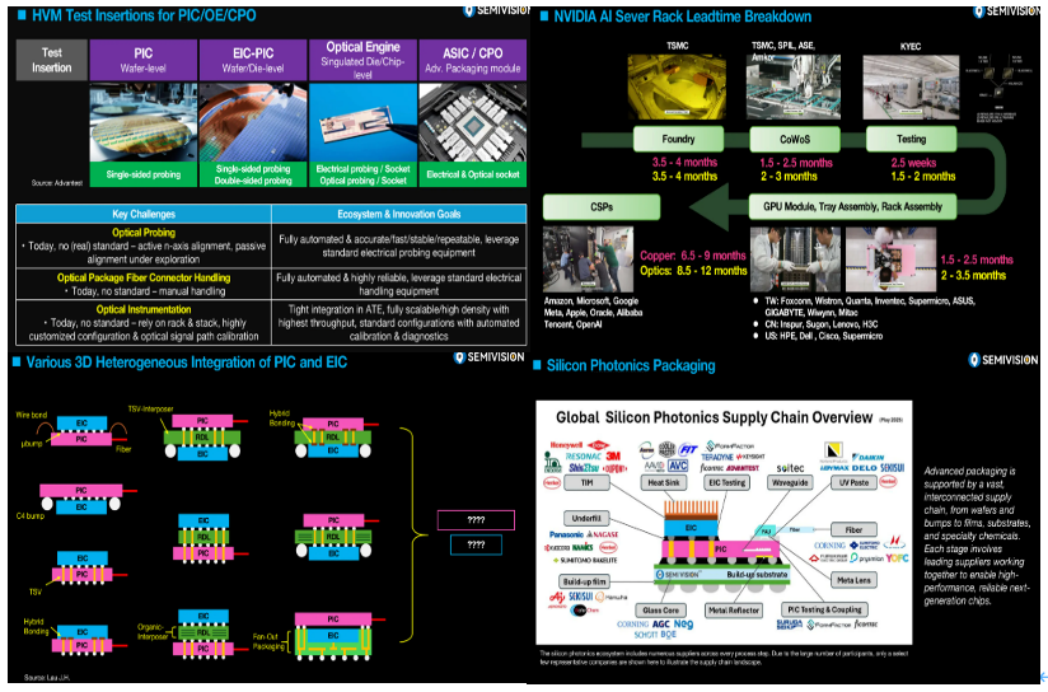

《光电CPO封装测试的挑战与未来AI产业发展》

SemiVision创始人陈熙先生

SemiVision作为活跃在光电芯片领域一线的媒体,陈熙先生以独特的专业视角阐述了AI算力基础和数据中心端光电共封装模块的强劲需求,尤其是在AI 市场增长投资与驱动一节,将其比作一个环,Nvidia投资给人工智能公司OpenAI,然后OpenAI向ORACLE购买算力,ORACLE再向NVIDIA购买算力机组,最终实现算力、云服务商和芯片厂商三方共同发展。

SemiVision全新视角解读光电共封装市场趋势

同样陈熙先生也指出在未来算力将从Scale up\out逐渐发展为Scale across,以英伟达算力机组为例,BlackWell和下一代Rubin均采用Spectrum-XGS (CPO)以太网平台技术,这一突破性网络解决方案致力于破解分布式AI计算中的跨地域连接瓶颈,通过创新的“跨区域扩展(scale-across)”架构,将分散于全球不同地域的数据中心整合为一台具有统一算力资源的“AI超级工厂”。

第二节陈熙先生聚焦于PIC(Photonics IC)、OE(Optical Engine)CPO(Co-Packaged Optics)测试环节,提出目前在晶圆级、芯片级和封装级PIC\OE\CPO测试存在诸多挑战,例如光学探针卡尚无业界标准,光学封装光纤测试分选机也大体依赖手动化测试;尤其是面对EIC+PIC光电混合封装其自动化测试也存在很多客制化,精密光路校准的业界难题,仍需设备商进一步开发。再叠加3D封装和异构集成存在纷繁复杂的多样堆叠互联变体,晶圆级测试、裸die中测等环节都存在不小的挑战,而且诸多的封装形式和芯片种类也会有散热、带宽、分立器件供应等诸多亟需攻克的难题。

SemiVision深度解读3D先进封装和硅光产业链

《面向人工智能世纪的光互连技术与光计算芯粒 》

新加坡Creideas Technologies Pte. Ltd. 合伙人兼首席技术官林福江教授

新加坡Creideas Technologies Pte. Ltd. 合伙人兼首席技术官林福江教授在《面向人工智能世纪的光互连技术与光计算芯粒 》中深入分析了CMOS技术在面对AI算力芯片时的诸多瓶颈,例如3nm工艺节点光刻复杂度激增,其制造成本大幅提升;算力机组端则面临功耗墙难题,训练千亿参数大模型时单机柜功耗可达30kW;最大问题还是互连延迟和带宽瓶颈,铜互连在10mm距离上的信号延迟达100ps,HBM内存与逻辑芯片间的数据传输带宽受限于256GB/s,光互连迫在眉睫。

Creideas Tech详解光互连技术发展

同时林教授还分享了光互连技术中高速电光调制器、PIC电路接收器创新点等议题,尤其是硅光新时代基底--薄膜铌酸锂调制器可以实现100GHz和0.5V·cm半波电压,较传统体材料性能提升10倍,支持800Gbps PAM4光信号生成,功耗降低至5fJ/bit级别;同时也介绍了异质集成Ge/Si雪崩探测器,多维复用解调芯片,硅基微环调制器集成等芯片器件的行业进展,同时也提出了目前玻璃基板光电共封装中的三大难题:超低损耗光波导,三维异构集成和热光稳定性控制。并且最后引出全光计算和存内计算融合这一全新课题,通过光神经网络加速以突破单算力瓶颈,融合非易失性光子存储器,支持全光学链路直接存内计算,达到近存光计算架构,即通过3D集成技术将铌酸锂调制器与HBM内存堆叠,实现光信号与存储数据的原位处理,有望将ResNet-50等模型的能效比提升至100TOTOPS/W量级。

Creideas Tech引出光计算芯粒产业难点

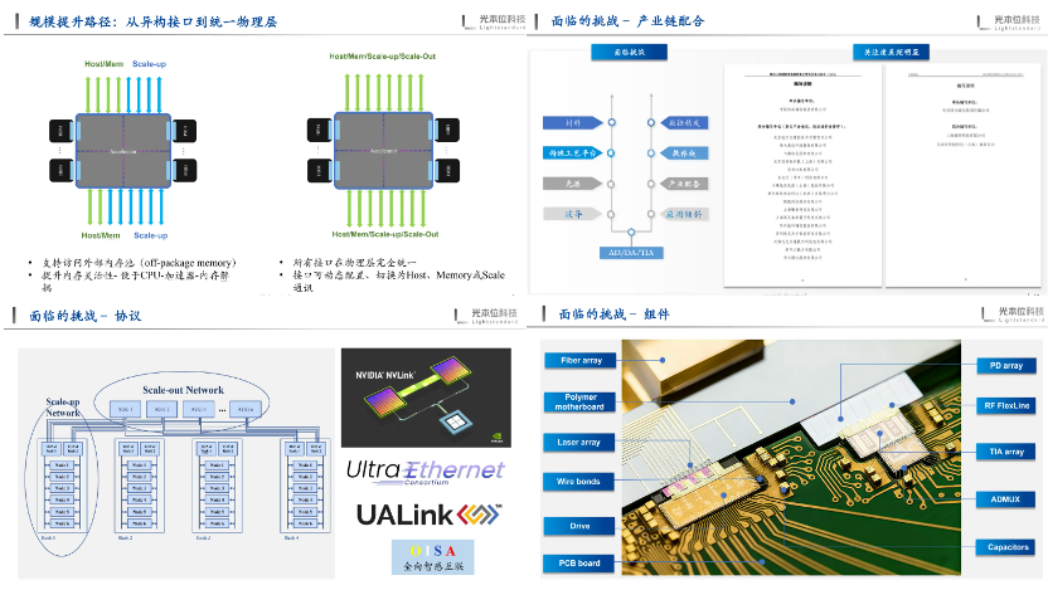

《光计算系统重构智算基建新范式 》

光本位智能科技产品与市场副总裁姚金鑫先生

光本位智能科技产品与市场副总裁姚金鑫先生则向业界分享了全光学计算系统路径的深入探究,目前电子IC面临单核算力物理极限和多核互联效率瓶颈,而光子计算系统可以越过硅基电子芯片的束缚,通过PCM+Crossbar这一技术路线,将点算力单元尺寸微缩,封装难度大大降低,并且材料端具有非易失性,所以维持功耗为零,实现存算一体,打破“存储墙”限制;同时引入波分复用技术,将进一步提升单芯片算力;通过将异构内存接口统一到物理层,极大规模提升数据路径带宽,使得内存灵活性大大提升。

光本位科技解构全光计算设计

光本位科技解构全光计算设计

最后光本科科技作为国内屈指可数的专注于光智算的科创企业,又分享了构建全光大规模AI计算的下一代颠覆式平台系统愿景,同时也指出产业界在光学组件封装和跨域算力互联存在诸多协议和网络的挑战。

光本科科技打破存储墙和功耗墙瓶颈探究

《硅光微环调制器与大容量光子互连芯片 》

松山湖实验室的张巍巍博士

来自松山湖实验室的张巍巍博士在会议分享了有关于微环WDM调制器、200G band 硅光子调制器、硅光子I\O芯粒等业界前沿技术。详细解释了硅光子MOS工艺,松山湖实验室所设计出的 MOS MZI调制器可以实现超高速>64GHz调制,同Intel调制器比较,驱动电压为1.2Vpp低1.8V,功耗为2.4pJ/bit(intel为6pJ/bit)光插损为5.8dB,Intel为6.5dB,其MOS Ring直径仅为15um,并且可以实现3-6nm的氧化物绝缘层。

松山湖实验室解码微环设计

其试验团队还首次实现硅基微环电吸收物理机制,刊发在Nature Photonics期刊,其独到的一环两用PN结微环结构为光电调制与探测协同设计,实现电光调制效率 VL=3.5Vmm,电光探测效率 R=0.8A/W。并对于PN结、MZI和MOS微环方案进行了对比研究,强调微环WDM技术是实现光电高密度互联的基础。

松山湖实验室联合莞芯半导体破解新材料破解底层制造难题

《智算时代的硅光技术趋势与挑战》

中兴光电子的赵建国博士

中兴光电子的赵建国博士分享了题目为《智算时代的硅光技术趋势与挑战》的演讲,他提到AI大模型对算力的需求依然呈现高速增长的态势,近乎每3-4个月算力需求就要翻一番,算力已成为继电力之后新一代基础资源。为了应对爆发式增长态势,算力集群化是必经之路,从单元到机组再到跨域机组集群互联,通过高效DCN和DCI互联实现更大规模、更广联接。提出DCN作为互联智算集群的内部瓶颈需要更多的光互联实现更大带宽、更低功耗和更低延迟。

中兴光电子把握硅光技术发展产业前沿动态

实现智算资源的全局调度:DCI技术,可以通过相干模块小型化和相干下沉,促进DCI开放解耦,简化相干实现相干下沉,补足IMDD带宽和传输距离限制。并且在探测器和调制器材料详细列举了三菱、清华、住友等企业的方案,得出通过异质集成突破硅光材料瓶颈,例如硅光芯片和铌酸锂晶圆级键合实现高速调制器。最后提出在硅光芯片与光源高密集成和高效耦合时碰见的行业前沿问题,并介绍了2.5D封装+异构集成和GC直接耦合、GC+微透镜、GC+反射镜等高效解决办法。

中兴光电子解密相干光和透镜技术发展

《NOEIC光电器件封装与测试平台研究进展 》

国家信息光电子创新中心的李宗阳博士

来自国家信息光电子创新中心的李宗阳博士则分享了NOEIC先进封装和测试业务能力,作为国家级光电子实验室,其拥有自动化光耦合装备,3D打印光耦合先进工艺,多通道、垂直、多透镜阵列耦合等先进技术。

NOEIC光电封测技术业界领先

NOEIC拥有精密互联(精度达±0.3μm)、性能测试(支持≥200Gbaud波特率)、发射/接收端 芯片、器件和模块设计、研发、封装、测试全栈能力,其110GHz 超高带宽电光调制器处于国内首款,国际领先水平;后续又推出了全球首发的145GHz电光调制器产品,其DC-145GHz的带内回波损耗S11≤-10dB。

NOEIC自研国产化光电共封装产品性能卓越

《CPO 与Foundry 生态系加速光电芯片产业化进程 》

逍遥科技CTO陈昇祐博士

逍遥科技CTO陈昇祐博士深入对比Broadcom与NVIDIA的CPO技术路线,指出Broadcom走演进式2.5D封装路径,而NVIDIA以3D混合键合实现接近零额外的插入损耗,并提出其向1 pJ/bit 传输功耗迈进的技术路线。陈昇祐博士强调,逍遥科技的核心竞争力在于其EDA工具如何赋能产业链各环节——从设计方案探索、版图验证、封装协同到系统级互连仿真和测试自动化,帮助供应链上下游实现高效协作与快速迭代。

逍遥科技从光电芯片设计和CPO制程解码

并且还分享了众多硅光子制造产业难点,例如LPCVD需要750-850°C高温而该制程与后续掺杂制程不兼容,可能会破坏已经掺杂好的有源器件(P-N结光电探测器),尤其是设计流程和EDPA工具上存在巨大短板,逍遥科技PIC Studio可以从设计、仿真到验证全流程提供光子集成电路一体化平台,实现传统分裂式工作流切换到统一设计工作流。其拥有流片前的 Layout vs. Schematic (LVS) 版图检查、pSim Plus 端到端光电融合仿真、pSim Plus DFE与CTLE联合均衡算法仿真与眼图分析、pSim Plus 支持支持光电组件高频紧凑模型及3D集成热串扰仿真和蒙特卡洛仿真与性能统计分析等功能。目前已经得到数十家业内头部foundries 公司和科研院所的认可与PDK 支持。

逍遥科技PIC Studio涵盖多物理场仿真,推动行业标准化共筑光电产业基础

结语

纵览本次论坛众多大咖专业深度的分享,笔者收益匪浅,AI算力单元带宽和功耗瓶颈,跨域超高速互联等需求迫使互联技术从电子学转向光电子学,最终走向纯光子链路算力的路径,是得光电子产业获得前所未有的发展契机。在2025-2030年间CPO和异质集成将会是两大核心技术落地的产业窗口期,并且产业链上游的EPDA和光学PDK等工具、热光电力等多物理场仿真软件、2.5D和3D封装工艺和材料、微环调制器等产业环节核心部分也都取得了瞩目的进展。此次湾芯展-光电芯片论坛涵盖产业链全生态,整合设计、制造、封测和光芯片全流程内容,堪称光电产业从业者的“视觉盛宴”。

*参考资料

1.《光电CPO封装测试的挑战与未来AI产业发展》

2.《面向人工智能世纪的光互连技术与光计算芯粒》

3.《光计算系统的可行路径与挑战》

4.《硅光微环调制器与大容量光子互连芯片》

5.《智算时代的硅光技术趋势与挑战》

6.《NOEIC光电器件封装与测试平台研究进展 》

7.《CPO 与Foundry 生态系加速光电芯片产业化进程 》

文末福利:免费获取最全的行业资料信息汇总!

文末也给看到这的读者们发福利啦,深芯盟编辑近期分析了光学行业产业链,Yolo的最新分析报告也免费分享给读者朋友们,欢迎大家点赞和转发,我们下期再见。

关注本公众号并回复关键词:OIF,就可以领取每期给大家分享的行业资料啦!

相关阅读