编制按:

本文核心看点:Rubin CPU+GPU的微秒级协同,Helios 3.2吨巨兽刷新规模化算力上限,与RISC-V 令通用处理逻辑与AI矩阵运算在流水线级别深度融合,谁将真正定义AI时代的算力新秩序?

知合计算AI首席科学家苏中老师CES keynote观后思考,五星推荐,欢迎留言讨论。

正文:

昨晚,圣诞假期后RVI的标准工作组刚刚结束了一场深夜讨论会。今早全靠咖啡续命,然后一边补上了拉斯维加斯CES 2026的两场重头戏——老黄(黄仁勋)和苏妈(苏姿丰)的keynote。苏妈的开场白直接定下了基调:“今晚的一切都关于AI,这毫不令人意外。”这句话不仅点出了CES 2026的主题,也精准概括了当前整个计算行业的发展方向。

Rubin架构:极致的互联带宽

老黄发布的Rubin架构展示了何为“系统级整合”的设计理念。这已不仅是芯片迭代,更是对整个计算架构的重构。

显存革命:全面搭载HBM4,带宽达到惊人的22TB/s。这相当于为数据传输建成了超高速专用通道,大幅缓解了大模型推理中的“访存墙”挑战。

双核深度协同:全新的Vera CPU采用3nm工艺的Olympus架构,与Rubin GPU实现深度绑定。这种强耦合的“CPU+GPU”设计,让数据处理延迟降至微秒级别,为实时AI应用打开了新可能。

互连系统创新:NVLink 6.0实现了单机柜内数千颗核心的实时协同,英伟达正将整个数据中心变成一个巨大的“虚拟处理器”,展现出纵向集成的系统级威力。

老黄展示的另一项硬核技术是Vera CPU搭载的Olympus核心,它基于ARMv9.2-A架构,引入了ARM下一代向量指令集扩展SVE2(第二代可伸缩向量扩展)和FP8DOT2指令。SVE2使其在处理加密与复杂数据流时快如闪电,而FP8DOT2则让CPU也能在大模型推理主流的FP8格式上贡献显著算力。

Helios平台:惊人的“体重”与开放生态

苏妈在她的keynote中展现了AMD不同的设计思路——模块化与规模化并行推进。她重点介绍了AMD的Helios平台,这一基于2nm和3nm工艺的系统整合了HBM4技术,在单个机架内容纳了多达72个GPU。更令人印象深刻的是现场展示的实物:“台上就有一台!”——这台双倍宽度的机器重达近7000磅(约3.2吨)。这种硬件层面的巨大投入,体现了AMD在高性能计算领域追求极致规模化的决心。与英伟达的纵向集成不同,AMD依然在强调其ROCm开放生态和Chiplet(芯粒)的灵活性,以更高算力密度和更开放适配性来构建差异化优势。

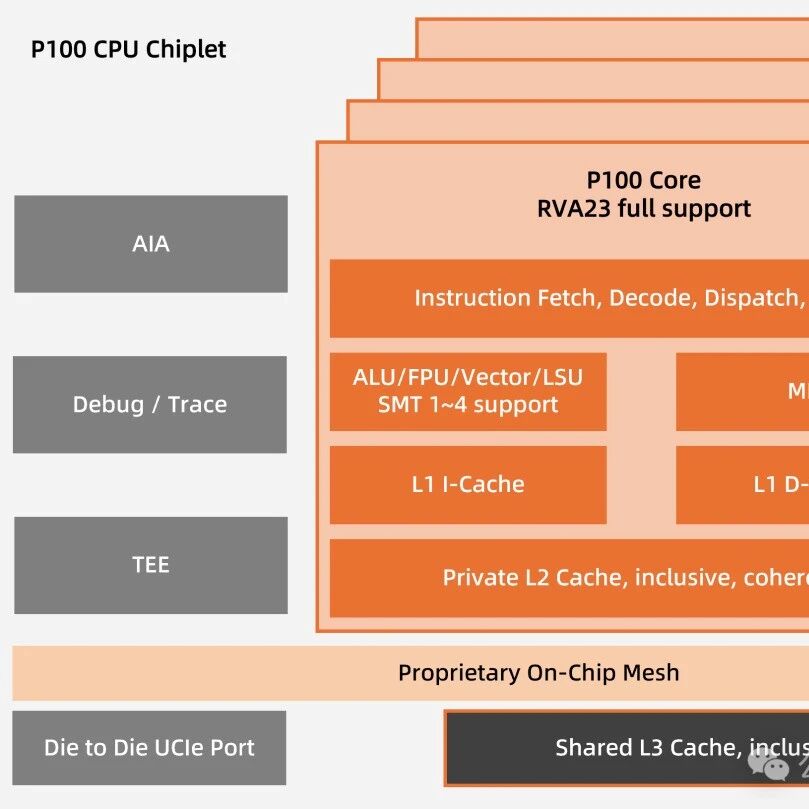

看完这两场精彩的展示,我不禁回想起上个月参与组织的珠海2025 RISC-V并行计算分论坛。当“一切关于AI”成为共识,如何实现AI计算的高效化与普及化,就成为各技术架构必须回答的问题。在珠海的论坛上,我们探讨的正是如何发挥开放架构在并行计算中的独特优势。

如果说Rubin的核心是Tensor Core,那么RISC-V的突破口则在于矩阵扩展(Matrix Extension)。英伟达在ARM架构中融入SVE2,RISC-V社区正在制定的IME/VME/AME(集成矩阵扩展)背后逻辑是相通的:在论坛上,阿里达摩院项晓燕博士详细解读了RISC-V矩阵扩展指令的最新进展。

珠海论坛的另一核心议题是异构并行。清华大学尹首一院长与何虎副教授分别从高算力芯片路径与开源GPGPU设计角度,阐释了如何让RISC-V核心与专用加速器高效协同。这一思路与Rubin的Vera CPU + GPU组合不谋而合。

RISC-V并行计算的多元未来

当前行业中CPU+GPU协同模式已相当成熟,而RISC-V则提供了另一种可能性——更紧密的异构集成,在统一架构下协调不同计算单元,减少数据搬运,提升整体效率。Rubin实现了CPU+GPU的微秒级协同,但它们仍属于两个不同的指令集体系。RISC-V的愿景或可以是“原生异构”,让通用处理逻辑与AI矩阵运算在流水线级别深度融合,走向真正的“通推一体”。

英伟达和AMD当前主攻昂贵的数据中心,AI的未来则无处不在。从数据中心的深度整合,到边缘侧(如具身智能、低空飞行器、IoT、穿戴设备等)的灵活定制,RISC-V开放架构允许每条技术路径依场景寻找最优解,实现从边缘到中心的AI场景全覆盖。

“One more thing”

在老黄的报告中,他特别提到一个值得关注的趋势:2025 年是 AI 史上的一个分水岭:以 DeepSeek、Qwen等为代表的中国开源大模型力量,正在打破硅谷对“最强模型”的垄断。AI 的未来或不在于谁的围墙更高,而在于谁的生态更深。当全球开发者可以以更低的成本调用这些“世界级”的开源模型时,真正的物理AI 时代(智能汽车、人形机器人)或才会全面到来。这或许也从一个侧面印证了开源力量的崛起与多元技术路径的价值。

苏中| 知合计算 AI 首席科学家

2026年1月6日,于CES keynote观后思考

来源:RVEI秘书处