在人工智能深度重塑产业格局的当下,设备端侧作为智能落地的 “最后一公里”,正面临实时响应、能耗控制、数据隐私与成本优化的多重挑战。传统处理方案在算力天花板、高功耗弊端及定制化适配难题前渐显乏力。破局之道,在于技术的深度融合与创新的敏捷迭代。隼瞻科技于第五届 RISC-V 中国峰会上重磅推出了“智翼” 系列端侧 AI 融合处理器解决方案,为行业突破困局提供了极具前瞻性和革命性的解题思路。

“智翼”系列端侧 AI 融合解决方案以先进的RISC-V DSA (Domain Specific Architecture)架构为基础,借助 ArchitStudio处理器敏捷开发平台的强大能力,可快速高效地进行处理器定制与优化。搭配可灵活定制适配多元模型的NPU模块,能够根据不同应用场景和算法,精准匹配各类 AI 模型,实现高效的计算处理。

01

“智翼” 核心

三位一体的DSA架构

端侧AI应用多样化特征决定了这是一个天然的DSA场景,而“智翼”解决方案的核心竞争力在于其独特的“RISC-V DSA + ArchitStudio敏捷开发平台 + NPU阵列” 三位一体架构带来了强大的DSA定制功能,客户可以根据不同的应用场景和算法需求灵活选择不同的模块单元组合:

强大且高效的标量基础

隼瞻科技高性能RISC-V处理器核

提供坚实的标量核心运算单元,高效运行操 作系统及任务调度等指令

覆盖从超低功耗MCU到高性能多核HPC的完整IP谱系,满足不同场景需求

面向领域的矢量加速

基于ArchitStudio设计的“紧耦合”矢量处理单元

利用隼瞻自研的ArchitStudio DSA敏捷开发平台,可快速为特定AI算法(如激活函数、池化、编解码,前处理后处理等)定制高性能VPU指令

提供应对AI算法快速迭代的灵活性,显著提升特定矢量运算效率

高密度的AI算力

高弹性可配置的NPU矩阵计算单元

统一硬件架构:能够从容应对不同 AI 模型对硬件架构的复杂性要求。无论是常见的卷积神经网络,还是循环神经网络,以及新出现的各类大语言多模态模型算法,统一的硬件架构都能高效适配,无需为不同模型单独设计硬件,大大降低了硬件设计的复杂度和成本

高效的数据搬移:有效提高 MAC(乘加运算单元)利用率。通过优化数据传输路径和排列重组方式,减少数据在存储和处理单元之间的搬移时间和能耗,让 MAC 能够更高效地进行运算,充分发挥其性能,提升整体 AI 处理效率

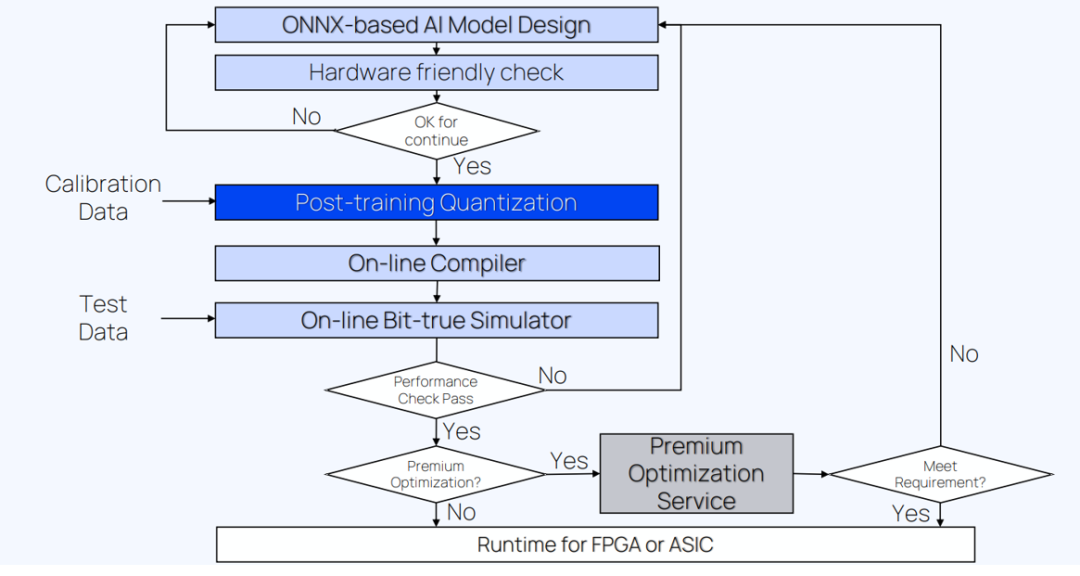

一键式的 AI 模型部署:借助一键式的软件栈,实现模型的快速部署与适配。开发者无需繁琐的配置和调试过程,只需简单操作,就能将训练好的 AI 模型部署到智翼解决方案中,显著缩短了产品的开发周期,提高了开发效率

02

“智翼” 优势

敏捷、高效、定制化

高密度的AI算力

ArchitStudio平台彻底革新传统DSA设计流程。通过“RISCAL”架构描述语言和智能引擎,实现:

“一键式”生成 定制化处理器IP包(RTL代码、验证环境、编译器、工具链等)

大幅降低 处理器设计技术门槛、项目复杂度和人力投入

显著缩短 从算法定义到芯片实现的周期,快速响应市场需求

极致能效比

专有架构设计和深度优化,保障在同等算力下实现极低面积与极小功耗,是电池供电和空间受限设备的理想选择

深度场景定制

基于RISC-V DSA的CPU/VPU可灵活裁剪、扩展,结合NPU的弹性定制能力,能够精准匹配客户专有场景与核心算法,实现最优性能功耗比

完善工具链与大模型支持

提供从EDA工具、软件开发套件到主流CNN/LLM/VLM模型支持库的完整生态,助力客户快速产品化

03

“智翼” 蓝图

全场景覆盖的算力阶梯

轻羽

超低功耗CPU+ 0.1-0.5TOPS NPU

面向超低功耗Always-On感知

如语音唤醒、人脸检测

翔风

高能效CPU + 0.5-2TOPS NPU

面向实时交互场景处理

如目标识别、手势交互、AI降噪

凌云

高性能CPU + 1-4TOPS NPU

面向多种复杂智能场景

如多路视频分析、高级机器视觉

御空

HPC级CPU + 4-64TOPS NPU

面向端侧大模型(LLM/VLM)部署、高端机器人、无人机等

04

“智翼” 落地实践

极低成本、超低功耗的端侧AI融合处理器

透过独特架构NPU设计与业界领先的低逻辑门数技术,隼瞻科技设计了一款极低面积极小功耗AI融合处理器系统,成功达成针对人脸侦测的 25 毫瓦(mW)Always-On 极低功耗运算需求。该解决方案具备精准感知用户动态的能力,能够实现人脸侦测、姿态侦测、手势识别等智能功能,显著提升设备的能源效率与信息安全性,并且已顺利导入量产。

立足智翼方案的发布节点,隼瞻科技将进一步深耕 RISC-V 与端侧 AI 的融合创新赛道。公司计划携手生态合作伙伴,共同推动相关技术实现规模化落地,让智能因子深度渗透到生活与产业的每一个场景。通过持续的技术突破与创新实践,隼瞻科技致力于为全球用户打造更优质的应用体验,不仅立志成为端侧 AI 革命的核心推动者,更要在全球创新舞台上,书写属于中国科技的精彩篇章。

关于隼瞻科技

隼瞻科技是一家聚焦DSA处理器设计创新的高科技企业,致力于打造基于 DSA(专用指令集架构)的RISC-V技术体系。公司依托三大核心技术板块 —— 自主研发的RISC-V处理器核、高效敏捷的DSA处理器敏捷开发平台,以及可灵活定制适配多元模型的NPU模块,构建起高度模块化的解决方案体系。通过自由组合的产品架构,精准响应AIOT、DSP、5G 网络、汽车电子、人工智能等复杂芯片场景的差异化需求,为行业提供兼具性能与灵活性的解决方案。