关注公众号,点击公众号主页右上角“ · · · ”,设置星标,实时关注旺材芯片最新资讯

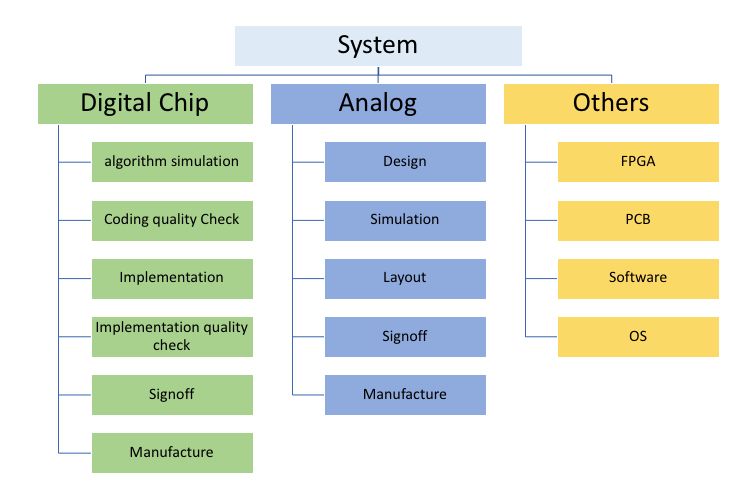

在各方助力下,集成电路成了时代热点,有大量文章在写芯片设计之复杂之困难,老驴打算从EDA 使用角度捋一遍芯片设计流程。在老驴画出第一副图之后,发现熟知的只有数字电路部分的一小段,对系统、软件及上层应用完全无知,只能归类为Others。

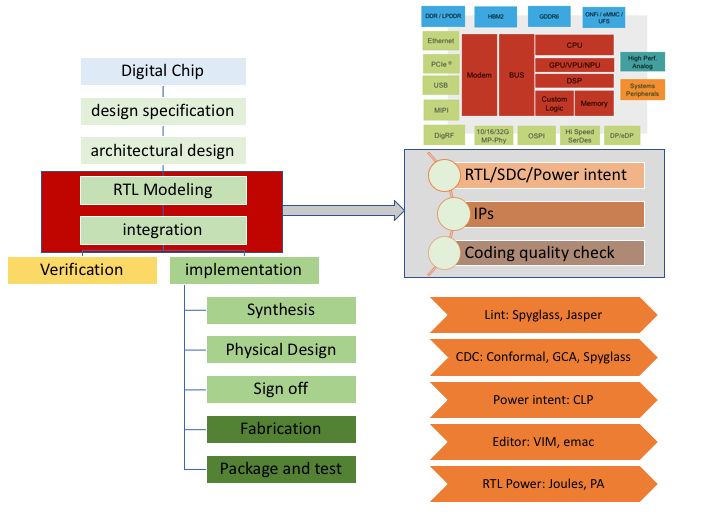

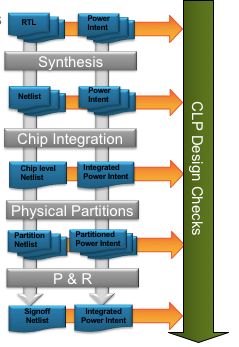

编辑器:VIM, emac; Lint : RTL 质量检查,Spyglass, Jasper; CDC: SDC 质量检查,Spyglass, Conformal, GCA; CPF/1801: power intent 质量检查,CLP; Power: RTL 级功耗分析,Joules, PA; 仿真器:C, S, M 三家都有各自的仿真工具; 综合:Genus, DC;

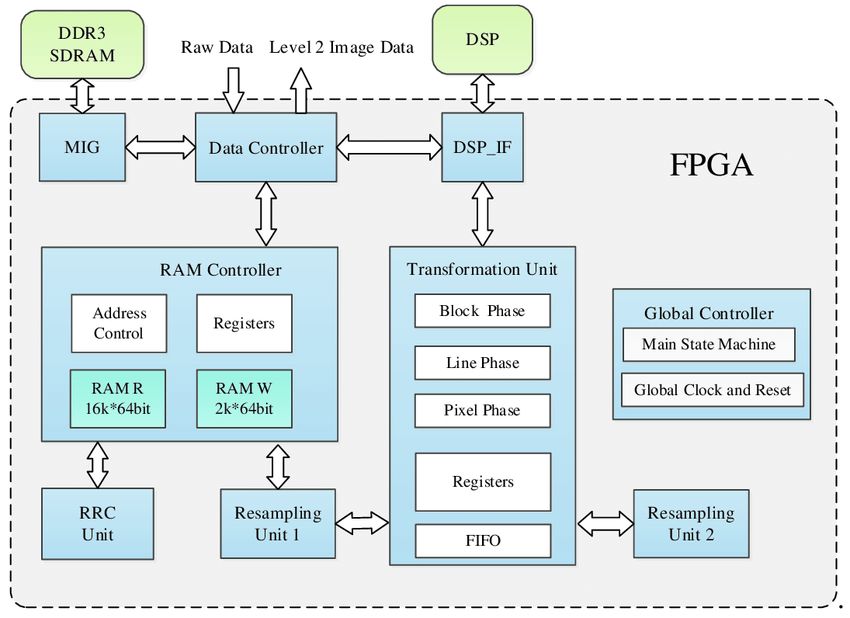

语言:各种脚本语言之外,C/C++, SystemVerilog, Verilog; 协议:各种接口协议,各种通信协议,各种总线协议; 工具:动态仿真工具,静态仿真工具,FPGA, Emulator;

Static Verification: Jasper Gold 是C 家新近推出的静态验证工具,驴所理解的静态验证是基于断言的验证方法学,所谓静态即不需要输入测试激励,验证过程是纯数学行为。 Dynamic Verification: Xcelium 是C 家的动态验证工具,驴所理解的动态验证是基于UVM 的验证方法学,通过输入测试激励,监控仿真结果,分析覆盖率完成功能验证。 Emulator: 硬件仿真加速器,粗暴理解:有debug 功能的集成了丰富接口的巨型可编程阵列;特点:超高速验证、支持系统软件调试。帕拉丁是C 家在验证领域的明星产品,是行业翘楚,据说常有钦差莅临硅厂在帕拉丁前驻足良久,赏其外形之美,赞其功能之强。 Verification IP: 验证需要各种验证模型,各种IP, 各种总线,各种高速接口。

硅农:Innovus 请解析A 文件,按设定目标做个功耗最优的结果; Innovus: 已读取目标文件,根据设计数据分析,本设计大概需要250G 内存,在5小时内完成,请选择任务完成后是否自动进入后续程序......

来源:陌上风骑驴看IC

专心 专业 专注

分布图领取