使用单一按钮推进电路至下一个逻辑状态的应用非常广泛。通常状态只有“开”(on)与“关”(off)两种,但也可以有更多状态。该电路的核心是一个可切换的触发器(toggle flip-flop),若需要更多状态,则可使用计数器或移位寄存器,这些组件会对频率信号的变化作出反应。

一个理想的电路必须可以防止机械按钮的触点抖动,避免每次按下和释放按钮时产生多个“频率”脉冲。此外,最好能在电源启动时初始化为特定状态,并在用户按下按钮的瞬间立即触发状态改变。图1所示的基本电路就具备这些特性。

图1:U1是一个肖特基反相器,U2为D型触发器。图中所用二极管为小信号肖特基二极管。按钮为常开型。电阻与电容的具体数值请参见正文中的说明。

电源开启与初始化行为

当VDD电源断电并放电后,肖特基二极管会将电容C1与C2放电至接近0V。时间常数R1C1应该设计为比电源开启时间长10倍以上,以确保电路在开机时会将U2的Q输出清零(reset)。

此外,于电源启动时,U1的输出会先为逻辑高电平,然后经由R2对C2充电而转为低电平。由于U2触发器的作用时序为由低电平到高电平,这使得Q保持初始化为低电平。R2C2的时间常数应设计在约1秒量级。

消除触点抖动的设计细节

R3为可选组件,用来限制当常开按钮被按下时C2初始放电的电流。如果使用R3,其阻值应设计使得在触点抖动期间(约10毫秒内)能几乎完全放电C2。

C2与R2,加上肖特基反相器U1,共同组成一个防触点抖动结构,能防止抖动造成额外的触发信号,否则会误触发触发器U2。当按钮释放、R2开始对C2充电后,若此时再次按下按钮,U2不会再被触发,因为U1的输出仍为高电平,无法从低电平转换为高电平来触发U2,这是设计R2C2时间常数不宜过大的理由之一。

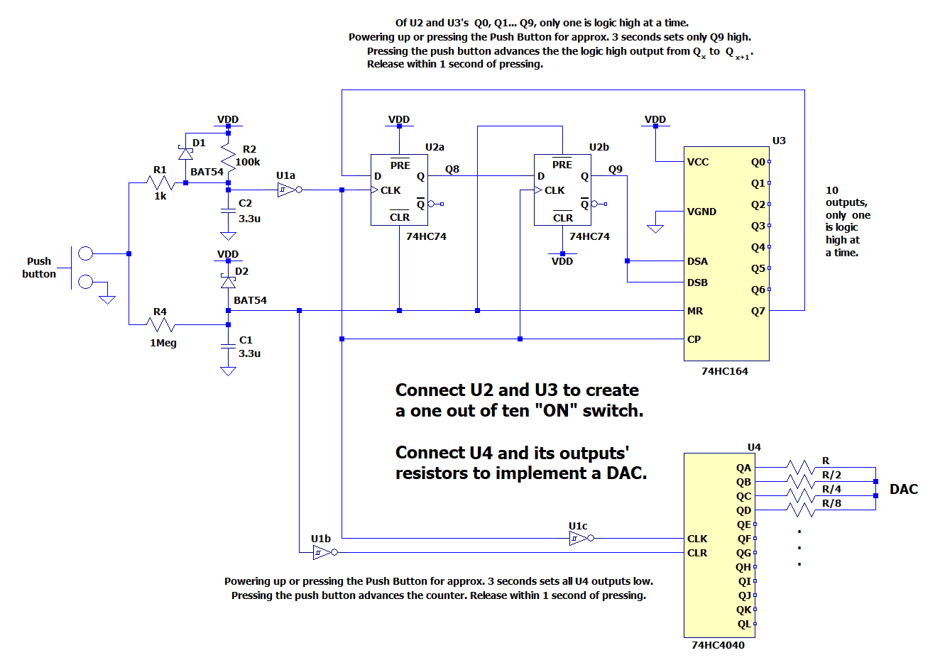

图2显示如何将图1的基本电路延伸为一个10位的多状态开关,该开关在任一时刻仅有一个输出为高电平,也可以扩展作为数模转换器(DAC)。

图2:一个10位开关电路实操案例,每次仅有一个高电平输出,也可以扩展为DAC。

若需要的状态少于10个,可将U2a的D输入连接至U3的其他输出引脚。对于DAC应用,可通过12个电阻将分辨率扩展至12位。虽然理论上能做到12位,但即使采用0.1%精度的电阻,其单调性仍会低于12位,而实际精度会更低。为避免对输出造成过重负载,各电阻阻值应不低于10kΩ。