1、点对点直连优先

适用场景:PCIe/USB超高速信号

操作要点:路径长度差<5mil,过孔数≤1个,差分对间距恒定

2、菊花链拓扑适配低速总线

适用场景:I²C/SPI/CAN

操作要点:分支长度差<50mil,末端加1kΩ上拉电阻

3、星型拓扑控负载均衡

适用场景:多负载总线(如RGB LED驱动)

操作要点:主干线宽+20%,分支等长误差<2mil

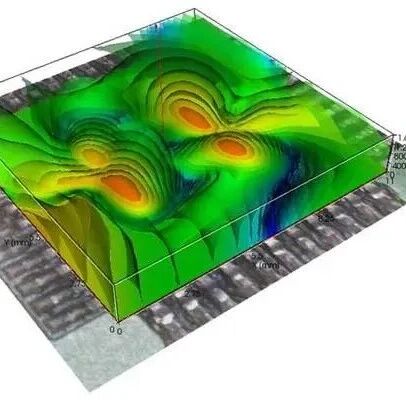

4、蛇形线等长补偿技术

适用场景:DDR地址/控制信号

操作要点:振幅≤2倍线宽,相位误差<5mil,间距≥3倍线宽

5、端接电阻降反射策略

适用场景:单端50Ω/差分100Ω信号

操作要点:电阻距接收端≤50mil,阻抗匹配误差±2%

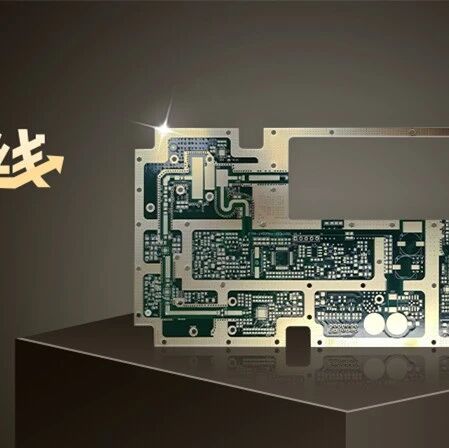

6、分层隔离提升隔离度

适用场景:模拟/数字混合电路

操作要点:敏感信号布内层,与电源层间距≤4mil,隔离度提升18dB

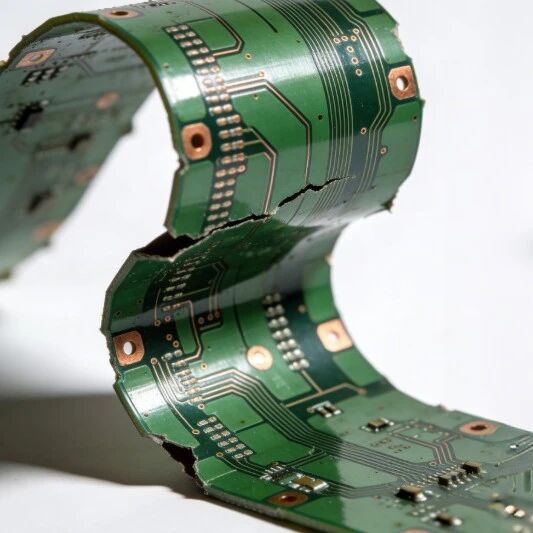

7、3W原则升级版

适用场景:高频平行走线(>500MHz)

操作要点:间距扩展至5倍线宽,串扰衰减达15dB