日本 Rapidus 公司在 2nm 工艺研发上持续推进,其节点逻辑密度数据首次公开,且明显与台积电 N2 工艺相当。

在 2nm 技术竞赛中,Rapidus 极有可能与台积电展开竞争,因其逻辑密度已达到同等水平。

近几个月来,Rapidus 备受关注,主要因其作为日本半导体领域的领军企业,连英伟达也对其表示兴趣。该公司正研发代号为 “2HP” 的尖端 2nm 工艺,据 @Kurnalsalts 透露,2HP 的逻辑密度与台积电 N2 工艺相近,更重要的是,其密度大幅领先英特尔 18A 工艺。这表明 Rapidus 的工艺节点有望成为行业内最具竞争力的技术之一,以 “黑马” 之姿闯入半导体赛道。

尽管英特尔的工艺节点标称尺寸更小,但其 18A 工艺的密度据称为 184.21 MTr/mm²。这主要是因为 18A 在基准测试中使用了高密度库,而另一个关键因素在于,英特尔采用 BSPDN(背面供电网络)技术,占用了部分正面金属层,导致高密度库测量时密度数值下降。由于英特尔更关注单位功耗下的性能指标,高密度并非其核心目标,尤其是 18A 工艺主要服务于内部需求。

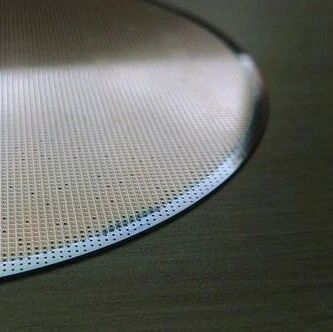

如今,Rapidus 2HP 的密度数据无疑彰显了其在半导体行业的重大进展。更值得关注的是,这家日本企业采用了单晶圆前端工艺 —— 这种独特方案专注于针对小批量生产进行工艺调试,再通过规模优化提升最终成果。Rapidus 计划于 2026 年第一季度向客户提供 2nm PDK(物理设计套件),从现有信息来看,该工艺节点前景可观。

欢迎加入 EETOP 微信群

TI 最新架构DSP+MCU (原厂免费培训)

(线下实操)

北京(9 月 11日)

TI 专家手把手指导您使用 C2000™ 系列产品