突破电互连瓶颈

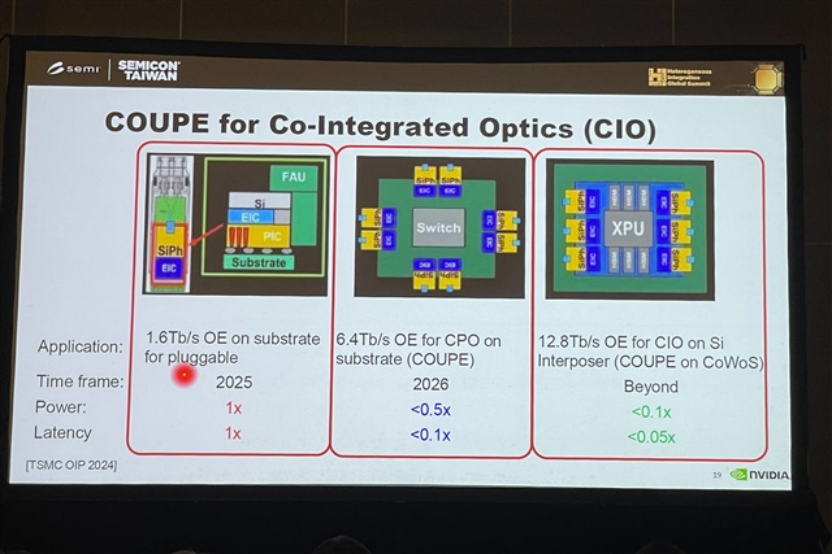

在 2025 年中国台湾半导体展上,英伟达高级研究科学家 Nandish Mehta 博士介绍了公司在共集成光学(co-integrated optics, CIO)领域的研究成果,并将其定位为共封装光学(co-packaged optics, CPO)之后,突破电互连技术局限的下一代方案。

数十年来,电信号传输一直是性能提升的核心路径,但如今已面临功耗、密度与传输距离的三重制约。

图片来源:电子时报(Digitimes)

英伟达早期的 CPO 方案通过在中介层上集成光引擎与交换机,已展现出切实优势:与传统链路相比,功耗降低至多 3 倍,信号完整性提升 63 倍,同时支持每平方毫米约 2 太比特 / 秒(Tb/s)的密度。

CIO 的核心优势

CIO 在 CPO 基础上进一步升级,将硅光子学(silicon photonics)器件直接与计算系统级芯片(SoC)共置于同一中介层上 —— 这一设计可最小化电传输距离,并实现更精细的带宽粒度控制。Mehta 表示,该方案为技术演进提供了可靠路径,但也在三个核心领域带来新挑战:设计效率、功耗控制与成本优化。

为实现高效设计与高密度集成,英伟达正研发基于微环谐振器(microring resonators, MRRs)的密集波分复用(dense wavelength division multiplexing, DWDM)链路。微环谐振器具备体积小、选频性强、能效高的特点,非常适配 CIO 架构需求。

图片来源:电子时报(Digitimes)

同时,英伟达还在开发电集成电路与光子集成电路之间的铜 - 铜混合键合(copper-copper hybrid bonding)技术。该技术可实现超高密度布线与表面光栅耦合器设计,在相同数据吞吐量下,电容降低且功耗节省约 30%。

功耗与成本优化策略

在功耗控制方面,Mehta 提到英伟达正采用时钟转发光链路(clock-forwarded optical links)技术。通过将并行时钟与数据一同传输,接收端无需再恢复时序信息,此举可降低抖动敏感性、简化电路设计并减少功耗。

图片来源:电子时报(Digitimes)

成本优化方面,英伟达正评估多项措施:

·研发低成本光纤阵列单元(fiber array unit, FAU)封装,以简化系统集成并提升可扩展性;

·瞄准分布反馈(distributed feedback, DFB)激光器阵列,实现紧凑型多波长工作,减少对体积更大的外部激光模块的依赖;

·热管理层面,建议采用系统级冷却方案,替代会增加成本与复杂度的片上热电冷却器(thermoelectric coolers, TECs);

·潜在成本节省点还包括用标准单模光纤替代保偏光纤—— 此举不会对性能造成显著影响。

图片来源:电子时报(Digitimes)

待突破的技术障碍

偏振管理仍是当前的核心技术挑战。英伟达正研究偏振分集接收器与偏振不敏感架构,以确保无论输入偏振状态如何,都能实现稳定性能。

Mehta 在演讲结尾指出,CIO 是具备长期可行性的光技术方向,并强调 “协同设计” 的重要性 —— 需同时考量光学、封装与系统架构三大维度。

尽管目前相关研究仍处于研发阶段,但英伟达预计,随着 AI 系统需求的持续升级,CIO 将能实现更低延迟、更高带宽密度与更优能效的目标。

原文标题:

SEMICON Taiwan 2025: Nvidia shifts optical roadmap from co-packaged to co-integrated optics

原文媒体:digitimes asia

芯启未来,智创生态