Part 01

前言

个人觉得,这个问题的答案并非简单的非高即低。实际上,开关频率的选择是妥协的结果吧,我们需要在多个关键性能指标之间寻求最佳平衡点才行,接下来我们就聊聊这个问题。

Part 02

促使我们提高开关频率的诱惑是什么?

第一个诱惑就是提高开关频率能实现无源器件的小型化。这是提高开关频率最直接、最显著的好处。

1.电感L的减小:根据电感的基本伏秒平衡公式

我们可以看到,在输入/输出电压和期望的电感纹波电流△IL都确定的情况下,所需的电感值L与开关频率fsw成反比。这意味着,如果我们将频率提高一倍,理论上所需的电感值就可以减半。更小的感值意味着更少的线圈匝数和更小的磁芯体积,从而直接实现电感器物理尺寸的缩小和成本的降低。

2.电容C的减小:开关频率越高,对输出电容进行充电的次数就越频繁。在每个开关周期之间,输出电压下降的总有效时间会变得更短。因此,为了维持相同的输出电压纹波△Vout,我们不再需要那么大的电容来平滑电压。这使得我们可以选用容值更小、体积更小的输入和输出电容。

除了能让无源器件体积更小之外,提高开关频率还有啥好处?答案是更优秀的纹波与动态响应。

1.更低的输出纹波:在电感和电容值已经确定的情况下,提高开关频率意味着每个周期内电感充放电和电容充放电的时间缩短,其电流和电压的波动幅度也就是纹波自然会变得更小。

2.更快的动态响应:电源的反馈控制环路对输出变化的响应速度,直接受限于开关频率。频率越高,控制环路在一个单位时间内进行采样和调整的次数就越多。当负载电流发生突变时,高频工作的电源能够更快地做出反应,稳定输出电压,从而实现更小的电压过冲和下冲。

Part 03

提高开关频率的代价是啥?

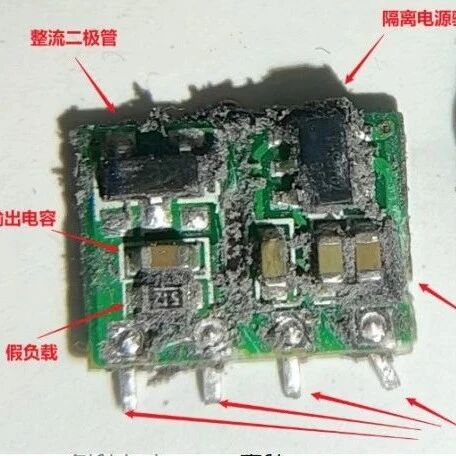

在这个短暂的切换时间内,MOSFET上同时存在着较大的电压和电流,其瞬时功耗(P =V×I)非常高。开关损耗与开关频率成正比。每次开关都会产生一次这样的损耗,频率越高,单位时间内开关的次数越多,累积的总开关损耗就越大。其简化公式为

驱动损耗更高:为了让MOSFET开关,需要对其栅极电容进行反复充放电。这部分损耗的功率与开关频率成正比:Pgate = Qg× Vdrv× fsw。

电感磁芯损耗更高:电感磁芯在交变磁场下会产生磁滞损耗和涡流损耗,这两种损耗都随着频率的升高而显著增加。

同步BUCK体二极管损耗更高:在同步BUCK电路的死区时间内,MOSFET的体二极管会导通,其损耗也与频率相关。

所有这些与频率相关的损耗最终都会转化为热量,导致芯片和电感等元器件的温度急剧上升。为了控制温度,这时候就需要增加散热器或采用铝壳散热等更复杂的散热设计,这在一定程度上又抵消了元器件小型化带来的体积优势。更重要的是,大量的能量以热的形式被浪费掉,直接导致电源的整体效率下降。

当然,开关频率越高,EMC问题也越难搞呀!

那开关频率该怎么选呢?当空间和尺寸是首要矛盾时,这时候选择更高的开关频率来减少器件的整体体积,当然还需要投入更多的精力去优化散热设计和选择低损耗的元器件。