缝合过孔 (Stitching Via) 是 PCB 表层常见的结构。如果正确使用覆铜,理想情况下他们会计算出合适的缝合过孔间距,使过孔阵列能够抑制串扰/干扰。另一种选择是将其用作层间多个并联连接,从而提供低电阻和低阻抗,从而提供高直流或交流电流。

在本指南中,我将介绍缝合过孔的一些标准用途以及它们在PCB中的使用时机。由于与覆铜有关,一些设计师对PCB设计的这一方面可能存在争议,而覆铜通常被认为在大多数设计中是不必要的。无论您对覆铜有何看法,缝合过孔在低频和高频PCB中都具有重要的用途。

PCB 中缝合过孔的基础知识

缝合过孔的结构很简单:它们是周期性的过孔阵列,通常通过PCB叠层接地。通过这种方式,它们在多层接地网络之间建立连接。需要注意的是,过孔阵列的一种用途是跨层电源连接(见下文)。这些结构在射频设计中也具有重要的用途,这有时会导致缝合过孔被误用。

让我们更详细地了解一下这些用途:

典型用途:连接地面

缝合过孔的标准用途是连接多层接地。在多层PCB中,通常会将多个铜箔区域分配给同一个接地网络。缝合过孔是一种非常有用的工具,可以连接所有接地区域,并确保沿PCB参考平面传播的任何回流电流的阻抗尽可能小。

通过通孔实现层转换

这正是连接到GND的缝合过孔真正展现其价值的地方。数字电路和射频电路中的层间过渡需要有清晰的接地参考,以控制信号沿PCB互连线的传播。进行层间过渡时,缝合过孔阵列中附近的过孔可以发挥与走线下方接地平面相同的作用。

一般来说,如果在PCB上放置缝合过孔阵列,则在信号过孔的层过渡附近很可能有一个缝合过孔。在某些情况下,这种做法可能行得通,您可能不必担心过孔过渡区域内的噪声发射或对噪声的敏感性。在信号过孔附近放置一个接地的缝合过孔应该足以抑制噪声,尤其是对于慢速GPIO、I2C、UART或其他慢速数字协议(低频模拟信号也同样如此)。

对于高速数字和射频,情况有所不同,需要在信号过孔附近专门设计一个缝合过孔阵列。缝合过孔阵列旨在为沿缝合过孔边缘感应的返回电流提供低阻抗路径。在这些转换中放置缝合过孔的另一个原因是将构成该信号的电磁场限制在缝合过孔所包围的过孔结构内。

在这种情况下,噪声抑制机制有时被称为“屏蔽”,就好像过孔可以防止电磁波耦合到受干扰互连中一样。这在某种程度上是正确的。将缝合过孔结构靠近信号过孔可以通过两种方式降低噪声:

- 由于通孔更靠近地,因此通孔区域的环路电感较低

- 靠近地面会导致信号通孔/接地通孔过渡占据通孔沿线总电容的主导地位

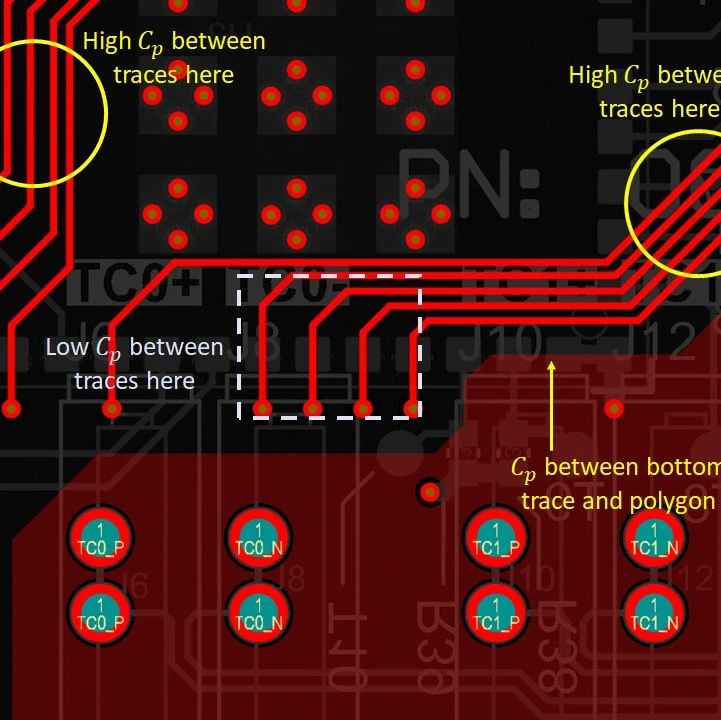

第二点相当于通过将接地平面靠近信号走线来减少寄生电容。我已在本文中展示了如何减少与其他信号网络的寄生电容耦合;此处预期也会出现同样的结果。

缝合过孔和反焊盘如何影响过孔阻抗

缝合过孔和反焊盘共同作用,设定过孔的阻抗,适用于通过过孔的单端信号和差分信号。上一节中电容和电感的修改是指,缝合过孔在层过渡中的位置将决定过孔的阻抗。与之相关的是反焊盘,理想情况下它应该与缝合过孔相交,因此它们共同作用,共同改变阻抗。

由于缝合过孔排列和层过渡周围反焊盘尺寸的存在,大多数过孔阻抗计算器完全无法计算实际过孔阻抗。准确确定过孔阻抗以及缝合过孔对过孔阻抗影响的唯一方法是使用电磁场求解器。我们必须区分单端和差分过孔过渡的两种缝合过孔选项,如下表所示。

这里我们关于过孔阻抗和缝合过孔有两个重要的结论:

- 对于单端过孔,需要缝合过孔来提供返回路径,因此它们是设置过孔阻抗的主要因素。

- 对于差分过孔,缝合过孔会影响阻抗,但阻抗对反焊盘尺寸和每层的层排列/Dk值更为敏感。

下面的示例展示了调整缝合过孔的位置如何影响差分过孔。在下图中,我比较了具有合并圆形反焊盘的差分过孔。缝合过孔距离信号过孔较远。当我们将缝合过孔拉近时,我们可以看到局部频率(绿线)移到了更高的频率,但阻抗没有变化。这意味着缝合过孔在限制过孔周围的电磁场方面发挥了作用,但除此之外没有太大作用。

在这种情况下,缝合过孔对中频差分对电容负载的影响并非最显著。反焊盘和信号过孔间的间距已经小于缝合过孔的距离,因此它们是电容负载的最大决定因素。

当信号过孔间距较大且反焊盘开口较大时,缝合过孔对信号过孔阻抗的影响会更大,因为它们可能是电容负载的主要来源。当信号过孔间距较小时,反焊盘对过孔阻抗的影响更大。当信号过孔间距较小且反焊盘较小时,您可能不会注意到缝合过孔的任何影响(如上图所示)。

在低频下,不必担心缝合过孔的数量和反焊盘尺寸对过孔阻抗的影响;由于过孔的电气短路非常短,您很可能察觉不到任何影响。高于约 5 GHz 的频率时,如果缝合过孔放置不当、反焊盘较大或没有缝合过孔,可能无法提供足够的电容负载,从而导致过孔过渡为电感性,阻抗在几十 GHz 频率下可达约数百欧姆。

缝合通孔阵列能提供屏蔽吗?

当以阵列形式放置时,答案是“是”,但仅限于特定频率。当用于提供屏蔽时,设计人员可能只是猜测过孔之间所需的间距。在某些情况下,我们所说的波导屏蔽应该更确切地称为场限制。无论您想如何称呼它,缝合过孔都可以阻挡电磁波在某个最高频率以下的传播。

对于您想要抑制的给定频率,过孔之间的间距应大约为:

专门用于阻止电磁波传播的缝合过孔的间距要求与限制 PCB 上波导内的波的要求相同。

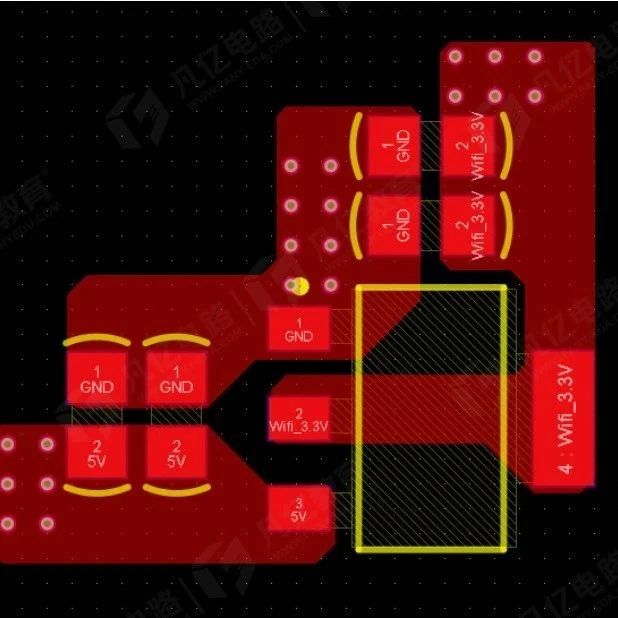

下面是一个用作天线馈线的接地共面波导的示例。在本例中,间距为 20 mil,根据上式,该间距适合屏蔽高达 43 GHz 的频率。如果附近有高速信号传输,我们可以预期这条馈线具有较高的屏蔽效果,这将有助于抑制射频线路中的串扰。

我认为这里需要注意的是,缝合过孔并非解决噪声问题的灵丹妙药,也不能成为您放弃最佳布线实践的借口。即使您已经按照上述方式使用了缝合过孔,您仍然应该为射频电路板实践良好的布局和布线策略。

缝合电源过孔

在电源系统的PCB布局中,缝合过孔通常不会采用典型的大间距布局。事实上,在这些设计中,您可能根本不会在大型接地覆铜区域看到它们。然而,缝合过孔阵列可用于在电源网络上创建低电阻层过渡。这使得过孔能够在层间以低损耗传输大量电流。

传输给定量的电流需要多少个缝合过孔?这取决于典型过孔的直流电阻。对于典型的过孔钻头直径和焊盘尺寸(10/20 mil)以及 1 mil 壁镀层厚度,过孔电阻约为 1.5 mOhm,热阻约为 180 °C/W。如果您尝试通过该过孔传输 20 A 直流电流,则会耗散 600 mW 的功率,并且预计过孔温度将升高 108 °C。

为了将温升控制在可接受的范围内,我们需要在阵列中使用多个过孔。如果我们并联使用10个这样的过孔,则每个过孔将承载2 A直流电流,每个过孔(以及整个阵列)的预期温升为1.08 °C。这应该可以展示如何使用温升目标来确定拼接过孔数量的限制。

自动缝合通孔布局

如果我们注意到,放置缝合过孔需要在电路板周围定位和放置大量的过孔,并且保持精确的间距,那么对于大多数 CAD 工具来说,这都很困难。较简单的 CAD 工具会强制手动放置缝合过孔,然后可能需要在电路板周围复制粘贴每一行/列以形成阵列。

Altium 在 PCB 编辑器中包含一个简单的实用程序,用于放置用户自定义尺寸和间距的缝合过孔。您可以通过选择过孔模板或设置自定义过孔尺寸和层过渡来放置缝合过孔。

那么,是否存在一种客观“正确”的缝合过孔使用方法呢?答案有时并不那么明确。我展示了一些缝合过孔阵列用于特定用途的实例:

- 如果只需要连接地线(无高速/射频),缝合过孔很方便,但不是必需的

- 如果提供跨层参考,缝合过孔也方便低速信号,以最大限度地减少电磁干扰

- 如果提供电源,紧密间隔的通孔可以提供高电流,同时将温升降至最低

- 对于高速信号转换,不能依赖随机放置的缝合过孔来保证信号完整性

因此,屏蔽仍然是缝合过孔尺寸、间距和布局方面一个悬而未决的问题。如需了解更多信息,请阅读这篇关于覆铜PCB 布局的文章,了解缝合过孔对噪声耦合和 EMI 的一些影响。

END

点击了解活动详情

点击了解活动详情往期精选:

请点下【♡】给小编加鸡腿