在日前举办的 2025 年 IEEE 国际电子器件会议(IEDM)上,比利时微电子研究中心(imec)发布了全球首项针对 3D 高带宽内存(HBM)与图形处理器(GPU)堆叠组件(HBM-on-GPU)的系统技术协同优化(STCO)热学研究成果。该类堆叠组件被视为支撑下一代人工智能应用的核心运算架构。

imec 指出,通过整合底层技术与系统级调节策略,可将 AI 训练负载下 GPU 的峰值温度从 140.7°C 降至 70.8°C,这一温控表现已与当前主流的 2.5D 集成技术持平。此项研究充分验证了跨层级协同优化 —— 即在不同技术抽象层实现协同调控 —— 结合全方位技术积累的独特优势,而这正是 imec 的核心竞争力所在。

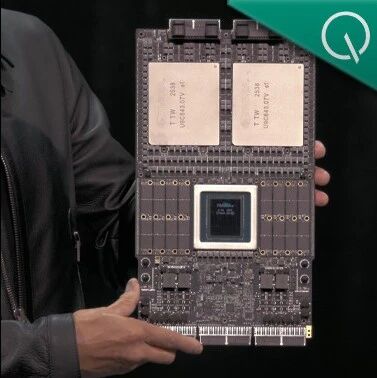

从技术架构来看,直接在 GPU 上方集成 HBM 堆叠,是构建新一代算力架构以满足数据密集型 AI 负载需求的极具吸引力的方案。相较于传统 2.5D 集成技术(将 HBM 堆叠置于硅中介层上,紧邻单颗或两颗 GPU),3D HBM-on-GPU 堆叠组件可大幅提升运算密度(单封装可容纳四颗 GPU),同时显著增加单颗 GPU 的内存容量与内存带宽。不过,这种高密度 3D 集成方案也面临严峻的散热挑战,更高的局部功率密度与垂直方向热阻,极易引发芯片过热问题。

为此,imec 在 2025 年 IEDM 上发布了业内首份针对 3D HBM 与 GPU 堆叠组件的全维度热仿真研究报告。该研究不仅精准定位了架构中的散热瓶颈,还提出了一系列提升该架构散热可行性的优化策略。实验数据显示,通过技术与系统级热调节手段的协同应用,AI 训练负载下 GPU 的峰值温度可从 141.7°C 降至 70.8°C。

据 imec 披露,本次研究采用的模型基于特定硬件配置:四颗 HBM 堆叠(每颗堆叠包含 12 颗异质集成 DRAM 晶粒)通过凸点直接键合在 GPU 上方,散热装置则部署于 HBM 堆叠顶部。研究团队基于产业级功率曲线绘制功率分布图,以此识别芯片局部热点,并与 2.5D 集成方案的基准数据进行对比。测试结果显示,在未采用任何热调节策略的情况下,3D 堆叠模型的 GPU 峰值温度达到 141.7°C,远超 GPU 与 HBM 的正常工作温度阈值;而在相同散热条件下,2.5D 集成基准方案的峰值温度仅为 69.1°C,处于稳定运行区间。基于上述数据,imec 进一步评估了技术与系统级热调节策略的协同优化效果,其中系统级策略涵盖 HBM 堆叠合并、硅基散热结构优化、双面散热设计及 GPU 频率调节等多项举措。

imec 系统技术协同优化(STCO)研究项目负责人詹姆斯・迈尔斯(James Myers)表示,将 GPU 核心频率降低 50%,可使芯片峰值温度从 120°C 降至 100°C 以下,满足内存稳定运行的温度要求。尽管这一操作会使 AI 训练负载增加 28%,导致训练速度有所放缓,但得益于 3D 架构带来的高通量密度优势,整体封装的综合性能仍优于 2.5D 基准方案。目前,研究团队正基于该方法,探索 GPU 与 HBM 倒装堆叠(GPU 置于 HBM 上方)等更多架构形态,以预判未来可能面临的热学限制。

imec 逻辑芯片技术研发副总裁朱利安・里克特(Julien Ryckaert)强调,此次研究成果,首次验证了 imec 跨技术协同优化(XTCO)项目在打造高散热稳定性算力系统方面的技术实力。XTCO 项目于 2025 年正式启动,旨在推动 imec 的技术研发路线与业界关键系统升级需求高效对接,其核心围绕四大系统级支柱展开:运算密度、供电效率、散热性能、内存密度与带宽。

朱利安・里克特还指出,imec 将系统技术协同优化(STCO)与设计技术协同优化(DTCO)的理念深度融合,并结合自身深厚的技术积淀,形成了独特的技术整合能力,这一能力在应对算力系统需求的持续增长与多元化挑战中具有极高价值。他同时发出倡议,邀请半导体生态圈内的各方企业,包括无晶圆厂设计公司与系统厂商,加入 imec 的跨技术协同优化项目,携手攻克算力系统升级过程中的关键技术瓶颈。