【内容目录】

1.封装首次进入AI芯片核心制造价值区间

【本文涉及的相关企业】

台积电、英伟达、英特尔、三星、日月光、Rapidus

围绕摩尔定律放缓的讨论,在半导体行业中已持续多年。进入生成式 AI 加速落地阶段后,行业关注点正在发生实质性转移:在先进制程带来的性能增益逐步收敛的背景下,系统层面的扩展能力开始成为决定算力上限的关键因素。算力竞争的焦点,正在从芯片能做多小,转向系统能扩展多大。

在这场竞争中,先进封装(Advanced Packaging)的地位显著上升,成为推动其发展的第二级火箭。封装的功能已从传统意义上的后段制造环节,延伸至系统架构设计、性能扩展以及成本结构优化等核心层面。对于面向数据中心的 AI 芯片而言,先进封装正在成为连接制程能力与系统性能之间的重要枢纽。

封装首次进入AI芯片核心制造价值区间

在 2025 年的一次产业论坛上,与会专家引用的数据显示:用于数据中心 AI 加速器(GPU 与 ASIC)的先进封装收入约为 41 亿美元,而同期先进晶圆制造服务收入约为 28 亿美元。在 AI 加速器相关的制造服务价值中,封装已占据了接近一半的比重。专家们一致认为,这种转变是前所未有的,而且,这种变化完全由人工智能驱动。

从历史角度看,这一结构变化具有显著的标志意义。过去数十年中,晶圆制造始终是技术门槛最高、价值占比最大的环节,封装的核心任务更多是实现电气连接、可靠性与量产交付,其价值通常远低于晶圆制造。如今,随着 AI 芯片规模和系统复杂度的提升,封装被赋予了新的功能定位,它不再只是完成芯片,而是在系统层面决定性能能否被真正释放。

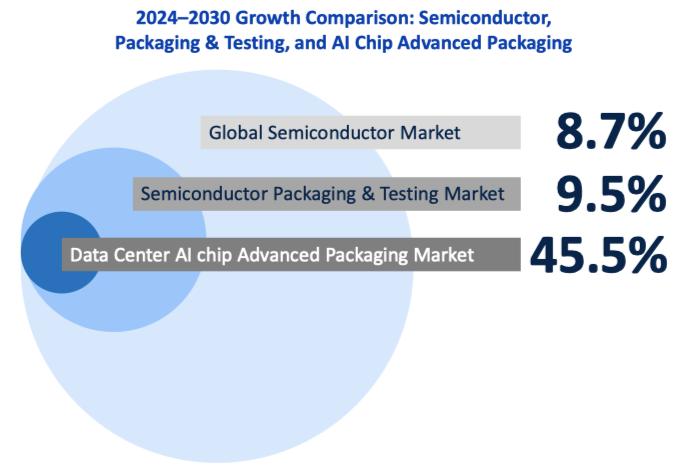

从长期趋势看,这并非短期需求失衡所造成的偶发结果。根据 DIGITIMES 的预测,到 2030 年,全球半导体市场规模将超过 1 万亿美元,年复合增长率(CAGR)约为 8.7%。而数据中心 AI 芯片相关的先进封装市场,年复合增长率预计达到 45.5%–46%,远高于行业平均水平。其市场规模预计将从 2024 年的 56 亿美元,增长至 2030 年的 531 亿美元。

更具启示意义的是,先进封装收入的增长速度,明显快于 AI 芯片出货量本身。到 2030 年,AI 芯片出货量预计由 3050 万颗增长至 5340 万颗,增幅有限,但单颗芯片所对应的封装价值却持续上升。这意味着,封装环节的价值来源,正在从数量驱动转向复杂度驱动。

图:2024-2030年半导体、封装测试与AI芯片先进封装增长率对比 (来源: DIGITIMES)

图:全球数据中心AI芯片先进封装收入预测(来源: DIGITIMES)

AI芯片结构中GPU 仍占主导,但ASIC亦势头强劲

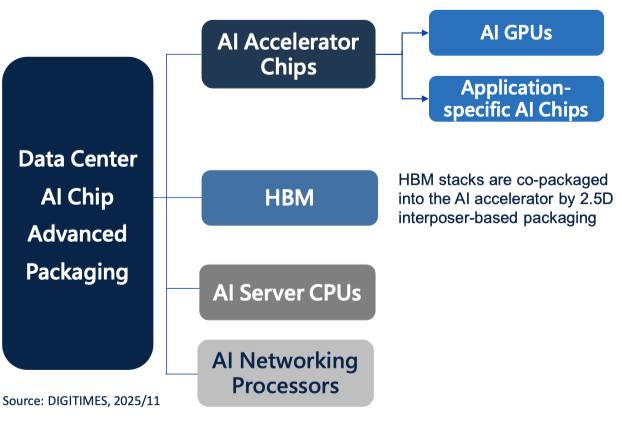

我们先来了解一下数据中心 AI 芯片的产品结构,及其采用的先进封装技术。AI 芯片主要包括以下这些类型:

AI 加速器芯片(AI Accelerator Chips):

这是算力竞赛的核心,可进一步细分为 AI GPU 和 应用专用 AI 芯片(ASIC)。为了支撑极致性能,这些芯片主要采用 CoWoS、FoCoS-Bridge、FOEB 以及英特尔的 Foveros 等封装技术。此外还有更具前瞻性的架构,如颠覆性的晶圆级系统(SoW),以及实现更高集成密度的 SoIC、Foveros Direct 和三星的 X-Cube等封装技术。

高带宽内存(HBM):

HBM 是解决“内存墙”问题的关键,通过 2.5D 中介层封装技术将其直接与 AI 加速器集成在一起。目前主流的连接工艺是微凸点热压键合(Micro-bump TCB)。预测从2028 年左右开始,更先进的混合键合(Hybrid Bonding)将成为该领域的重要技术演进方向。

AI 服务器 CPU(AI Server CPUs):

作为数据中心的大脑,高性能 CPU 的主要封装技术主要包括 CoWoS、Foveros 和英特尔的 EMIB(嵌入式多芯片互连桥)等。

AI 网络处理器(AI Networking Processors):

随着数据中心内部通信需求的激增,网络芯片也开始大规模应用先进封装。除了常见的 CoWoS 类似技术外,还有针对共封装光学(CPO)的 2.5D 扇出型封装。此外,SoIC 技术也被应用于光引擎(OE)中的 EIC/PIC(电/光集成电路)集成,这反映了光电协同封装已成为行业的高端趋势。

图:数据中心 AI 芯片的产品结构(来源: DIGITIMES)

在 AI 芯片产品结构中,高端 GPU 依然是先进封装收入的主要来源。尽管定制化 ASIC(如 Google TPU、AWS Trainium)的出货量年复合增长率预计达到 21%,高于高端GPU的10%,但从封装收入规模看,到 2030 年 GPU 相关收入仍预计高出 ASIC 超过 40%。

这一差异并不源于产品路线的优劣,而更多来自系统形态的不同。高端 GPU 往往集成更大规模的计算 Die,采用多 Chiplet 组合,并配置更高数量、更高带宽的 HBM 堆栈。这些设计直接推高了封装在互连密度、供电、散热与良率控制方面的技术要求,推高了 GPU 的单颗封装价值。

也正因如此,即便 GPU 的出货增速相对温和,其对应的封装与代工收入仍能保持较高增长。这一现象进一步强化了一个趋势判断:在 AI 时代,封装的价值并不简单取决于芯片类型,而取决于系统复杂度。

这一变化在成本结构上体现得尤为明显。联发科指出,封装在 AI 芯片总成本中的占比,已从过去不足 1%,上升至 50% 以上。对于芯片设计公司而言,封装不再是可以后置优化的环节,而是必须在架构设计阶段就纳入考量的核心要素。

图:数据中心AI芯片出货量增长率(来源: DIGITIMES)

封装技术正在进入AI系统架构层

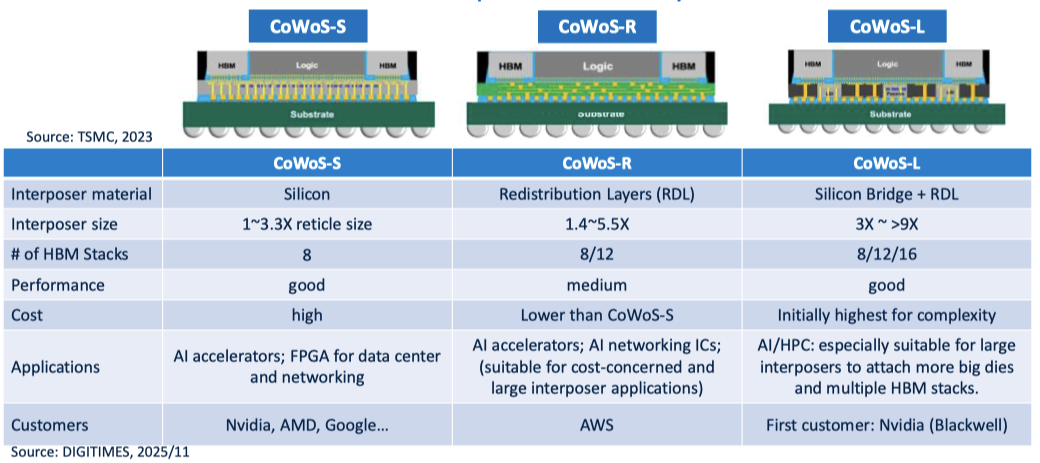

从技术层面看,AI先进封装的角色变化尤为明显。当前,高性能 AI 加速器仍主要依赖 2.5D CoWoS 封装方案。这是高性能 AI 加速器最成熟、应用最广泛的封装方案,预计到 2030 年该技术仍将占据约 58% 的市场份额。

随着芯片规模持续扩大,CoWoS-L 通过硅桥结构突破光罩尺寸限制,使中介层面积显著扩展至传统上限的 3.3 倍,甚至更高。这一能力为多 Die 集成和多 HBM 堆栈提供了现实基础。NVIDIA Blackwell架构即采用了该技术,以支持更大规模的计算芯片和多达 16 个 HBM 堆栈,这正是这一技术路径的集中体现。

图:CoWoS家族技术对比(S/R/L型)(来源:DIGITIMES)

在更高互连密度需求下,3D 封装逐步进入实用阶段。台积电的 SoIC 通过无凸点键合方式,实现了更高的互连密度和更低的信号延迟,成为 3D 封装的重要发展方向。同时,SoIC 也被应用于共封装光学(CPO)中的 EIC/PIC 集成,为高带宽、低功耗的数据传输提供封装层面的支持。

在更长远的探索中,晶圆级系统(SoW,System on Wafer)等方案也试图在整片晶圆尺度上构建系统,以获得远超传统封装的互连能力。这也被视为面向超大规模 AI 加速器的潜在技术方向。

先进封装拆解AI芯片性能瓶颈

在数据中心环境中,AI 芯片长期面临互连、内存带宽与散热三方面的限制,俗称互连墙、内存墙和散热墙。先进封装之所以被推到产业前台,正是因为它在这些关键瓶颈上提供了系统级的解决方案。

数据显示,从 28nm 演进至 A16 制程,若仅依赖制程微缩,整体算力提升约为 80 倍;在先进封装与异构集成(Heterogeneous Integration)的支持下,不同功能的Chiplets(小芯片)紧密拼装,算力提升可放大至约 320 倍。这个差距清晰地表明,先进封装在缩短信号路径、提升系统效率方面具有显著放大效应,已成为放大制程能力的重要杠杆。

为跨越内存墙,2.5D 封装与HBM 深度协同,内存与计算核心实现近距离集成,显著降低了访问延迟,缓解了内存带宽瓶颈,确保GPU不再因为等待数据而空转。

另一方面,当多颗高功耗Die堆叠在一起时,散热成了噩梦。先进封装通过优化的芯片布局和更先进的散热介质,在微米级空间内引导热量传导,是确保AI服务器在高压环境下稳定运行的前提。

图:从N28到A16的算力飞跃(来源: DIGITIMES)

先进封装产业链呈现区域分散趋势

在全球先进封装产业中,中国台湾依然处于无可替代的核心位置。2024 年,台湾地区在全球先进封装市场中的份额约为 77%,其中台积电在高端 AI 芯片封装领域发挥着关键影响力。

台积电方面多次指出,当前先进封装需求的快速增长,几乎完全由 AI 应用驱动。曾被视为成本高昂、扩产节奏受限的 CoWoS,如今已成为供不应求的关键资源。客户持续要求加大扩产节奏,这也使先进封装的核心问题从技术议题转变为资本投入与产能规划问题。

与此同时,现实约束也在逐步显现。台湾本地的土地资源与基础设施条件,使大规模、快速扩产面临挑战。在这一背景之下,地缘政治与供应链安全考量进一步推动了全球主要厂商在其他地区的加速布局,先进封装产业链呈现出一定的区域分散趋势。例如英特尔、三星、日本 Rapidus 以及中国大陆厂商,均在加快相关布局。

然而,从技术成熟度、良率控制和量产经验来看,台湾厂家在可预见的未来仍将保持超过 70% 的市场份额。

产业组织形态从专业化分工到虚拟集成

先进封装的重要性提升,也正在改变半导体产业的组织方式。在经历了数十年的“无晶圆厂+纯代工”的高度专业化分工之后,行业开始呈现一定程度的再整合趋势。例如,云服务商开始参与 AI 芯片设计、英伟达继续提供机架级系统、台积电、英特尔、三星、日月光等制造与封装厂商向系统级集成延伸。

但这一趋势并不意味着完全回归垂直整合。多方观点认为,当前趋势更适合描述为“虚拟集成”,即通过更紧密的跨公司协作,实现系统层面的优化,而非完全意义上的垂直整合。即便是高度自主的产品体系,也仍然依赖外部制造与封装能力,这使得专业化与协同合作将在相当长的时间内并行存在。正如专家们所强调的那样,在当今复杂的 AI 系统中,没有任何一家公司可以独立完成所有环节。

结语

随着 AI 应用持续扩展,先进封装已不再只是半导体制造流程中的配套环节,而是决定系统性能、成本结构与产业竞争力的重要基础设施。

在 CoWoS、SoIC、HBM 与 Chiplet 等技术持续演进的推动下,半导体产业的竞争重心,也在从单一制程节点,转向系统级异构集成能力。这一变化不仅重塑了制造价值的分布,也为未来十年的算力增长,奠定了新的技术与产业基础。

参考资料:

1. https://www.digitimes.com/reports/ai/2025_ai_chip_packaging/

2. https://www.digitimes.com/news/a20251107VL203/

3. https://www.digitimes.com/news/a20250808VL209/

作者:Felina Wu