一、混合键合:3D IC 封装的范式转移与核心价值

分析性引言:在“后摩尔时代”,半导体工业正处于从平面微缩向垂直集成转化的范式转移期。传统的微凸点(Microbumps)封装技术因受限于 20-40μm 的物理间距瓶颈,已无法满足 AI 与 HPC 对超高带宽及能效的严苛需求。混合键合(Hybrid Bonding),亦称直接键合互连(DBI),通过原子级的金属与介电层直接融合,消除了传统封装的中间焊料层。它不仅是 3D IC 的技术高地,更是 HBM 演进与系统级算力飞跃的战略支点。

技术机制解析:混合键合实现了介电材料(SiO₂ 或 SiCN)与铜电极在同一平面上的双重融合:

●表面制备: 依靠超高精度 CMP 工艺,将表面粗糙度( $R_a$ )控制在 0.5nm 以下。根据来源数据,铜焊盘需预设 5nm 或更小 的凹陷(Dishing),以补偿退火过程中的热膨胀。

●物理连接: 首先在室温下通过羟基(-OH)形成氢键初步粘合;随后在 150°C-400°C 退火,利用铜的原子扩散形成冶金级连接。

●性能增益:垂直互连密度提升15倍以上,互连电阻和寄生电容降低数个数量级。

●互连密度: 较传统微凸点提升逾 15 倍,间距可下探至 250nm 亚微米级。

●能效与热传导: 互连能效提高 3 倍以上,由于消除了底部填充材料(Underfill),垂直方向热阻显著降低。

“So What?” 洞察:混合键合强制芯片设计进入 “系统级多芯片协同设计”(DTCO) 阶段。设计者不能再孤立考虑单片逻辑,必须利用 3D 感知 PDK 在架构阶段锁定热、应力与时序。 战略建议: 领先代工厂必须通过构建 3D-aware 生态(如台积电 OIP)来锁定下游客户,而芯片设计公司则需在 EDA 流程中提前引入 3D 物理验证模块。

二、工艺路径对比:晶圆对晶圆 (W2W) vs. 芯片对晶圆 (D2W)

分析性引言:路径选择不仅涉及吞吐量,更直接挂钩 KGD(已知合格芯片)管理与异构集成的灵活性。

对比分析:

●W2W (Wafer-to-Wafer): 目前在 CIS 与 3D NAND 中应用最广。其优势在于利用晶圆级并行处理实现极致的套准精度(<50nm)。然而,其核心弱点是“良率乘数效应”,即底层晶圆的缺陷会导致对应位置的整对芯片报废。

●D2W (Die-to-Wafer): 是 HBM 与异构集成(如不同尺寸芯片堆叠)的核心路径。由于引入了 等离子体切割(Plasma Dicing) 替代机械/激光切割,大幅减少了颗粒污染与边缘裂纹(Die-edge chipping),这对于混合键合这种对颗粒极其敏感(200nm 以上颗粒即可致死)的工艺至关重要。

竞争要素矩阵:

“So What?” 洞察:HBM 路径修正: 虽然混合键合是长线目标,但受限于热预算与成本压力,SK 海力士、三星与美光在 HBM4 世代初期可能仍会沿用微凸点技术 。Hybrid Bonding 将在 HBM4 后的超高堆叠架构中爆发。 战略行动: 设备商应在 HBM 转型期重点推介 D2W 路径下的“等离子体切割+前道洁净标准”组合方案,以应对良率敏感度。

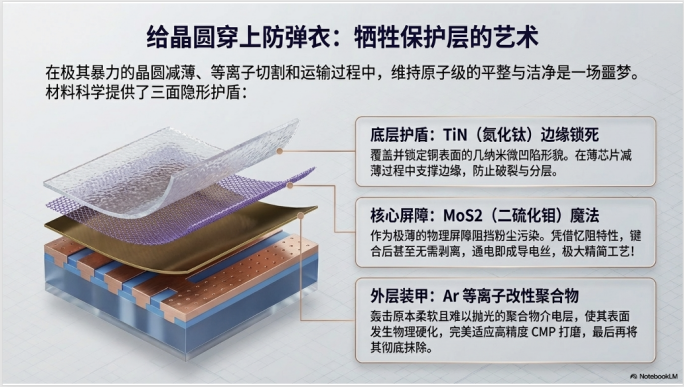

三、关键材料与物理极限挑战:纳米孪晶铜与表面保护

分析性引言:3D 堆叠的核心矛盾在于“互连密度 vs. 热预算”。材料学的突破是降低键合温度、保护敏感芯片(如 HBM 存储单元)的关键。

核心技术拆解:

●纳米孪晶铜 (nt-Cu): nt-Cu 具有高度 (111) 晶向,其表面原子扩散系数比普通铜高出 3-4 个数量级。利用 表面蠕变与扩散模型 ,nt-Cu 可将退火温度从 400°C 降至 200°C 左右,极大缓解了 3D 堆叠的应力。

●SiCN 介电层创新: 传统 PECVD 沉积 SiCN 需 ~350°C,而通过 溅射(Sputtering)工艺 可以在 <250°C 下完成沉积,进一步压缩了热预算。

●牺牲保护层 (TiN): Applied Materials 等厂商通过沉积牺牲性 TiN 层来锁定铜焊盘形貌,防止氧化并减少薄芯片(<50μm)在处理过程中的边缘脱层。

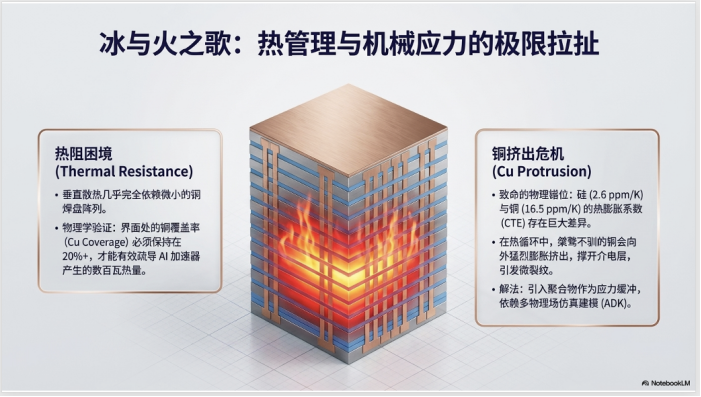

物理极限挑战:

●铜挤出(Cu Protrusion): 源于铜(16.5 ppm/K)与硅(2.3-2.6 ppm/K)之间巨大的 CTE(热膨胀系数)错配。热循环中,膨胀的铜会撑开界面,导致分层。

●等待时间(Queue Time)敏感性: 混合键合对水分极度敏感。CMP 与键合之间的“排队时间”是核心 KPI,长时间暴露会导致腐蚀与氢键粘合力下降。

“So What?” 洞察:战略建议: CTO 应优先评估 nt-Cu Gen 2(具备更细晶粒与更高机械稳定性)的电镀液供应链,并引入 “前道级洁净度控制” 到后道封装线。掌握 queue time 自动化管理能力的代工厂将拥有显著的良率溢价。

四、全球领先代工厂(Foundry)战略布局对比

分析性引言:混合键合已成为代工厂构建封闭生态、实施 IDM 2.0 战略的物理粘合剂。

三大巨头技术对比:

●TSMC SoIC: 性能标杆。其 SoIC-X 成功支持 AMD 3D V-Cache(9μm 间距)。核心护城河在于 OIP 生态系统 ,提供了经验证的 3D-aware PDK,使客户能像设计 2D 芯片一样便捷地设计 3D 堆叠。

●Intel Foveros Direct: 展现了其跨厂牌芯片堆叠的野心。Foveros Direct 将混合键合与 18A 制程及背面供电(PowerVia) 整合,有效解决了 3D 结构中顽固的 IR Drop(电压降)问题。

●Samsung X-Cube: 利用 HBM 垂直整合优势提供“一站式”服务。三星正通过超细铜混合键合(HCB)技术,试图消除异构集成中的物流与责任风险,吸引大规模 AI 训练客户。

●OSAT 补充视角:Amkor (S-Connect) 在亚利桑那州紧邻台积电建立园区,凭借其中立代工身份,专注于光子集成(CPO)等异构材料融合市场,为规避生态绑定的客户提供灵活选择。

“So What?” 洞察:战略抉择: 芯片决策者需在台积电的“昂贵但高保障”生态与 OSAT 的“灵活低成本”方案间权衡。 关键指标: 评估代工厂是否具备“Front-end to Back-end”的无缝整合能力,这是解决 3D 机械应力失效的先决条件。

五、关键设备供应商的竞争格局与性能差异化

分析性引言:混合键合设备正从传统后端设备向具备“前道精密性”的平台演进。

供应商技术矩阵:

“So What?” 洞察:设备采购指令: 对于处理 2nm 或高价值逻辑晶圆的产线, 原位返工能力(如 TEL 的 ZF 模块)应被视为强制性标准 ,而非选配。Besi 与 Applied Materials 的深度绑定证明了“前道化”是设备商生存的必经之路。

六、行业总结与决策建议:迈向集成时代

未来趋势预测:

1.250nm 亚微米时代: 互连间距将挑战 CMP 与材料物理的原子极限。

2.异质融合: 混合键合将跨越硅基,实现硅光子(COUPE)与 GaN 的 3.5D 集成。

3.HBM 临界点: HBM4 后的堆叠架构将全面倒向混合键合,以突破厚度与散热极限。战略行动指令:

●技术路线: 对于同质大批量产品(CIS/NAND)坚守 W2W;对于 AI 芯片与 HBM 的异构集成,必须从现在起布局 基于等离子体切割的 D2W 流程 。

●供应链安全: 重点评估 nt-Cu 电镀液 与 CMP 磨料 的准入风险。材料纯度与微观取向的微小波动即是良率的杀手。

●良率优化: 必须将 CMP 凹陷控制(<5nm)与 Queue Time 管理纳入生产线的实时闭环监控系统。

结束语:掌握混合键合核心技术,尤其是低温 nt-Cu 物理机制 与 纳米级对准设备,是未来十年占据全球半导体价值链制高点的入场券。