目前,半导体行业正热议芯粒(chiplet)——一种裸片,旨在与其他裸片组合成单个封装器件。各公司已开始规划基于芯粒的设计,也称为多裸片系统。然而,芯粒架构的设计究竟包含哪些内容、哪些技术已准备就绪,以及未来有哪些创新,仍然存在诸多不确定性。

在芯粒得到广泛应用之前,必须充分了解其技术及支持生态系统。随着技术不断涌现,芯粒有望成为高性能计算、人工智能加速、移动设备和汽车系统等众多应用领域的解决方案。

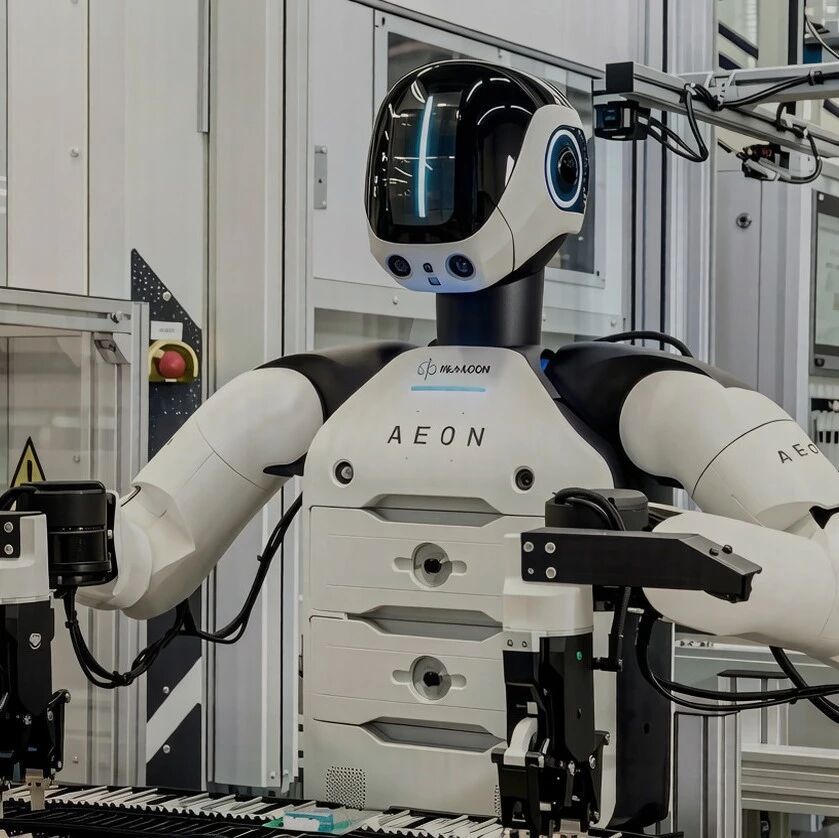

图1:在芯粒技术得到广泛应用之前,必须先了解这项技术。(来源:Arteris)

芯粒的兴起

直到最近,集成电路(IC)、专用集成电路(ASIC)、专用标准产品(ASSP)和片上系统(SoC)器件都是单片式的。这些器件构建在一块硅片上,然后封装在专用封装中。根据用法不同,“芯片”一词既可以指裸片本身,也可以指最终封装好的组件。

设计单片式器件的成本越来越高,扩展性也越来越差。解决方案是将设计分解成多个更小的裸片,称为芯粒,这些芯粒安装在称为基板的共享基底上,再整体封装于单一封装内,最终形成多裸片系统。

基于此,以下用例说明了芯粒架构的实际实现方式。分离式I/O与逻辑是一种芯粒用例,其中核心数字逻辑采用先进工艺节点实现,而收发器和存储器接口等I/O功能则被卸载到采用更旧、更经济工艺节点制造的芯粒上。一些高端SoC和FPGA制造商采用这种方法,通过为每项功能选用最优工艺,实现性能与成本的双重优化。

掩模尺寸限制分割用例适用于设计面积超过当前约850mm2掩模极限的情况,需将其分割为多个裸片。例如,英伟达的Blackwell B200图形处理器(GPU)采用双芯粒设计,每个裸片面积约800mm2,通过10TB/s的链路协同工作,表现如同单一GPU。

同构多裸片架构将多个相同或功能相似的裸片(如CPU、GPU或NPU)集成于单一封装,或通过“中介层”(interposer)连接。中介层是一种类似PCB但密度更高、通常采用硅基光刻工艺制造的连接层。每个裸片执行相同或相似任务,通常采用相同工艺技术制造。该方法使设计人员能够突破单裸片在物理尺寸(受850mm2掩模限制)和经济性(大裸片良率下降导致成本飙升)方面的瓶颈,实现性能与吞吐量的扩展。

功能解耦是大多数人听到“芯粒”时首先想到的架构。它将设计拆分为多个异构裸片,每个裸片均采用在成本、功耗和性能方面最适合其功能的工艺节点实现。例如,射频(RF)裸片可采用28nm工艺,模数转换器(ADC)和数模转换器(DAC)可用16nm工艺,核心数字逻辑则采用3nm工艺。由于SRAM在更精细工艺下面积缩放有限,大容量SRAM常采用7nm或5nm工艺实现。

好消息

企业计划或已转向芯粒架构的原因有很多,其中包括:

-

芯粒可构建超出单裸片物理极限的更大设计;

-

更小裸片带来更高良率,从而降低整体制造成本;

-

芯粒可混合搭配一流处理单元(如CPU、GPU、NPU及其他硬件加速器),并集成封装内存储器、外部接口及内存控制器;

-

多裸片系统既可通过同构处理单元阵列实现可扩展性,也可通过异构单元集合为每项功能选用最优工艺;

-

模块化的芯粒架构有助于平台化设计与设计复用。

图2:推动半导体公司采用芯粒架构的因素有很多。(来源:Arteris)

生态系统仍需发展

尽管优势明显,芯粒架构要实现广泛应用仍面临挑战。PCIe等标准已成熟,但UCIe和CXL等裸片间(D2D)通信标准仍在演进,生态采纳程度不均。同时,将不同芯粒集成到统一标准下的过程仍在发展中,增加了构建互操作系统难度。

有效的D2D通信还需在各类物理接口上实现低延迟与高带宽。寄存器映射和地址空间曾局限于单裸片,如今需扩展至整个多裸片设计。AMBA CHI等缓存一致性协议也必须跨越多个裸片,使系统级集成与验证成为重大障碍。

要理解芯粒系统的长期愿景,可先回顾当前板级设计的典型流程:设计团队从Avnet、Arrow、DigiKey、Mouser等分销商处选择现成组件,这些组件均支持I2C、SPI、MIPI等成熟标准接口,便于连接与集成。

当前SoC设计则通常通过授权多个可信第三方供应商的软知识产权(IP)功能模块来开发单裸片IC。团队还会开发一个或多个专有IP以实现产品差异化。所有软IP随后被集成、验证并实现到半导体裸片上。

芯粒设计的长期目标是建立完整的芯粒生态系统:设计团队可像板级工程师一样,从芯粒分销商处采购由可信第三方预验证的现成芯粒。这些芯粒将采用业界广泛认可的“黄金”验证IP完成预验证,从而实现预设计芯粒的无缝集成,无需在流片前对其进行联合验证。

团队也可基于相同验证IP开发自有芯粒。遗憾的是,这一生态系统及完备的行业标准规范预计还需数年才能成熟。即便是UCIe等标准,其规范内仍存在大量选项与变体,无法保证两个不同UCIe实现间的互操作性,更遑论高层协议兼容。

当前形势

尽管芯粒生态系统仍在演进,已有公司开始构建多裸片系统。大型企业(如AMD、英特尔和英伟达)掌控全流程;小型公司则常与两三家伙伴合作,构建自有“迷你生态”。它们通常采用UCIe等现有D2D标准,但往往在其上叠加自定义协议,并在流片前对所有芯粒进行联合验证。

众多电子设计自动化(EDA)与IP供应商正协作推进标准、工具流程及关键的验证IP(VIP),包括Arteris、Cadence、Synopsys、Arm,以及RISC-V领域的SiFive和Tenstorrent等企业。

如今,几乎所有人都涌向芯粒赛道。许多人大肆宣扬其前景,却往往言过其实、兑现不足。虽然真正成熟的芯粒生态系统可能还需5至10年,但无论规模大小,企业已在积极开发基于芯粒的设计。

关于作者

Ashley Stevens,Arteris公司产品管理与市场总监,负责相干片上网络(NoC)和裸片间互连技术。拥有逾35年行业经验,曾任职于Arm、SiFive和Acorn Computers。

END

![2026年中国5G工厂行业建设内容、相关政策、工厂建设现状、运营商项目数量及未来趋势分析:已建设超8000个5G工厂,建设质量同步提升[图]](https://xtechcon-static.oss-cn-chengdu.aliyuncs.com/xtimes/xtimes/images/2026-03-19/69bb4b05828aa.jpeg)