引言

随着生成式人工智能、高性能计算(HPC)及 5G/6G 通信技术的爆发式发展,全球先进封装市场规模从 2023 年的 378 亿美元预计增至 2029 年的 695 亿美元,其中 2.5D/3D 封装 以 20.9% 的复合年增长率成为技术迭代的核心驱动力。从凸块(Bump)、重布线层(RDL)等基础互连技术,到倒装芯片(FC)、晶圆级封装(WLP)及 2.5D/3D 堆叠方案,先进封装已形成覆盖异构集成、高密度互连的完整技术体系。与此同时,刻蚀、薄膜沉积、热压键合等设备需求因前道工艺后移而持续增量,全球设备市场格局正经历从国际垄断向国产替代突破的关键转型。本报告将系统剖析先进封装的技术演进脉络、设备市场需求及未来发展趋势,为产业参与者提供全景化的技术与市场洞察。

原报告我放在了知识星球

一、先进封装行业发展现状与市场驱动

1.1 市场规模与增长趋势

全球先进封装市场呈现显著扩张态势,根据 Yole 数据,其规模从 2023 年的 378 亿美元 预计增至 2029 年的 695 亿美元,复合年增长率(CAGR)达 12.7%。细分领域中,2.5D/3D 封装 增速最为突出,2023-2029 年 CAGR 达 20.9%,成为驱动市场增长的核心动力。出货量方面,先进封装出货量从 2023 年的 709 亿颗 攀升至 2029 年的 976 亿颗,CAGR 为 5.5%,其中 WLCSP、SiP 和 FCCSP 在出货量上保持领先地位。此外,晶圆产量方面,2023-2029 年先进封装晶圆总产量(等效 300mm)以 11.6% 的 CAGR 增长,2.5D/3D 技术 增速达 32.1%,显著受益于 AI 及高性能计算的芯片面积扩展需求。

资料来源:Yole 华金证券研究所

1.2 核心驱动因素

1.2.1 人工智能与高性能计算的技术拉动

生成式人工智能(AI)与高性能计算(HPC)是先进封装需求的核心驱动力。AI 芯片对算力密度的极致要求推动 2.5D/3D 封装 成为主流方案,例如 CoWoS 技术通过硅中介板实现多芯片集成,满足 AI 服务器的高带宽低延迟需求。数据中心对低功耗、高可靠性封装的迫切需求,进一步加速了 HBM 等 3D 堆叠技术的规模化应用。Yole 数据显示,AI 相关半导体市场 2024-2033 年 CAGR 达 28.9%,显著高于总半导体市场的 6.8%,驱动先进封装技术向高密度互连方向迭代。

1.2.2 5G/6G 与消费电子的市场需求

扇出型封装(FOPLP)凭借低成本和灵活性优势,持续满足 5G 通信与消费电子领域的集成需求。与传统晶圆级封装相比,FOPLP 面积使用率超 95%,较 300mm 晶圆级封装成本降低 66%,适用于中低端市场并逐步向高端拓展。Yole 预测,2029 年 FO(含 IC 载板)市场规模达 43 亿美元,其批量生产能力与异构集成特性,契合 5G 终端对小型化、低功耗的要求。

2023-2029E FO(含IC载板)收入规模(百万美元/%)

1.2.3 汽车电子与自动驾驶的场景拓展

汽车先进封装解决方案在自动驾驶、ADAS 及信息娱乐系统中快速渗透。自动驾驶对低功耗、高可靠性封装的需求,推动嵌入式封装(EMIB)等技术在车载芯片中的应用,实现不同工艺节点芯片的异构集成(如 10nm CPU 与 22nm 内存的整合)。日月光等厂商数据显示,高端汽车产品封装需求保持强劲,传统 MCU 及低端产品虽面临库存调整,但 ADAS 功能普及持续拉动先进封装需求。

1.3 技术路线演进与行业协同

1.3.1 摩尔定律放缓与 3D IC 的加速应用

随着制程工艺向先进节点推进,单位晶体管成本下降幅度显著放缓。从 16nm 到 10nm,每 10 亿颗晶体管成本降低 23.5%,而 5nm 到 3nm 仅下降 4%,促使行业加速采用 3D IC 技术。混合键合、热压键合(TCB)等先进封装技术通过异构集成优化算力密度,弥补制程进步放缓的瓶颈。例如,HBM 通过 TSV 堆叠实现高带宽存储,其堆叠层数与 IO 密度随技术迭代持续提升,成为突破芯片面积限制的关键方案。

1.3.2 先进制程与先进封装的协同发展

先进制程与先进封装呈现协同演进趋势:先进制程向纳米级(如 2nm)推进,而先进封装聚焦微米级精度提升。凸块节距从传统的 75-200μm 缩小至 10-30μm,硅通孔(TSV)深度控制在 20-30μm,实现芯片间立体互连。2.5D/3D 封装技术 通过硅中介板(如 CoWoS)和 TSV 堆叠(如 HBM),构建 “先进制程 + 先进封装” 的协同体系,有效缩小芯片与封装间的性能差距,满足 AI、HPC 等领域对算力密度的极致需求。

二、先进封装基础技术体系

2.1 凸块(Bump)技术

2.1.1 技术演进与工艺特性

凸块技术正朝着更小节距、更小直径方向发展,成为三维系统封装的核心互连技术。在三维系统封装中,微凸点互连通过在芯片表面制备可润湿凸点,与基板区域对准并实现最短电连接通路,大幅提升封装密度。当前技术演进路径从早期的 SnPb C4 Bump(直径 75-200μm)发展至 Cu Pillar 无铅凸块(直径 10-30μm),节距同步缩小,满足高密度集成需求。

2.1.2 制备工艺对比与应用

凸块制备主要包括机械打珠法、焊膏印刷法、植球法和电镀法。其中,电镀法可制备直径小于 60μm 的凸点,均匀性好,适用于先进封装,但工艺复杂且存在环境污染问题;机械打珠法工艺简单但效率低,适用于离散芯片;植球法产能大但最小植球直径受限至 60μm。该技术在倒装芯片(FC)互连中尤为关键,如 C4 可控塌陷芯片连接技术实现基板到中介层的高效连接。

2.2 重布线层(RDL)技术

2.2.1 工艺进步与精度提升

RDL 技术通过晶圆级金属布线变换芯片 I/O 焊盘位置,形成新的互连结构,是实现芯片水平方向互连的关键。根据未来半导体披露,头部厂商封装业务的 RDL 线宽和线间距(L/S)从 2023/2024 年的 2/2μm 发展至 2025/2026 年的 1/1μm,预计 2027 年后进入 0.5/0.5μm 时代。4 层 RDL 工艺已成熟,良率达 99%,可满足约 85% 的封装需求,未来布线层数将从 4 层增至 8 层以上。

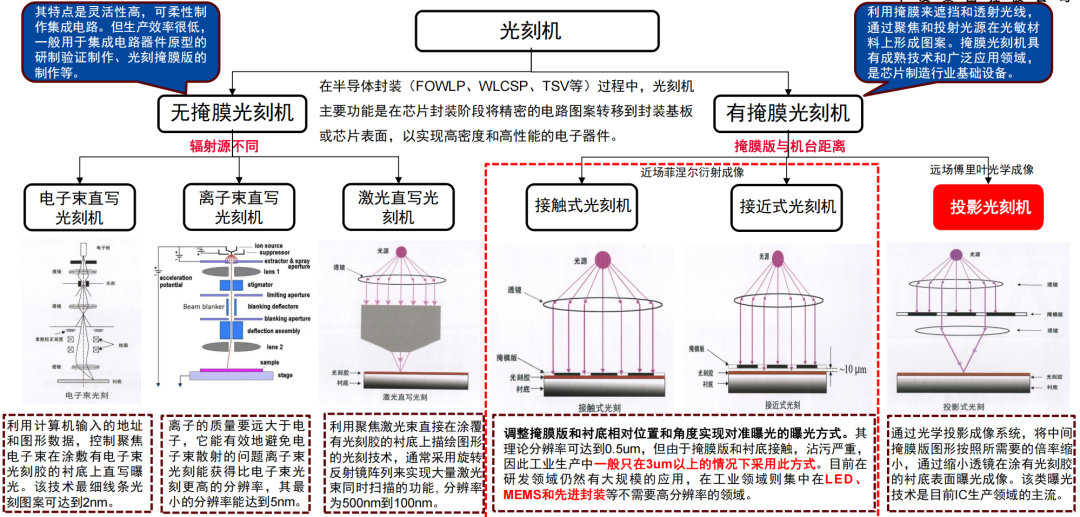

2.2.2 制造流程与设备需求

RDL 通常采用半加成工艺,包括电介质沉积、湿法 / 干法蚀刻、阻挡层和籽晶层沉积及镀铜等步骤,需配套掩膜设备、涂胶机、溅射台、光刻机、刻蚀机等。其工艺精度直接影响封装密度,例如在扇出型封装(FOWLP)中,RDL 技术与凸块工艺结合,实现芯片外部的布线扩展,提升 I/O 密度。

2.3 硅通孔(TSV)技术

2.3.1 工艺步骤与类型划分

TSV 技术通过在硅片上垂直穿孔并填充导电材料,实现芯片间立体互连,是 2.5D/3D 封装的核心基础。其主要工艺步骤包括孔刻蚀、绝缘层沉积、扩散阻挡层 / 种子层沉积、导电材料填充及表面平坦化。根据孔底部导电连接需求,TSV 制造分为两种类型:类型 Ⅰ 无需孔底部直接导电,类型 Ⅱ 则需去除孔底部绝缘层后实现导电连接。

2.3.2 技术路线与应用场景

TSV 工艺按制程阶段分为 Via First、Via Middle 和 Via Last。Via Middle 为最普遍工艺,采用 Cu 填充,适用于 CMOS 结构完成后的通孔制作;Via Last 则在晶圆减薄后刻蚀 TSV,采用 Si 片固定技术辅助填充。在应用中,2.5D 封装中 TSV 充当多颗裸片与电路板的桥梁(如 CoWoS),3D 封装中用于芯片堆叠(如 HBM),TSV 深度通常根据堆叠芯片厚度确定,控制在 20-30μm。

2.4 混合键合(Hybrid Bonding)技术

2.4.1 技术原理与优势特性

混合键合利用范德华力实现芯片连接,无需额外能量,通过金属(如铜)和氧化物键合的组合完成互连。其核心优势在于大幅减少凸块间距和接触间距,增加连接密度(可达 10,000 至~1M connections per mm²),实现更快传输速度与更低功耗。与传统微凸点相比,混合键合热阻降低 80%,是下一代高密度集成的关键技术。

2.4.2 工艺路线与应用前景

混合键合分为 Wafer to Wafer(W2W)和 Die to Wafer(D2W)两种工艺路线。W2W 键合良率更高,通过单独腔室对齐和键合,过程更洁净,但无法筛选已知良好芯片(KGD);D2W 通过重构载体晶圆实现 KGD 对齐,精度更高但步骤复杂。该技术最早应用于 SONY 高端 CIS 产品,目前三星、SK 海力士等厂商正推动其在 HBM4 等下一代产品中的量产,预计 2028 年占据 HBM 工艺的 36%。

三、堆叠互联技术方案与应用

3.1 倒装芯片(FC)技术

3.1.1 技术优势与原理

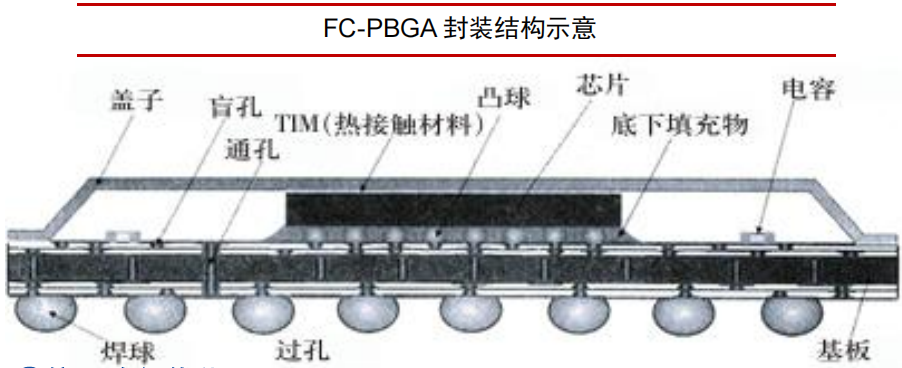

倒装芯片(Flip Chip, FC)技术通过凸点(Bump)将芯片正面朝下直接与基板连接,采用区域阵列式分布,相较于引线键合的周边布线,显著优化信号路径、提升散热性能并增加 I/O 引脚密度。该技术省去键合丝,信号通过凸点直接连接基板,缩短传输路径,减少信号延迟与寄生电感,同时芯片与基板直接接触提升散热效率,支持高性能芯片的稳定运行。

3.1.2 市场规模与应用

根据 Yole 数据,2024Q2 FCBGA 营收达 23 亿美元,环比增长 6.8%,同比增长 18%,预计未来因 AI 需求及 2.5D/3D 封装应用持续增长。2029 年 FCBGA 收入规模预计达 180 亿美元,CAGR 10.3%,出货量 CAGR 5.1%;FCCSP 未来两年收入增长,2029 年收入规模 CAGR 6.9%。消费电子为首要应用领域,覆盖移动终端、汽车电子及通信基础设施,AI 芯片封装需求推动 FCBGA 在高性能计算场景的渗透。

3.2 晶圆级封装(WLP)技术

3.2.1 技术分类与工艺特点

晶圆级封装(Wafer-Level Package, WLP)在整片晶圆上完成封装测试后切割,直接贴装至基板,封装尺寸接近芯片尺寸,成本大幅降低。按芯片与封装尺寸关系分为扇入型(FI-WLP)和扇出型(FO-WLP):FI-WLP 封装尺寸与芯片相同,锡球位于芯片内,适用于低 I/O 数量场景;FO-WLP 封装尺寸大于芯片,锡球扩展至芯片外,通过批量处理构建金属化结构,封装后 IC 面积可达芯片的 1.2 倍。

3.2.2 工艺路线与市场预测

FO-WLP 进一步分为 Chip first(Die face up/down)和 Chip last(RDL first)工艺。Chip last 技术因避免芯片损失、消除偏移且支持超细 RDL(线宽线距 < 2μm),成为精良扇出封装的首选。市场方面,2029 年 WLCSP 规模预计 24 亿美元,FO(含 IC 载板)达 43 亿美元,FO 封装出货量 CAGR 3.6%。移动和消费终端为主要应用领域,占比超 70%,汽车电子与通信基础设施需求逐步提升。

3.3 2.5D/3D 封装技术

3.3.1 2.5D 封装:CoWoS 技术与应用

2.5D 封装通过硅中介板(Interposer)实现多颗芯片并列互连,TSV 连接中介板与基板,代表技术为台积电 CoWoS。该技术分为 CoW(集成 Logic IC 与 HBM)和 oS(凸块接合至基板)两段,基于硅中介板提供更高互联带宽与更低延时,广泛应用于 GPU 等 AI 芯片。CoWoS-S 使用硅中介层,CoWoS-R 采用 RDL 中介层,CoWoS-L 通过夹层与 LSI 芯片互连,满足不同算力密度需求。2029 年 2.5D/3D 封装规模有望达 378.58 亿美元,CIS 为主要收入来源,CBA DRAM 增速最快(CAGR 649.9%)。

3.3.2 3D 封装:HBM 技术与工艺

3D 封装通过 TSV 实现芯片垂直堆叠,典型应用为高带宽存储(HBM)。HBM 在前端制程后增加 TSV 制程,包括光刻、干刻、沉积镀膜、TSV 填孔(电镀 + CMP)等,TSV 深度 20-30μm,完成后进行后端金属布线与微凸点形成。技术路线包括无凸点键合(Hybrid Bonding)和 Via-last TSV(Sequential/Collective),前者通过铜 - 氧化物键合提升互连密度,后者优化堆叠层数与 IO 密度。HBM3e 堆叠层数达 12 层,HBM4 预计采用混合键合,2028 年混合键合工艺占 HBM 应用的 36%。

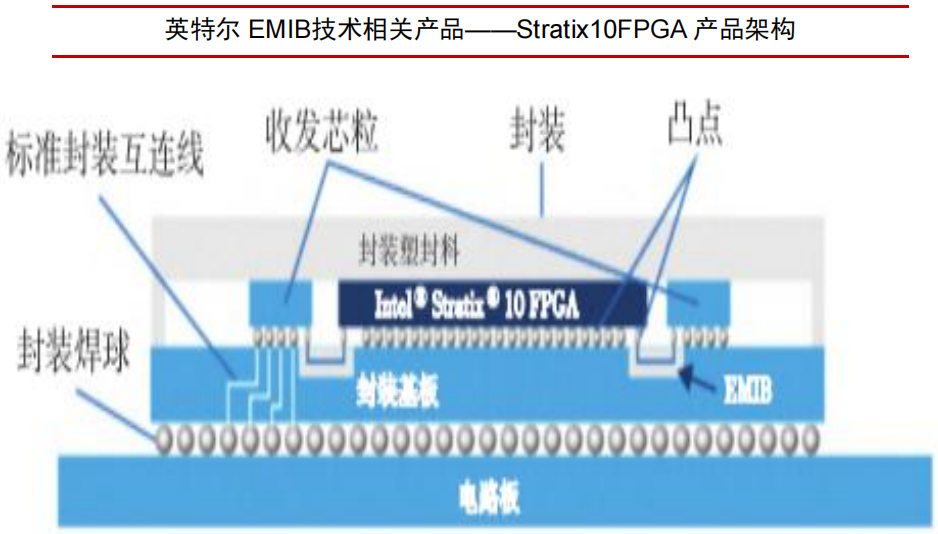

3.4 嵌入式封装(EMIB)技术

3.4.1 技术特点与优势

嵌入式封装(EMIB)属于无 TSV 的基板类封装技术,通过硅片实现局部高密度互连,与传统 2.5D 封装相比,具有封装良率高、无需额外工艺、设计简单等优势。该技术支持异构集成,例如将 10nm 工艺的 CPU、14nm 的 IO 单元及 22nm 的内存整合为单一处理器,降低能耗并提高集成度。EMIB 技术方案基于标准有机基板制备,核心挑战在于盲孔与硅桥芯片焊盘的精确对准,涉及硅桥贴装精度、基板孔洞设计等关键环节。

3.4.2 应用实例与市场定位

英特尔 Stratix 10 FPGA 采用 EMIB 技术实现多芯片集成,通过硅桥连接不同工艺节点的芯粒,优化性能与成本。该技术适用于对功耗、集成度有较高要求的场景,如 AI 边缘计算芯片、汽车电子控制单元,填补 2D 封装与 2.5D/3D 封装之间的技术空白,与 CoWoS 等技术形成互补,推动异构集成方案的多元化发展。

四、先进封装设备需求与市场格局

4.1 设备技术升级趋势

先进封装设备需求呈现前道工艺后移的显著特征,刻蚀、薄膜沉积、电镀等前道设备在封装环节的应用持续深化。随着封装技术向 2.5D/3D 演进,设备精度要求从传统的微米级向亚微米级提升,例如贴片机键合精度需达到 ±1.5μm,临时键合 / 解键合设备的套准精度要求≤2.5μm。同时,设备智能化与自动化程度大幅提升,集成视觉系统、MES 系统及实时工艺监控功能,满足先进封装多步骤、高精度的制程需求。

4.2 核心设备分类与市场

4.2.1 晶圆减薄与划片设备

4.2.1.1 减薄机:高精度加工主导市场

全球晶圆减薄设备市场呈寡头垄断格局,2022 年市场规模约 8.3 亿美元,预计 2029 年增至 13.2 亿美元(CAGR 6.5%)。日本 DISCO、东京精密(TOKYO SEIMITSU)合计市占率超 65%,其设备可实现 25μm 以下晶圆减薄及 15μm 高速量产。国内华海清科 Versatile-GP300 减薄抛光一体机已实现量产交付,中国电科 12 英寸系列减薄机发货突破百台,逐步实现进口替代。

4.2.1.2 划片机:激光技术推动精度升级

2022 年全球划片机市场规模约 117 亿元,预计 2029 年达 25.2 亿美元。日本 DISCO、东京精密占据高端市场,其激光切割机 DFL 系列可实现碳化硅晶圆切割速度提升 10 倍。国内光力科技通过并购整合,成为国产高端划片机第一品牌,12 英寸双轴全自动划片机 ADT-8230 定位精度达 3μm,打破国外垄断。

4.2.2 贴装与键合设备

4.2.2.1 贴片机:高精度集成驱动市场

2023 年全球半导体贴片机市场规模 10 亿美元,2018-2024 年 CAGR 7.43%,ASM、Besi 合计市占率超 60%。先进封装贴片机精度从传统的 10-25μm 提升至 2.5μm,如华封科技 AvantGo E2 支持 2.5D/3D 封装,键合力控制精度达 ±0.05N。国内新益昌高精度固晶机 HAD8212 适用于 CoWoS、HBM 封装,位置精度 ±3μm,已获头部客户订单。

4.2.2.2 热压键合(TCB)设备:HBM 封装核心装备

2024 年全球 TCB 设备市场规模 1.19 亿美元,预计 2031 年达 3.17 亿美元(CAGR 14.5%),韩国韩美半导体、SEMES 及日本 Shinkawa 主导市场。设备需满足 ±1.5μm 键合精度及 300N 键合力控制,如 ASMPT FIREBIRD TCB 系列支持惰性环境下的 LPC 制程,适用于 HBM 多层堆叠。国内普莱信智能 Loong WS-C2W 热压式固晶机已实现 1μm 贴装精度,进入中试阶段。

4.2.2.3 混合键合设备:下一代技术布局加速

2027 年 W2W/D2W 混合键合设备市场规模预计达 5 亿 / 2.3 亿美元,2030 年设备需求或达 1400 台(累计市场 28 亿欧元)。国际厂商如 ASMPT、BESI 已推出 D2W 混合键合机,国内拓荆科技 Dione 300 晶圆对晶圆混合键合设备通过客户验证,芯慧联 3DSIXI 设备应用于 CIS、3D NAND 领域,与国际巨头形成技术追赶态势。

4.2.3 互连与再布线设备

4.2.3.1 电镀设备:高深宽比工艺主导

2023 年全球半导体电镀设备市场规模 5.59 亿美元,预计 2030 年达 8.55 亿美元(CAGR 6.0%),泛林半导体、应用材料、盛美上海占据主要份额。设备需支持深宽比 > 10:1 的 TSV 填充,如盛美上海 UltraECP3d 电镀设备采用多阳极技术,实现 2μm 超细 RDL 线电镀。国内厂商在先进封装电镀领域突破显著,已实现 TSV 工艺全流程国产化。

4.2.3.2 光刻机:先进封装专用机型崛起

2023 年全球先进封装光刻机市场规模 18.4 亿元,预计 2030 年达 30.9 亿元(CAGR 8.3%),K&S、Onto、Canon 主导市场。上海微电子 SSB500 系列步进投影光刻机支持 0.8-2μm 分辨率,适用于 FC、FOWLP 及 2.5D/3D 封装,已实现批量供货。

4.2.3.3 刻蚀设备:深硅刻蚀技术关键

2025 年全球干法刻蚀设备市场规模预计 181.85 亿美元,泛林半导体、东京电子、应用材料合计市占率超 90%。深硅刻蚀设备需支持 Bosch 工艺,如中微公司 Primo TSV 300E 设备在 3D 芯片硅通孔刻蚀中通过验证,北方华创 PSE V300 深硅刻蚀机应用于 2.5D/3D TSV 制程,实现国产设备在先进封装领域的重复订单突破。

4.2.3.4 薄膜沉积设备:高深宽比覆盖关键

2024 年全球薄膜沉积设备市场规模约 230 亿美元,应用材料、泛林半导体、东京电子垄断市场。设备需满足 TSV 绝缘层、阻挡层及种子层的高精度沉积,如北方华创 Polaris 系列物理气相沉积系统针对 TSV 工艺优化,实现铜、钛等材料的均匀覆盖,拓荆科技 PECVD 设备应用于混合键合界面层沉积。

4.2.4 涂胶显影与湿法设备

2023 年全球涂胶显影设备市场规模约 40 亿美元,东京电子占据 90% 份额,国内芯源微在成熟制程领域实现突破。后道先进封装用涂胶显影机需支持厚胶曝光及高深宽比图形,如芯源微设备已批量应用于台积电、长电科技等一线厂商,临时键合 / 解键合设备实现与国际先进水平对标,键合 TTV 指标达业内领先。

4.3 中国设备厂商突破

国内厂商在刻蚀、薄膜沉积、电镀等关键设备领域实现多点突破:北方华创覆盖刻蚀、沉积、电镀等全产品线,在 HBM 封装中提供 TSV 刻蚀、薄膜沉积等设备;中微公司深硅刻蚀设备在晶圆级封装及 MEMS 领域获得重复订单;拓荆科技混合键合设备实现产业化应用,键合套准精度量测设备通过验证;华海清科 CMP、减薄设备进入存储及先进封装产线,逐步打破国际垄断。

五、未来技术演进与设备需求展望

5.1 技术演进趋势

5.1.1 混合键合技术的规模化应用

混合键合技术作为下一代高密度集成的核心方案,将在 10μm 节距以下互连中取代传统热压键合。该技术通过铜 - 氧化物键合组合实现无凸点互连,传输速度提升 11.9 倍,带宽密度提高 191 倍,能耗降低超 100 倍。韩国三星、SK 海力士正推动其在 HBM4 产品中的应用,预计 2028 年混合键合工艺将占据 HBM 所用工艺的 36%,成为突破堆叠层数与 IO 密度瓶颈的关键技术。

5.1.2 3D 封装技术的深度迭代

3D 封装技术将向更高堆叠层数与更低互连间距发展。HBM3e 已实现 12 层堆叠,HBM4 预计采用混合键合技术,互连间距缩小至 18μm,2028 年 HBM5 目标间距 < 15μm。Via-last TSV 工艺中,Collective TSV 通过统一通孔制程降低成本,Sequential TSV 优化堆叠精度,两者协同推动 3D 封装在 AI 芯片、高带宽存储中的规模化应用。

5.1.3 封装与制程的协同进化

先进封装与先进制程的协同向 “异构集成” 方向深化。随着制程工艺进入 3nm 以下,单位晶体管成本下降幅度趋缓(5nm 到 3nm 仅降 4%),3D IC 通过 Chiplet 架构实现算力密度优化。例如,台积电 SoIC-X 混合键合技术支持逻辑芯片与存储芯片的异构堆叠,英特尔 EMIB 技术整合不同工艺节点芯粒,推动 “制程缩小 + 封装集成” 的双轨发展。

5.2 设备需求展望

5.2.1 高精度设备的技术突破

5.2.1.1 混合键合设备的量产需求

2027 年 W2W 和 D2W 混合键合设备市场规模预计达 5 亿 / 2.3 亿美元,2030 年全球需求或达 1400 台(按 200 万欧元 / 台测算,累计市场 28 亿欧元)。设备需满足 ±1μm 的键合套准精度,支持晶圆级与芯片级的表面活化处理,如拓荆科技 Dione 300 晶圆对晶圆混合键合设备已实现产业化应用,Propus 芯片对晶圆预处理设备通过客户验证。

5.2.1.2 TCB 设备的性能升级

热压键合(TCB)设备需适应 HBM 堆叠层数提升,2031 年市场规模预计达 3.17 亿美元(CAGR 14.5%)。设备需将键合精度从 ±1.5μm 提升至 ±1μm,键合力控制精度达 ±0.05N,如韩美半导体设备支持 16 层 HBM 堆叠,ASMPT LithoBolt™混合键合机整合 D2W 工艺,满足 Chiplet 集成需求。

5.2.2 前道设备的后移扩展

刻蚀、薄膜沉积、电镀等前道设备在先进封装中的应用持续深化。深硅刻蚀设备需支持 30:1 以上高深宽比刻蚀,薄膜沉积设备需实现 TSV 绝缘层的原子层沉积(ALD),电镀设备需满足 2μm 以下超细 RDL 线电镀。北方华创、中微公司等国内厂商的刻蚀设备已应用于 2.5D/3D TSV 制程,盛美上海电镀设备实现 TSV 全流程国产化。

5.2.3 国产化设备的市场替代

国内设备厂商在先进封装领域的突破加速进口替代。华海清科 12 英寸减薄机 Versatile-GP300 实现批量供货,光力科技 12 英寸划片机 ADT-8230 打破国外垄断,芯源微涂胶显影设备进入台积电等一线厂商产线。预计 2025-2030 年,国内厂商在减薄、划片、电镀等设备的市场份额将从不足 10% 提升至 20%,逐步实现关键设备的自主可控。

5.2.4 面板级封装(PLP)设备布局

扇出型面板级封装(FOPLP)设备因成本优势成为新增长点。与 300mm 晶圆级封装相比,515mm×510mm 面板级封装面积使用率从 64% 提升至 93%,成本降低 66%。设备需支持 600mm×600mm 方板处理,如芯碁微装 PLP 3000/4000 系列采用多光学引擎扫描技术,适配 RDL、Bumping 等制程,推动 FOPLP 在中低端市场的规模化应用。

*来源:半导体产业报告

芯启未来,智创生态