咨询公司VDC Research今年4月份在《Embedded Processor Architectures(嵌入式处理器架构)》中写过这样一句话:RISC-V的成果已经扩展到嵌入式计算之外,进入到了存储技术和HPC,表现出这种架构更广泛应用的趋势。这句话也在今年RISC-V欧洲峰会、中国峰会上由RISC-V International CEO Andrea Gallo所引用。

前不久,电子技术设计已经撰文探讨了现在RISC-V分别在HPC AI、汽车、嵌入式应用方向上的发展情况。之所以RISC-V能获得现如今的发展成果,与时代走向“应用导向”的芯片设计有莫大关联——RISC-V的开放、可裁剪、可扩展特性,令其能够更好地适配应用;与此同时,开放性也意味着社区合作,集众家之长来完善生态,令其有能力向现有市场统治者发起挑战。

Andrea在演讲中也说,时代已经从传统的SoC设计走向了“基于负载做设计(workload-designed)”,“专注于负载、设计出最好的架构,RISC-V就能做到。”这次电子工程专辑针对Andrea的采访中,我们就AI HPC的话题做了进一步的探讨——看看在高附加值、高难度的市场上,RISC-V的准备工作怎么样了。

Andrea Gallo, RISC-V International CEO

AI HPC应用发展进度如何?

RISC-V之父Krste Asanović(RISC-V International首席架构师,SiFive首席架构师,加州大学伯克利分校研究生院名誉教授)在峰会上说:“RISC-V是个能做一切的ISA,它将会是比任何ISA应用范围更广的指令集。”

虽然RISC-V中国峰会现场,不少企业和专家都认为RISC-V格外适配AI应用,但不得不承认,RISC-V现阶段在AI数据中心及其他HPC类的应用是相对受限的。虽然我们没有HPC市场不同指令集处理器的市场占比数据:但Omdia在峰会上呈现了一组2024年中国国内的MCU微控制器市场上,不同指令集在不同领域的份额数据,如下图所示。

许松(英富曼数据服务有限公司首席分析师)评论说,RISC-V已经在消费电子领域,尤其音频、可穿戴等领域表现出相当好的发展态势,“工业控制等市场也在持续积极布局”,“但部分高门槛、高附加值领域,如车用、高性能计算等,市场占比依旧较低。”这组数据可能参考价值不算太大,但仍然就RISC-V现阶段的微控制器主场,对RISC-V的市场地位有了个大致呈现。

不过许松也明确提到IP供应商正在诸如车规级、高性能计算、高速连接和AI加速器领域做相关布局。“RISC-V向下可以适配多样化轻量级端侧应用;向上发展可以适应高计算密集场景,提供优异能效比。”

所以Andrea在主题演讲中援引SHD Group的数据:2031年预计RISC-V SoC芯片出货量会达到200亿颗,并在SoC市场获得超过25%的渗透率。与此同时,RISC-V在消费、计算机、汽车、数据中心、工业、网络(networking)六个市场的份额会达到26%-39%之间。

在此之中,我们更想关注的还是AI HPC。首先要明确,这里的“HPC(高性能计算)”是广义的HPC,就像台积电在财报中把PC处理器也划归在HPC方向一样:在这一定义下,不同类型的数据中心(包括超算中心、企业计算数据中心、超级集群、云计算数据中心、AI工厂、边缘数据中心)都可算作HPC。

通常狭义的HPC可能仅包含其中的1-2类(尤指超算,解决诸如气候科学、流体动力学、核聚变反应等各类复杂问题...)。聚焦于AI方向时,AI HPC作为某种子类涵盖了各种智算数据中心,以及NVIDIA及不少GPU企业现在热衷于谈的“AI工厂”。

Andrea向我们介绍RISC-V在数据中心的近况:“这方面的新闻挺多的,包括Rivos、Canonical合作在数据中心领域提供可扩展的RISC-V解决方案;玄铁也发布了最新的服务器级别芯片(C930);Fedora数据中心的RISC-V Koji实例也上线了;进迭时空针对新一代AI应用开发了服务器CPU芯片V100;还有Ventana Veyron V2数据中心处理器...”

“最近在RISC-V生态内,我们批准了(ratify)服务器SoC规格,也在和服务器平台协作。价值就在于我们围绕着RISC-V核心定义了共同的硬件外围;一起对软硬件接口做定义和标准化;如此一来,操作系统供应商会更容易移植到RISC-V平台。”

针对狭义的HPC方向,Andrea除了谈到欧盟DARE SGA1项目——由巴塞罗那超算中心领衔,获得2.4亿欧元注资的基于RISC-V、针对HPC和AI的软硬件设施的超算堆栈,还提到“北京开芯院的香山项目也有基于RISC-V的HPC处理器”。“RISC-V在该领域的发展相比其他垂直市场都更快,很多研究实验室都在致力于HPC方向的工作。”

更具体到AI应用场景,“NVIDIA预计去年就出货了超过10亿RISC-V处理器;Ahead Computing首轮融资2.15亿美元;Axelera AI获得超过6100万美金的补助,用以开发用于高性能计算的AI chiplet与平台;晶心科技和Meta一起合作开发AI加速器......”“很多企业都在开发基于RISC-V、面向AI的创新架构。”

仅是RISC-V中国峰会主论坛,我们就看到了Tenstorrent、阿里达摩院、北京开源芯片研究院、知合计算、中兴微电子等企业或机构,谈到他们在HPC与AI应用方向基于RISC-V指令集的技术成果和产品规划。阿里巴巴达摩院玄铁负责人在演讲中就很有信心地表示,“我们要往HPC方向上发展”,“我相信基于这样的趋势,RISC-V在各领域都会三分天下”,包括“高性能、大算力领域”。

凭什么能在HPC AI领域发展起来?

知其然还要知其所以然:如果“然”是指“RISC-V正在AI HPC领域高速发展,乃至在未来有可能与x86和Arm三分天下”;那么“所以然”的关键就是“RISC-V究竟凭什么”了。

借用包云岗(中国科学院计算技术研究所副所长,中国开放指令生态(RISC-V)联盟秘书长,北京开源芯片研究院首席科学家)在峰会主论坛上提出的一个问题:“Arm用得好好的,为什么要换RISC-V?”这个问题的答案必然不单是由于RISC-V的开源特性可达成技术自主——虽然Andrea也特别提到RISC-V让企业不再需要被单一供应商绑定,“掌握自己的命运很重要”。如果RISC-V没有真正的技术或商业优势,那么在电子产业也只会叫好不叫座。

首个要素,必然是RISC-V指令集的灵活性。“灵活性让企业能够针对特定负载来开发创新解决方案。”“对于AI而言,RISC-V之所以能够产生吸引力,从定制开发角度来看就在于芯片设计者可以按照需要,对特定扩展做调整:留下有需要的、抛弃不需要的。”Andrea谈到,“如此一来,就能做到die size、功耗的最小化,同时针对需要在RISC-V处理器上跑的特定负载和操作做出性能优化。”

最近的报道文章里,我们已经对RISC-V指令集灵活性特性产生的成本、能效收益做了详细阐释。这一特性与时下“应用导向的芯片设计”是完美契合的。

所以我们才会看到NVIDIA现在的GPU芯片也选择采用RISC-V内核作为控制器——去年的RISC-V北美峰会上,NVIDIA曾经介绍过GPU之中用来进行计算资源、电源管理的RISC-V核心:根据不同的芯片复杂度,NVIDIA为GPU定制开发的RISC-V核心从10-40个不等;而且NVIDIA甚至还特别针对自家GPU,设计了至少3种RISC-V微控制器核心;并为了实现额外的性能、功能和安全性,开发了20+定制扩展...

Jim Keller(Tenstorrent首席执行官)和练维汉(Tenstorrent首席架构师)则都在不止一个场合提过,选择RISC-V就是因为其开放与灵活性。练维汉在2022年的RISC-V峰会上就说过,他在刚加入公司时,对ML处理器的companion CPU做评估。他去找了Arm询问能否支持某种特定的数据类型,Arm的答复是不行。据说Arm对于这种程度的支持需要2年时间的内部讨论和与合作伙伴之间的磋商。于是RISC-V很快成为新选择。

其次“在于商业模式”。“有关于RISC-V指令集的授权模式:我们的所有规格都是公开发布的。无论是硅谷、欧洲、印度,还是中国的任何人,都可以免费用上RISC-V规格和标准。”Andrea在采访中说,“随后他们就能基于RISC-V标准,在当地做开发了。”“初创公司也能更容易地基于RISC-V创造价值、快速打造创新产品。”

一方面,这带来了芯片设计成本的降低:包云岗在主题演讲中说,RISC-V的开放性,使用开源实现和开源工具链,能“结构性降低成本”。他举例谈到研发一款量产10万颗的64核服务器芯片,开发成本“保守估计7.5亿人民币”,其中“IP授权费用和版税约2.5亿人民币,占33%”。

如果“基于开源的联合开发模式,就能为企业降低30%左右的成本”,“企业完全可以将这些成本用在其他地方。RISC-V能够带给我们新机会。”

另一方面,这样的商业模式也意味着“合作”。“因为是全球标准,就能和所有RISC-V生态内的企业一起合作。”Andrea谈到,“在其他垂直领域投入在RISC-V生态的,也能为AI所用;大家都能受惠于诸多IP供应商的资源”...加上操作系统、基础软件、工具链、编译器等方面的资源共建,也更有机会挑战原有市场统治者。

Tenstorrent今年在演讲环节提到的“AI民主化”,以及自家软硬件各组件的全面开放开源,外加OCA(开放式chiplet架构)标准,强调的都在于多样化需求的AI应用面临芯片及系统开发、AI技术使用的高成本,故而需要藉由RISC-V整个生态的“合作”与“共建”,来做到AI使用成本的降低与“AI的普及”。这个逻辑的根基就是RISC-V生态合作产生的价值,也是x86、Arm这样的生态难以达成的。

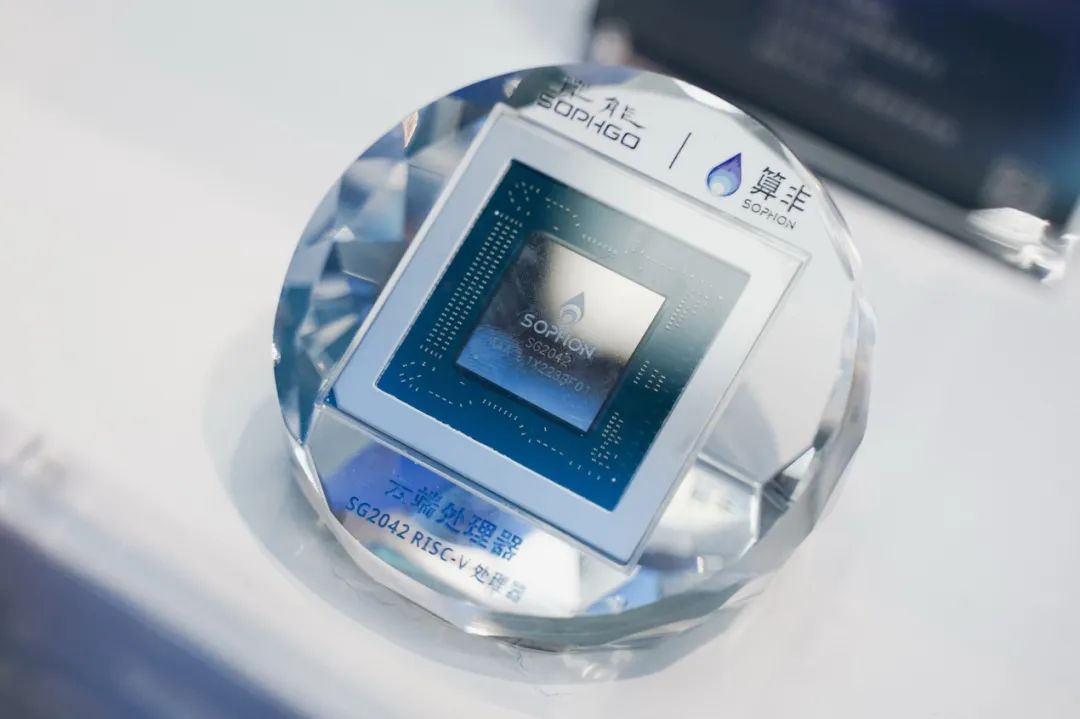

与此同时,我们认为同样重要的,还在于RISC-V标准的统一。在同时具备开放性,且标准统一的前提下,“投入到RISC-V的企业才会有信心构建未来和路线图。”这也是峰会上,算能这样在做HPC市场的企业认为,“合作”与“共识”将让RISC-V生态的参与者有机会挑战CUDA生态的原因。

标准与生态建设进度怎样?

而统一及标准化正是RISC-V International的重要工作之一,毕竟这涉及到整个生态的走向,也是谈论“合作”与“创新”的基础。Krste在主题演讲中特别汇报了RISC-V Profile的进展,除了去年10月刚刚批准的“RVA23作为RISC-V目前最重要的profile”,“是非常完整、具备竞争力的特性集”,“今年末到明年会有不同的RVA23硬件解决方案出现”。

Andrea也在采访中提及,RVA23指明了一系列强制和可选的新特性与扩展——这类profile的推进很大程度上能够确保不同RISC-V实施方案的软件相容性,属于处理器“基线特性集(baseline feature set)”般的存在,“对于降低移植软件的成本很重要”。他说RVA23是经过了长时间的开发、审视、认证流程的,毕竟需要适用于大量应用、系统软件生态。

RVA23包含不少得到批准的ISA扩展,比如说针对并行数据处理(尤其AI/ML)的矢量扩展(vector extension,RVV),针对虚拟化的hypervisor扩展,针对数值计算的某些浮点指令,用于代码密度的压缩指令,面向系统级性能的cache与内存管理扩展等...

规划中的下一个小更新是RVA23p1,只增加可选项——而且未来每年可能都会有1-2次小版本更新发布。Krste补充说,小版本更新的可选项都是为了给下一个大更新RVA30强制特性做准备——RVA30预计会在2-3年后发布(not expected for another 2-3 years)。

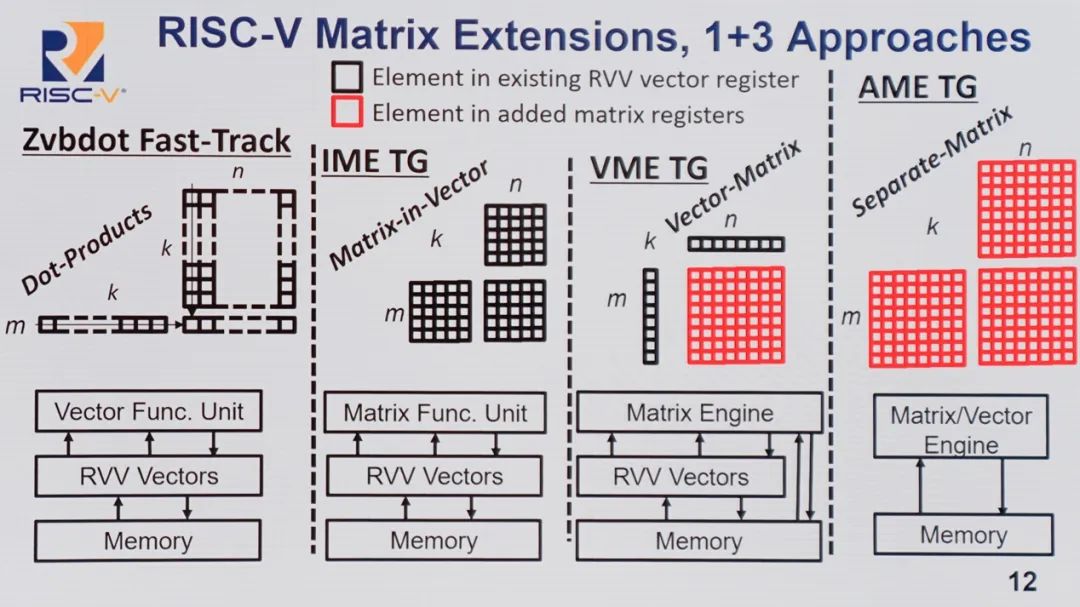

除了Krste相继提到DSP、>32b长指令扩展支持,针对AI尤为值得一提的是峰会现场不少人提到的矩阵扩展(matrix extension)——Andrea也在采访中数度提到RISC-V 正在做矩阵扩展,“矢量扩展、对BFloat 16数据格式的支持,还有矩阵扩展都能让AI推理直接跑在RISC-V处理器上,不需要外部NPU,提升了效率。”这本身就是体现RISC-V优势的扩展,“在CPU内部执行推理,避免内存拷贝、加速器延迟之类的问题;也就降低了功耗、减少了芯片尺寸。”

在论及HPC时,他补充说:“最近我们发布的RISC-V Vector C Intrinsics也能帮助开发者优化HPC库。”这里的RISC-V Vector C Intrinsics API能用于低层级C语言访问RVV指令,更细粒度控制矢量操作,故而有利于优化HPC库的性能和效率。还包括“我们为HPC提供hypervisor支持,甚至要考虑面向关键模拟仿真领域的超算算法,像是天气、地震预测等。”

“另外,性能、功耗不是唯一考量因素,还需要确保国家实验室、超算等应用场景所需的安全性。所以我们也跟成员合作,听取不同企业的需求。去年我们批准了面向安全和回弹性(resilience)的扩展:针对整体控制流完整性的pointer masking、landing pad、shadow stacks,还有supervisor域隔离、物理内存防护(PMP)、IO防护等。”“在面向HPC和数据中心时,还有像是RERI(RAS Error-record Register Interface)之类的扩展,RAS也是很重要的行业标准。”

“由于RISC-V的特性,我们能够快速为其增加价值、带来创新。我们的角色就是要确保协同所有成员,确保进化标准、发展RISC-V扩展,并在全球范围内对齐(aligned worldwide)。”

实际上,RISC-V International特别成立了AI/ML SIG(特别兴趣小组),“我们采用自下而上的方式来分析AI/ML处理需求、了解新op code(操作码)的加速;以及通过自上而下的方法,和平台合作,在框架层面来发现将RISC-V集成到所有ML框架中的最佳方式。”

不只是AI、HPC这类方向,在面向不同垂直市场时,RISC-V International内部会成立对应的SIG,“在SIG方面更进一步的投入,能够让我们和每个垂直领域的软件开发商、设备制造商、产品制造商一起协作。”毕竟不同垂直领域有着各自不同的平台生态与标准,“我们需要在这些领域理解软硬件之间的正确标准”,基于此构建共同标准,让RISC-V成为Krste所说“比任何ISA应用范围更广的指令集”。

除了指令集本身,在芯片真正面向应用开发者时,Andrea也谈到2024年在主要开源项目上,RISC-V面向关键开发者发出了将近300块板子;“我们也和学术机构、实验室一起,为开发者构建起可供远程访问的开发板。”

并且“我们针对RISC-V有着大量的、类别还在持续增多的在线培训课程,都是免费的,从基于RISC-V设计FPGA,到支持实时操作系统和Linux,以及开发驱动等”,“我自己最喜欢的是‘如何构建一个RISC-V CPU核心’...如果你刚刚接触RISC-V,跟着这些教程,你会感受到RISC-V之美,和这种架构的简洁。”

其他合作方面,“我们和诸多操作系统供应商,包括Yocto、Red Hat、Canonical等也都在合作。”“操作系统供应商已经完成了95%-100%的匹配度。”编译器方面,“我们和GCC, LLVM社区的合作也相当紧密。”比如在批准RVA23之时,就已经有面向GCC/LLVM的补丁来做出支持了。“针对参考模型、工具链增加所需支持是扩展批准的一个重要条件。”

而开发工具链的“某些工作会直接由RISC-V的成员完成,有些则会由RISE(RISC-V Software Ecosystem)项目去做”。比如RISC-V欧洲峰会上RISE副主席Barna Ibrahim谈到和RISC-V International的合作,除了编译器、runtime,上到应用层“最近我们组建了AI/ML工作组,去把PyTorch和Llama.cpp等移植到RISC-V架构上面来”。

如此一来,我们对于RISC-V生态的建设、标准的定义与设立,以及RISC-V的工作就有了个更全面的认识——当然我们这次的采访只聚焦在了AI HPC方向上。实际Andrea主题演讲中还特别提到了RISC-V在汽车、航天等不同垂直领域的发展,但整体模式和思路应该是大致相似的。

而更重要的是,在AI时代之下,我们也能更能理清为何RISC-V中国峰会的不少论坛活动上,有那么多发言人和专家形容“AI和RISC-V两者相互补充、促进”,甚至认定RISC-V是最适配AI芯片及应用的CPU指令集了——具备灵活性,又有统一标准,且有生态参与者合作共建,就是最直接原因。

“最后我想补充一点,RISC-V能够实现快速创新。”Andrea在采访最后说,“企业能够开发他们的定制扩展,在市场上快速创新;并且他们又能和RISC-V生态一起建立共同标准。因此这样的创新速度是唯有RISC-V能够做到的。”