英伟达 CPO 技术实现低功耗高速互联

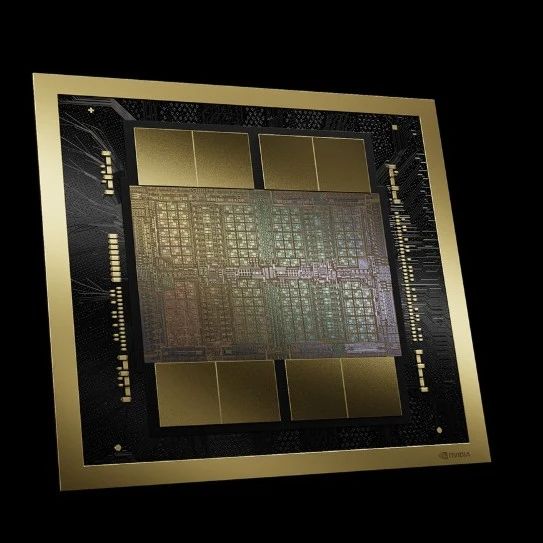

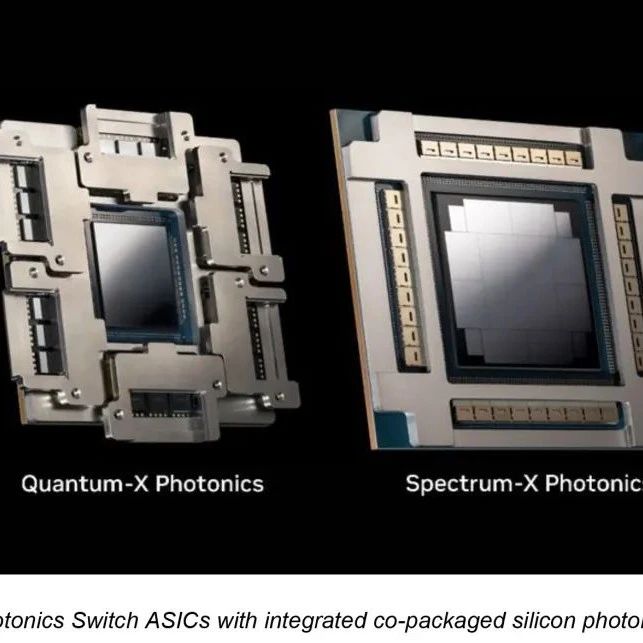

随着 AI GPU 集群规模持续扩大,跨网络层的通信需求正推动光通信技术的应用。今年早些时候,英伟达透露其下一代机架级 AI 平台将采用硅光子互连结合共封装光学(CPO)技术,以更低功耗实现更高传输速率。在今年的 Hot Chips 会议上,英伟达进一步披露了下一代 Quantum-X 和 Spectrum-X 光子互连解决方案的细节,预计 2026 年落地。

英伟达的技术路线图与台积电 COUPE 路线图高度同步,后者分三个阶段推进:第一代是适用于 OSFP 连接器的光引擎,支持 1.6 Tb/s 数据传输并降低功耗;第二代引入 CoWoS 封装的共封装光学,在主板层面实现 6.4 Tb/s 速率;第三代目标是在处理器封装内实现 12.8 Tb/s 传输,并进一步削减功耗和延迟。

为何选择共封装光学(CPO)?

在大规模 AI 集群中,数千颗 GPU 需协同工作,这对处理器互连提出挑战:传统方案中每个机架通过短铜缆连接架顶(ToR)交换机,而新架构将交换机移至行列末端,以构建跨多机架的低延迟统一网络。这一调整大幅延长了服务器与一级交换机的距离,当速率提升至 800 Gb/s 时,铜缆已无法满足需求,几乎所有服务器 - 交换机、交换机 - 交换机链路均需光连接。

英伟达指出,在这种场景下使用可插拔光模块存在明显局限:信号需先离开 ASIC,经电路板和连接器传输后再转换为光信号,这会导致严重电损耗 ——200 Gb/s 信道上损耗可达约 22 分贝,需通过复杂处理补偿,使单端口功耗升至 30W(进而需要额外散热并可能成为故障点)。随着 AI 部署规模扩大,这种方案几乎难以承受。

CPO 技术通过将光转换引擎与交换机 ASIC 集成,避免信号经长电迹传输,而是直接耦合至光纤,从而将电损耗降至 4 分贝,单端口功耗降至 9W。这种架构省去大量易损元件,大幅简化光互连部署。

英伟达称,借助台积电 COUPE 平台将光引擎直接集成到交换机芯片中,相比传统可插拔收发器,CPO 在效率、可靠性和可扩展性上实现显著提升:能效提升 3.5 倍,信号完整性提高 64 倍,因有源器件减少使弹性提升 10 倍,且由于维护和组装更简单,部署速度加快约 30%。

面向以太网与 InfiniBand 的 CPO 方案

英伟达将为以太网和 InfiniBand 技术同步推出基于 CPO 的光互连平台:

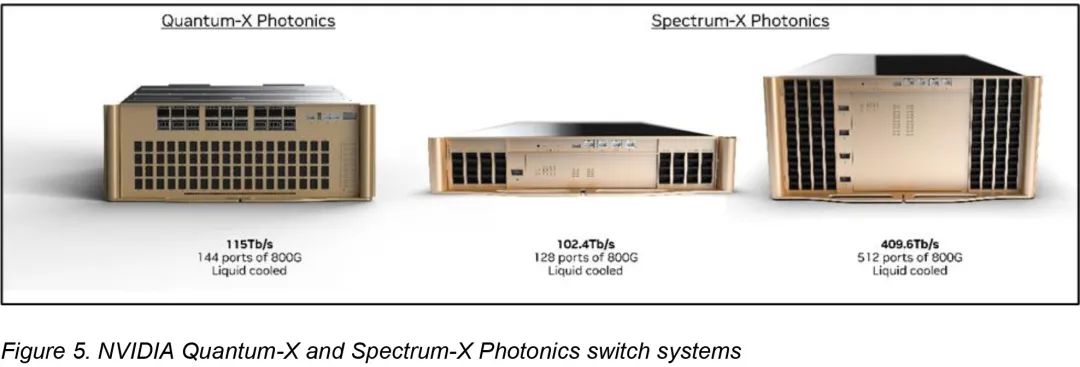

Quantum-X InfiniBand 交换机:计划 2026 年初推出,单交换机吞吐量达 115 Tb/s,支持 144 个 800 Gb/s 端口,集成具备 14.4 TFLOPS 网络内处理能力的 ASIC,并支持第四代可扩展分层聚合缩减协议(SHARP)以降低集体操作延迟,采用液冷设计。

Spectrum-X 光子平台:2026 年下半年面向以太网推出,基于 Spectrum-6 ASIC 打造两款设备:SN6810 提供 102.4 Tb/s 带宽(128 个 800 Gb/s 端口),SN6800 扩展至 409.6 Tb/s(512 个同速率端口),均采用液冷方案。

英伟达设想,基于 CPO 的交换机将为规模与复杂度不断提升的生成式 AI 集群提供动力。借助 CPO,这类集群可省去数千个离散元件,实现更快安装、更易维护和更低单连接功耗,使 Quantum-X InfiniBand 和 Spectrum-X 光子平台在开机时间、首 token 响应时间和长期可靠性等指标上显著优化。

英伟达强调,共封装光学并非可选增强功能,而是未来 AI 数据中心的结构性需求。这意味着该公司将把光互连技术作为对抗 AMD 等竞争对手机架级 AI 方案的核心优势 —— 这也解释了为何 AMD 近期收购了 Enosemi。

技术演进路线

值得注意的是,英伟达硅光子计划的演进与台积电 COUPE(紧凑型通用光子引擎)平台深度绑定。台积电第一代 COUPE 通过 SoIC-X 封装技术将 65nm 电子集成电路(EIC)与光子集成电路(PIC)堆叠集成。

台积电 COUPE 路线图分三阶段推进:第一代面向 OSFP 连接器光引擎,实现 1.6 Tb/s 传输并降低功耗;第二代采用 CoWoS 封装的共封装光学,在主板层面支持 6.4 Tb/s;第三代目标是在处理器封装内实现 12.8 Tb/s,进一步降低功耗与延迟。

欢迎加入 EETOP AI/GPU 等微信群

报名即将关闭

西门子EDA大会

8月28日 上海