随着人工智能(AI)、汽车电子和物联网(IoT)等应用的迅猛发展,把模拟、数字、射频等功能集成于单一芯片的数模混合信号芯片已成为主流趋势。此类芯片广泛渗透至生活与产业场景中,然而其首次流片成功率通常较纯模拟IC/数字IC低10%-30%。这是由于数字电路与模拟电路本身在设计方法学、验证难度和工艺要求等方面存在显著差异。数字电路通常基于标准单元库设计,重点高集成度和功耗优化;而模拟电路则依赖PDK,需全面考量器件的物理特性、噪声、失配等因素。

在数模混合芯片中,常见的Bug类型包括:

接口与时序问题:例如数模接口时序失配、信号电平不兼容;复位信号出现毛刺或异步复位恢复时序错误,致使寄存器进入亚稳态或控制逻辑异常;芯片上电时序、休眠唤醒流程设计不当,造成模块状态异常。

电源完整性问题:如同步开关噪声、地弹现象,以及电源噪声耦合至敏感模拟电路,当I/O或核心逻辑同时开关时,噪声通过电源/地网络传播,影响供电质量。

跨域交互问题:如数字辅助校准算法或控制逻辑存在缺陷,导致ADC/DAC微分非线性(DNL)与积分非线性(INL)超出规格等。

设计与制造失配问题:如前后仿结果与流片硅后测试结果不一致,寄生参数提取不完整或影响评估不足等。

为确保数字设计与模拟设计在同一芯片协同工作,必须进行复杂的电路设计和严格的数模混合仿真硅前验证。在芯片持续朝着更高集成度、更先进工艺节点迈进,且复杂度呈指数级增长的背景下,数模混合仿真验证工程师面临着三个关键维度的挑战:

仿真速度与精度的两难困境:数模混合芯片中的模拟部分需要晶体管级精度(如SPICE模型),而数字部分依赖高层次抽象(如Verilog/System Verilog)。不同抽象层次协同存在技术难点,仿真耗时极长。全芯片级仿真涉及海量计算,验证周期长达数周。为追求速度而在SPICE精度上妥协,可能引发流片后的灾难性后果。

数模接口跨域协同的复杂性:数模接口是功能失效的高频发生区域。模拟信号为连续的电压或电流值,而数字信号为离散的逻辑电平。不同仿真器间需要通过数模转换和模数转换接口来实现信号转换。接口精度(分辨率和转换速率)直接影响仿真结果的保真程度。若设置过于粗糙,将会引入误差;若设置过于精细,则会进一步降低仿真速度。怎样高效且精准地验证数字逻辑与模拟电路之间的交互,是对仿真工具跨域协同能力的极限挑战。

时间同步与容量极限的挑战:数字仿真器采用“事件驱动”模式,模拟仿真器采用“时间步进”模式。如何让数字仿真器在合适的模拟时间点“暂停”以交换数据,是复杂的调度难题。同步不准确会引发时序错误,比如在关键时刻遗漏毛刺或出现建立/保持时间违规。超大规模集成电路中上亿级晶体管的设计规模不断突破传统仿真工具的容量上限,全芯片级别的数模混合仿真变得极为困难。

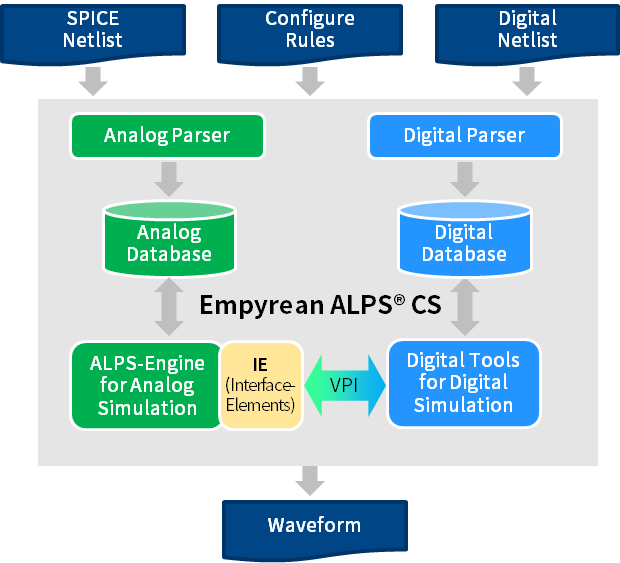

为应对上述挑战,华大九天推出了Empyrean ALPS® CS(Accurate Large capacity Parallel SPICE Co-Simulation)数模混合信号仿真工具。该工具基于 SPICE 精度的数模协同仿真架构,通过数模同步协同和并行技术突破等核心能力,大幅度提升数模混仿效率,为业界提供了一套在速度、精度与容量维度均具备优势的高效数模混合仿真验证解决方案。ALPS CS全面支持涵盖Verilog、SystemVerilog、VerilogA、VerilogAMS等主流硬件描述语言的前后仿真流程,并且能够依托LSF集群开展分布式仿真,从而从容应对复杂芯片的仿真验证挑战。

核心技术一:高效的数模接口跨域协同与时间同步机制

鉴于当前数模混合芯片中通常存在模拟域和数字域的多个反馈环路,数字设计与模拟设计呈现多层次融合,且相互作用复杂;ALPS CS通过多项关键技术研发以确保混合信号仿真高效性与结果可靠性:

标准接口兼容:支持借助VPI接口与数字仿真器实现无缝对接,同时能够解析Hspice、Spectre等多种模拟网表格式,可轻松融入现有的设计流程,降低工具替换的迁移成本以及工程师的使用难度。

精准数模同步技术:运用协同工作点收敛(Co-simulation Bias Point Convergence)与主从步长协同(Master-Slave Timestep Coordination)算法,精确掌控数字事件与模拟信号在交互界面的时序同步,杜绝因步长不匹配而导致的状态错误,确保跨域仿真的准确性。

智能接口元件(IE):具备内置自动化的数模/模数信号转换功能,依据配置精确模拟信号的上升/下降时间以及电压阈值,简化跨域验证设置流程,有效提升验证效率。

核心技术二:基于智能矩阵求解与并行计算的高速仿真引擎

仿真速度是决定验证效率的关键因素。ALPS CS传承了ALPS仿真器家族在性能方面的技术积累,并将其充分运用到数模混合仿真,通过智能矩阵求解以及高效的并行计算,进一步提高了大规模数模混合芯片的验证效率。

智能矩阵求解算法:与传统仿真器固定单一的矩阵求解模式不同,ALPS CS内置了数十种差异化的求解策略,具备华大九天独有的精度无损智能矩阵求解(Smart Matrix Solver)方案。在仿真过程中,该算法可实时动态分析电路的拓扑结构与电气特性,自主匹配并切换至最优求解方案,从底层提升求解效率。

多核并行技术:与传统方案无法并行的情况不同,ALPS CS采用业界领先的并行计算架构,能够高效调度多核CPU的硬件算力,对大规模电路的仿真任务进行精细化拆解和分布式并行处理,充分发挥硬件算力资源潜能。

核心技术三:数模混仿中集成大容量/高速/高精度的模拟仿真器ALPS

现代大规模集成电路的设计规模呈爆发式增长,对仿真工具的容量支持能力提出了极高要求。ALPS CS依托优化的内存管理机制,在遵循SPICE精度标准的基础上,能够稳定支持超过1亿个器件规模的超大规模电路仿真,满足复杂芯片设计的验证需求。

同时集成高速/高精度模拟仿真器ALPS,采用无损仿真技术,通过直接求解全电路方程,精确复现晶体管级的物理行为。其在信号传输特性、路径时序参数,及数模接口响应等方面,均可实现与芯片实测高度一致的仿真结果,为“一次流片成功”提供了核心技术支撑。

客户案例应用成效

ALPS CS已在多家客户的应用场景中成功落地,彰显出显著的速度优势。无论是器件数量仅25K的小规模DDR芯片,在进行前仿真时,现有方案需耗时2.1小时,而ALPS CS仅需0.6小时,加速比达到3.5倍;还是器件数量较多的大规模高速串行数据传输SERDES芯片,前仿真时现有方案需95.9小时,ALPS CS仅需20.0小时,加速比高达4.8倍,单次仿真可节省75.9小时。锁相环PLL在前仿真中的加速比可达3倍,后仿真加速比更是高达6.3倍。在其他诸如接收器RX、电源管理PMU等不同类型、不同规模的芯片仿真中,ALPS CS同样展现出显著的加速效果。由此可见,ALPS CS能够大幅缩短单次仿真的时间,进而缩短整体IC研发周期。

总结

ALPS CS的技术优势与应用价值

Empyrean ALPS® CS依托在仿真速度、精度和容量这三大核心维度的突破性技术革新,搭建起一套高效且可靠的数模混合信号验证体系。它借助高效的数模接口跨域协同与时间同步机制,充分确保数字仿真器和模拟仿真器实现“顺畅”通信。凭借独有的精度无损智能矩阵求解以及高效多核并行技术,在保证速度的同时不降低精度;通过优化内存管理,支持超1亿级数量的器件规模仿真。总体而言,ALPS CS的通过仿真速度提升,将单次混合仿真验证时长从“周”缩短至“天”。ALPS CS为复杂数模混合芯片设计的高效验证提供关键的EDA工具支持,尤其能够助力面临先进工艺挑战的芯片设计团队突破数模混合验证的瓶颈,大幅缩短验证周期,加速大规模数模混合芯片产品成功推向市场。

北京华大九天科技股份有限公司(简称“华大九天”)成立于2009年,一直聚焦于EDA工具的开发、销售及相关服务业务,致力于成为全流程、全领域、全球领先的EDA提供商。

华大九天主要产品包括全定制设计平台EDA工具系统、数字电路设计EDA工具、晶圆制造EDA工具、先进封装设计EDA工具和3DIC设计EDA工具等软件及相关技术服务。其中,全定制设计平台EDA工具系统包括模拟电路设计全流程EDA工具系统、存储电路设计全流程EDA工具系统、射频电路设计全流程EDA工具系统和平板显示电路设计全流程EDA工具系统;技术服务主要包括基础IP、晶圆制造工程服务及其他相关服务。产品和服务主要应用于集成电路设计、制造及封装领域。

华大九天总部位于北京,在南京、成都、深圳、上海、香港、广州、北京亦庄、西安和天津等地设有全资子公司,在武汉、厦门、苏州等地设有分支机构。