2025湾区半导体大会技术论坛总结报道:EDA/IP与IC设计论坛

作为芯片产业的核心支撑,EDA工具链的持续优化、IP核的创新突破,以及IC系统级集成的方法学演进,共同构成了数字经济的“技术底座”。在摩尔定律趋缓的背景下,如何通过EDA/IP与IC设计的协同创新,突破传统芯片设计的物理极限与效率瓶颈,已成为行业共同关注的命题。

今年的EDA/IP与IC设计论坛由清华大学路延教授主持,主题演讲嘉宾包括:

颖脉信息技术(上海)有限公司中国区生态负责人黄音

芯和半导体科技(上海)股份有限公司技术市场总监黄晓波

巨霖科技(上海)有限公司副总经理邓俊勇

芯华章科技股份有限公司高级研发总监刘军

灿芯半导体(上海)股份有限公司项目管理总监李想

奇捷科技(深圳)有限公司研发VP袁峰

深圳市比昂芯科技有限公司创始合伙人兼COO张汝民

端侧AI新时代的AI处理器需要达到什么样的能效?

当AI从云端走向终端,一场“端侧智能”革命正悄然发生——手机秒级响应的语音助手、实时监测健康的智能手表、自主避障的扫地机器人、工业产线边缘的轻量级推理设备……端侧AI以“低延迟、强隐私、低功耗”的特性,重新定义了人机交互方式。但这场革命的背后,藏着一个关键难题:传统架构难以兼顾端侧场景对算力效率、定制灵活性与成本控制的极致要求。

颖脉信息技术(上海)有限公司(IMAGINATION)中国区生态负责人黄音女士首先做主题演讲《端侧AI新时代》,深度拆解端侧AI爆发期的核心技术挑战(如能效比瓶颈、实时响应需求),并分享颖脉在典型场景中的实践洞察与未来布局。

Imagination E-Series NPU内核的AI加速性能高达200TOPS INT8。

集成系统EDA如何赋能Chiplet先进封装设计?

当先进制程逼近物理极限,Chiplet异构集成技术正成为芯片性能突破的新路径——通过将不同工艺、不同功能的芯片模块灵活组合,实现“性能-成本-良率”的最优平衡。但Chiplet的落地并非易事:多芯片互联的信号完整性、封装层面的热管理、系统级协同设计……每一个环节都充满挑战,而这正是集成系统EDA工具的价值所在。

芯和半导体科技(上海)股份有限公司技术市场总监黄晓波博士分享了《集成系统EDA赋能Chiplet先进封装设计》的主题,揭秘EDA如何加速Chiplet商业化,以及集成系统设计在先进封装时代的方法学革新。

多颗芯粒的高速互联是实现系统性能提升的关键。

EDA工具正从“辅助设计”升级为“驱动创新”的核心引擎,为Chiplet技术的规模化应用铺平了道路。

高速接口信号完整性sign-off仿真工具的破局尝试

随着芯片集成度与数据传输速率的不断提升,高速接口(如PCIe、DDR、USB4)的信号完整性问题已成为制约性能的关键瓶颈——信号衰减、串扰、时序偏移等问题,在复杂场景下可能导致芯片功能失效。传统仿真工具在应对高频、多物理场耦合时逐渐力不从心,行业亟需新的破局思路。

巨霖科技(上海)有限公司副总经理邓俊勇先生分享了《高速接口信号完整性sign-off仿真工具破局尝试》的经验,介绍巨霖科技如何通过技术创新解决复杂场景下的仿真难题,以及该工具的实际应用价值。

信号完整性签核仿真工具需要生态闭环。

高速接口设计的新视角——更精准的仿真工具,将成为保障芯片高性能互联的“安全锁”。

通过形式化验证工具实现数据通路完备验证

芯片设计复杂度的指数级增长,让数据通路验证的“完备性”成为关键命题——任何细微的逻辑漏洞,都可能导致芯片功能异常甚至系统崩溃。传统动态验证方法(如仿真、FPGA原型验证)在覆盖率和效率上逐渐触及天花板,而形式化验证凭借其数学严谨性,正成为解决这一难题的核心工具。

芯华章科技股份有限公司高级研发总监刘军先生做了《基于芯华章GalaxEC-HEC形式化验证工具实现数据通路完备验证》的主题演讲,揭秘该工具如何实现高效、全面的验证覆盖,以及在实际芯片设计中的应用实践。

芯华章形式化验证工具系列包括GalaxEC HEC、SEC和LEC。

形式化验证技术的突破,为芯片设计的可靠性提供了“数学级”保障,让我们看到了“零缺陷”设计的更多可能。

灿芯YouIP+YouSiP设计平台如何赋能定制芯片设计一站式解决方案?

当前,芯片应用正从消费电子向汽车电子、AIoT、工业控制等高复杂度场景快速延伸,定制芯片的需求呈现“高性能、低功耗、强场景适配”的爆发式增长。但传统设计模式中,IP选型分散、SiP集成低效、设计-验证-流片协同周期长等问题,严重制约了开发效率与市场响应速度。

如何破解这一瓶颈?灿芯半导体(上海)股份有限公司项目管理总监李想先生分享了YouIP+YouSiP设计平台,通过“IP标准化+系统智能化”双轮驱动,将定制芯片设计周期缩短30%以上、验证效率提升40%,并在汽车SoC、边缘AI芯片等领域落地多个成功案例。

YouIP+YouSiP平台让我们看到,定制芯片设计正从“个性化难题”走向“标准化高效”,为产业升级注入了强劲动能。

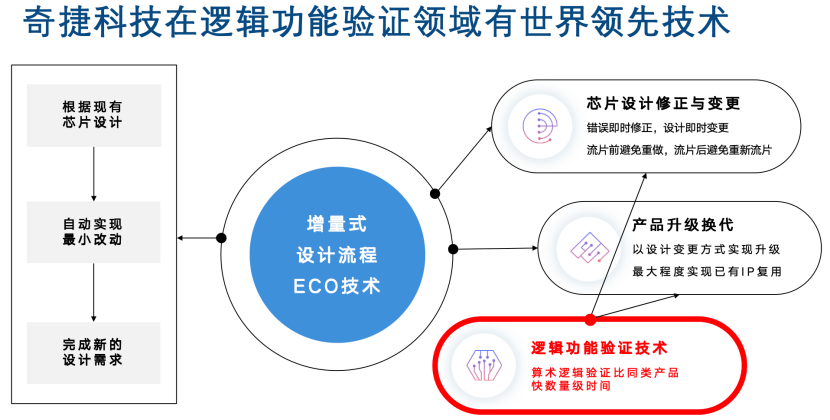

应对不同复杂度芯片设计的Functional ECO挑战与解决方案

随着芯片设计从简单功能模块向多核、多模块的系统级芯片演进,设计后期的功能变更(Functional ECO)成为“牵一发而动全身”的关键挑战——每一次微小的逻辑调整,都可能影响芯片的性能、功耗与面积。如何在不影响整体设计的前提下,实现高效、精准的功能变更?

奇捷科技(深圳)有限公司研发副总裁袁峰先生分享了《应对不同复杂度芯片设计的Functional ECO挑战与解决方案》,揭秘如何平衡效率、性能与成本,实现“无忧变更”。

奇捷科技独特的增量式设计流程ECO技术。

AI驱动的模拟电路自动化设计与仿真一站式平台

模拟电路设计是芯片设计中的“硬骨头”——设计周期长、调试难度大、对工程师经验依赖度高。但随着AI技术的飞速发展,模拟电路设计与仿真的自动化成为可能。通过AI算法优化参数搜索、预测电路行为,不仅能大幅提升设计效率与精度,更能降低对高端人才的依赖,推动模拟芯片的普惠化。

深圳市比昂芯科技有限公司创始合伙人兼COO张汝民博士带领团队打造的AI驱动平台,实现了模拟电路设计与仿真的全流程自动化,并在实际项目中验证了其价值。

AI与模拟电路设计的融合,正在打开芯片设计的“智能时代”,让我们看到了技术交叉带来的无限潜力。

结语

我们从端侧AI的终端革命出发,探讨了Chiplet先进封装如何突破制程极限;聚焦高速接口信号完整性,为芯片高速互联保驾护航;见证了形式化验证工具如何提升设计可靠性;体验了一站式定制平台如何加速芯片开发;应对了复杂芯片的功能变更挑战;更展望了AI驱动模拟电路自动化的未来。

EDA/IP与IC设计,是芯片产业的基石,更是智能时代创新的引擎。每一项技术的突破,都源于开发者们的智慧碰撞;每一次生态的进化,都离不开企业的深耕与行业的协同。

芯启未来,智创生态