大功率的 MOS 管驱动必须要考虑 MOS 管的米勒效应,MOS 管的米勒效应是物理特性决定的,只要 MOS 管存在 Cgd,就必然存在米勒效应。

先简单解释下 MOS 管的米勒平台,新入行的大部分工程师对米勒效应并不了解,对于一些小信号行业,或者小功率产品,低功耗产品从业者来说,甚至都没听过这个词,他们直观的认为,MOS 管的导通过程就跟反转 IO 信号一样自然,实际上并非如此。

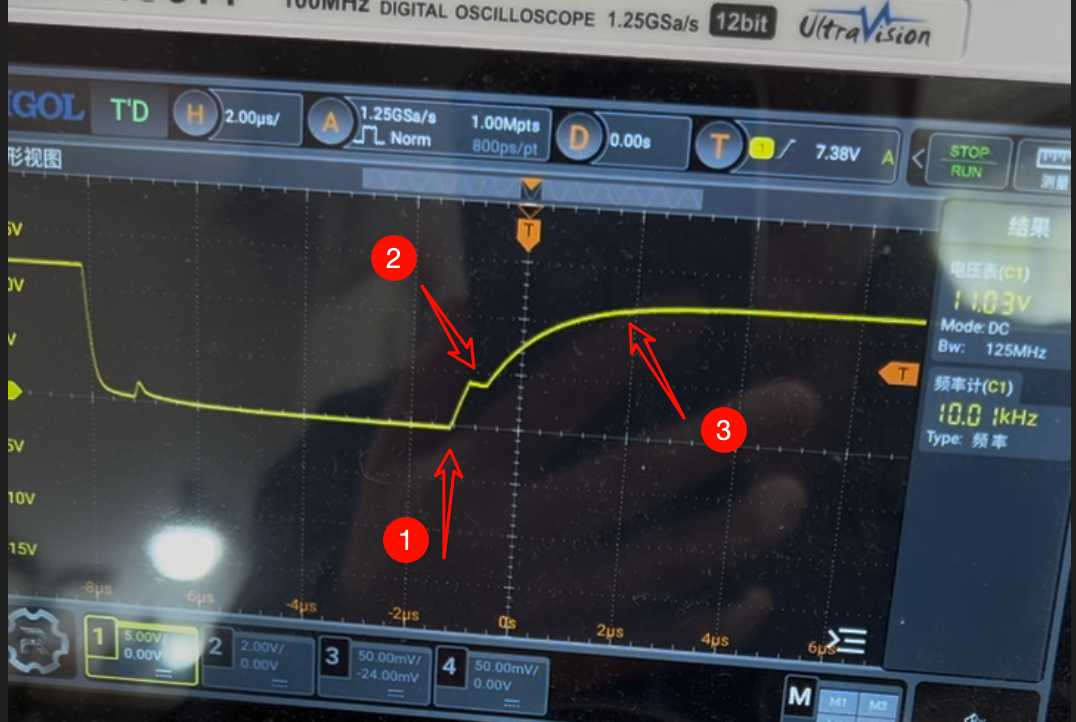

我们来看一下MOS 管在开通时,Vgs 上的真实的波形信号:

一个 MOS 在开启的过程中,它的 Vgs 电压会经历三个阶段,一些小信号处理的MOS,或者低功率的 MOS 管为什么测试没有这样的波形呢?那是因为时间轴展开的不够,只要波形放的足够大,就一定能看到这个平台。

下面,我们先分析一下,米勒平台时怎么形成的。这里我们针对硬开关驱动感性负载,软开关的米勒平台不在这里讨论。

在 t0 时刻,MOS 管的 Vgs 电压为 0,MOS 处于关闭状态,此时 Vds 电压为 VDD,也就是我们要控制的电压并没有通过 MOS 管给到负载端。

在 t1 时刻,Vgs 达到了 MOS 的开启电压 Vth,Vth 通常在 2-3V 的样子,MOS 管的这个参数一致性并不是很好,因此这是一个范围。

我们知道,MOS 管栅极的输入阻抗是无限大的,为什么波形是一个逐渐增加的波形呢?这是因为 MOS 管的栅极和源极之间存在寄生电容 Cgs,驱动 MOS 就是给这个寄生电容充电的过程。

通常此时,MOS 管的 Rdson 开始从无限大变小,MOS 管中流过的电流逐渐上升。Vds 也随之逐渐降低。

在 t2 时刻,Rdson 减小的最小值,因此漏源电流开始恒定为 Id,此时电流达到最大值,Vds 的电压将快速跌落,其跌落曲线根据负载不同而不同,也会受到栅极电流的影响,其最终将接近 0,也就是 MOS 管完全导通。

问题来了,为什么从 t2 开始,Vgs 电压不上升了呢? 看图:

因为,MOS 管的栅极和漏极之间还存在一个寄生电容叫做 Cgd,t2 时刻开始,我们的 Vgd 会根据负载的不同而下降到接近 0V(图中 S 接地参考点)。这个电压下降的过程中就会出现栅极电压要给 Cgd 充电的情况。如果这个充电的速度和 Vgd 下降的速度相同,那么就形成了一个电压持续不变的状态。

t2 到 t3 的持续时间不会很长,因为 Rdson 很小,当 Vgd 不在下降时,栅极电压将慢慢的给 Cgd 充电,直到 Vgs 到达驱动电压。

所以弥勒平台本质是漏极电压变化与栅漏电容的耦合,导致了栅极电压在某一个时间段被钉住了。

我们还可以发现,t0 到 t2 时刻的 Vgs 斜率比较陡峭,但是 t3 到 t4 时刻的 Vgs 斜率就缓和了很多,这是因为前一段主要是给 Cgs 充电,而后面一段是给 Cgs 和 Cgd 一起充电。

我们从开关功耗的角度来分析,哪几个阶段功耗最大呢?

MOS 的损耗公式为 P= U*I,也就是Vds * Id,那么可以看出,在开启的整个过程中,t1-t2 和 t2-t4 都会产生大量的热损耗。

在 t1-t2 阶段,Vds 还没有完全下降,但是电流 Id 是直线上升的,这个过程也是 Rdson 逐渐减小的过程。

在 t2-t3 阶段,Id 已经达到最大值,但是 Vds 还没有降低到最小,这也就是平台持续的过程。

因此我们要降低 MOS 管的开关损耗,主要是缩短 t1-t3 的时间。要想缩短 Vgs 爬升的时间,也就是要给两个电容充电的速度加快,最终还是需要我们加在栅极上的电流足够大才行。

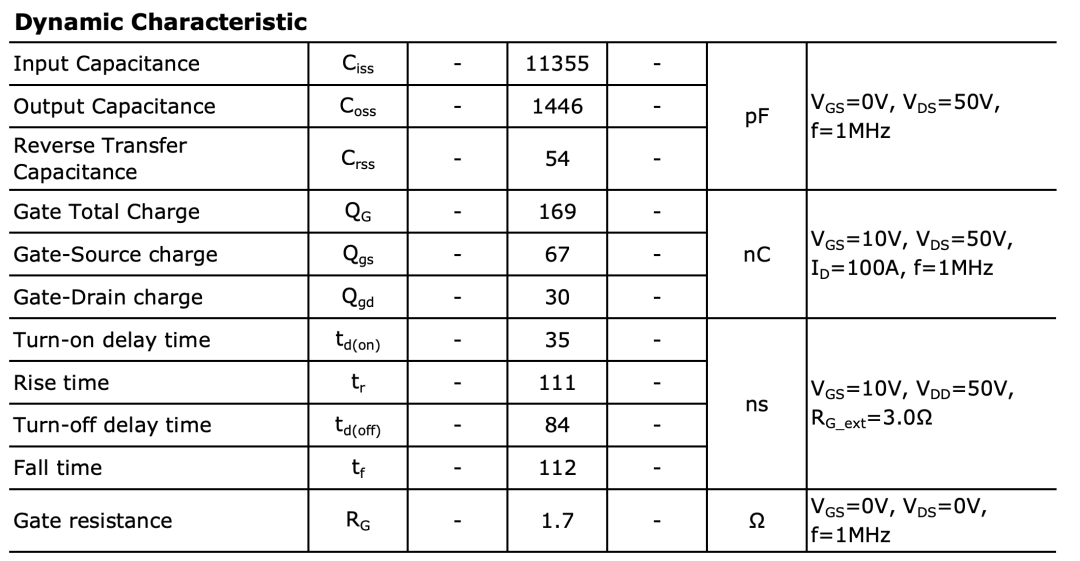

假设现在我们有一个 MOS 管参数是 100V,2mR 内阻,它的规格书提供下面的动态参数,我们来分析一下如何驱动这个 MOS。

图标中的 Ciss 可以看下图:

相同电压和内阻的 MOS,他们的寄生参数会根据工艺的不同而不同,所以要想降低 MOS 管的开关损耗,首先就要选择 Ciss 小的管子。

如果 MOS 管我们已经选好了,那么我们只能靠强大的驱动电流来降低开关损耗了,比如我们上面的所选的 MOS 管的 Qg 是标称 169nC,这是,如果我们给定 2A 的驱动电流,那么根据公式

T = Qg / I = 169nC/2A = 84.5ns

整个 Vgs 上升,包括米勒平台阶段,只需要不到 100ns。这只是理论时长,我们还要考虑栅极驱动的限流电阻,以及米勒电容两端不断攀升的电压,因此实际的时长往往更长。

![2025年中国无机颜料行业发展现状及未来趋势分析:在工业绿色转型与碳中和目标驱动下,行业正经历结构性变革[图]](https://xtechcon-static.oss-cn-chengdu.aliyuncs.com/xtimes/xtimes/images/2025-10-18/68f2e779a4deb.jpeg)

![2025年中国核电泵行业产业链、发展现状及未来趋势研判:装机目标驱动增长,行业规模有望突破420亿元[图]](https://xtechcon-static.oss-cn-chengdu.aliyuncs.com/xtimes/xtimes/images/2025-10-20/68f58aa012792.jpeg)