芯片制造过程中一个常被忽视的环节,正逐渐成为人工智能发展的下一个瓶颈。

每一枚用于驱动人工智能的微芯片都必须被封装到能够与外部世界交互的硬件中。但目前,几乎所有这一被称为先进封装的芯片制造环节都集中在亚洲,产能严重不足。

随着台积电准备在亚利桑那州破土动工兴建两座新工厂,以及埃隆·马斯克选择英特尔为其雄心勃勃的定制芯片计划供货,先进封装正成为关注的焦点。

“如果人们不积极主动地进行资本支出投资,以应对未来几年晶圆厂产能的激增,那么先进封装很快就会成为瓶颈,”乔治城大学安全与新兴技术中心的约翰·弗维表示。

台积电北美封装解决方案负责人保罗·卢梭在接受CNBC采访时罕见地表示,产能“正在大幅增长”。

目前最先进的封装技术是晶圆基板芯片封装(CoWoS),Rousseau 表示,该技术正以惊人的 80% 的复合年增长率快速增长。

人工智能巨头英伟达已预订了台积电(TSMC)大部分最先进的产能,台积电是封装领域的领军企业。

但英特尔的技术实力与这家台湾巨头不相上下。

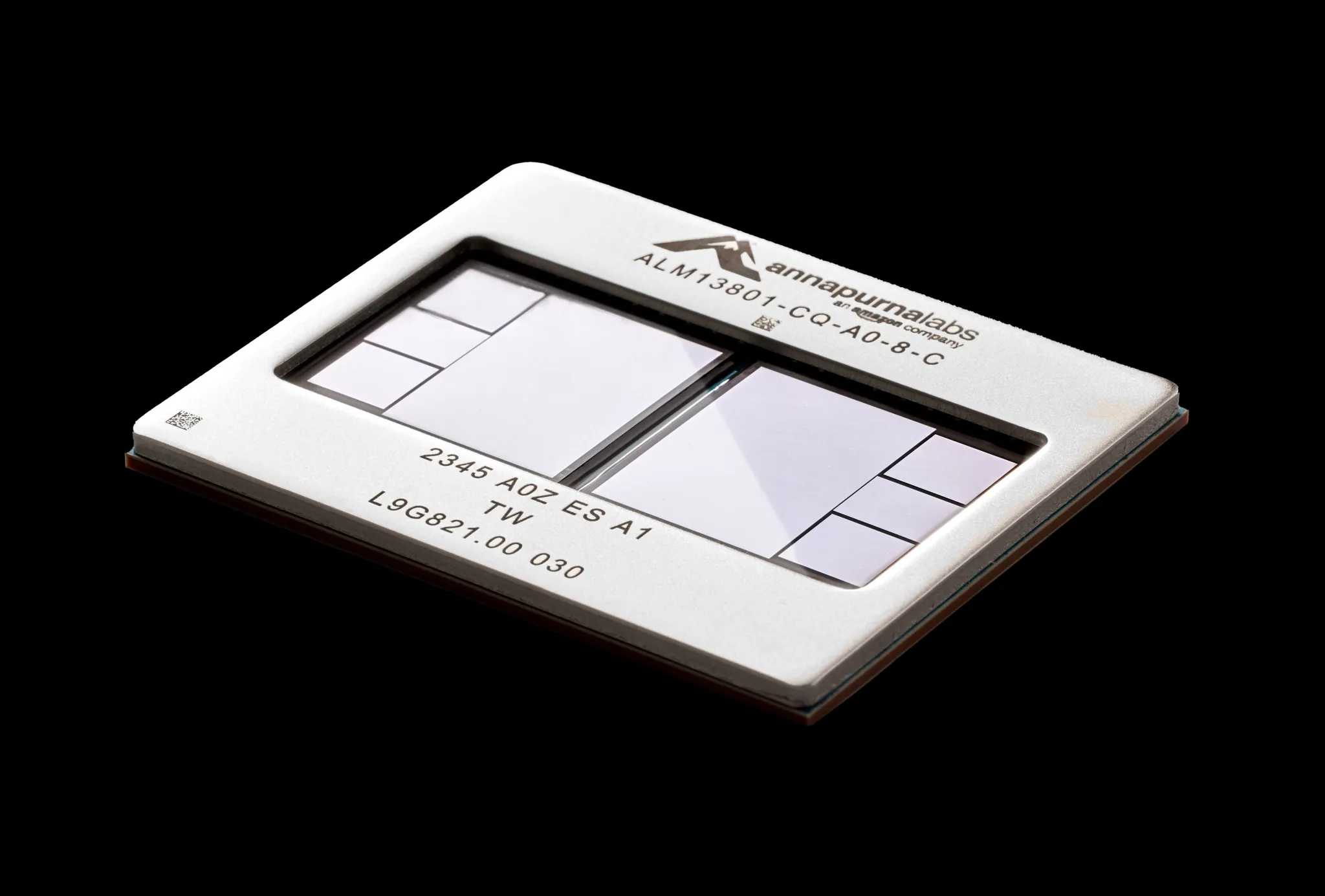

这家美国芯片制造商一直难以为其芯片制造业务找到重要的外部客户,但其封装客户包括亚马逊和思科。

周二,马斯克还委托英特尔为其计划在德克萨斯州建设的雄心勃勃的 Terafab 工厂封装 SpaceX、xAI 和特斯拉的定制芯片。

英特尔的大部分最终封装工序都在越南、马来西亚和中国完成。英特尔最先进的部分封装工序则在美国新墨西哥州、俄勒冈州以及亚利桑那州钱德勒市的工厂进行。随着人工智能 (AI) 的发展,芯片制造商竞相为推理工作负载打造最佳硬件,对芯片的密度、性能和效率提出了更高的要求,封装工艺也因此备受关注。随着晶体管密度接近物理极限,新的硅封装方法可以发挥作用。“这实际上是摩尔定律在三维空间中的自然延伸,”卢说道。几十年来,单个芯片(称为“芯片”)从单个晶圆上切割下来,封装成一个系统,然后连接到计算机、机器人、汽车和手机等设备。随着人工智能的出现,芯片的复杂性在过去几年里呈爆炸式增长,更先进的封装方法应运而生。如今,多个芯片(例如逻辑芯片和高带宽内存)被封装到一个更大的芯片中,例如图形处理器 (GPU)。先进的封装技术用于将所有芯片连接在一起,使它们能够彼此通信并与整个系统进行通信。“大约五六年前,几乎没人这么做,” Moor Insights & Strategy 的芯片分析师 Patrick Moorhead 表示,并补充说,封装过去常常被视为“事后考虑”的工作,公司会将其分配给初级工程师。“现在,显然我们知道它与芯片本身一样重要,”他说道。英伟达已预订了台积电领先的CoWoS技术的大部分产能,产能预订量如此之高,以至于据报道台积电已将部分工序外包给专注于流程中较简单环节的第三方公司,例如日月光(ASE)和安靠(Amkor)。日月光是全球最大的半导体封装测试外包公司,预计到2026年,其先进封装产品的销售额将翻一番。日月光正在台湾建设一座大型新厂,其子公司SPIL去年也在台湾为另一座新的封装厂举行了盛大的开业典礼,英伟达CEO黄仁勋也出席了典礼。台积电除了在亚利桑那州建设两座封装厂外,还在台湾扩建两座新的封装厂。目前,台积电100%的芯片都运往台湾进行封装,即使是那些在其位于亚利桑那州凤凰城的先进芯片制造厂生产的芯片也不例外。台积电没有透露美国封装厂的完工时间表。“在亚利桑那州的晶圆厂旁边就能拥有这种封装能力,会让客户非常高兴,”TechSearch International 的首席封装研究员 Jan Vardaman 告诉 CNBC。她补充说,这是因为这样可以避免在亚洲和美国之间来回运输,从而缩短周转时间。英特尔已经在亚利桑那州新建的先进 18A 芯片制造厂附近开展一些封装业务。这家美国芯片制造商尚未为其 18A 晶圆厂找到主要的外部芯片制造客户,但其代工服务主管 Mark Gardner 告诉 CNBC,自 2022 年以来,该公司已有封装业务客户,包括亚马逊和思科。英伟达也计划在英特尔进行封装业务,这是其对这家芯片制造商 50 亿美元投资的一部分。几周前,美国政府刚刚宣布将在 2025 年向英特尔投资 89 亿美元。“芯片公司希望向美国政府表明他们愿意与英特尔开展业务,而与英特尔合作风险最低的方式就是进行封装,”Moorhead 说。当被问及英特尔能否通过先进封装技术找到一家大型芯片制造客户时,加德纳表示,与一些客户“已经找到了突破口”。马斯克可能会成为英特尔芯片制造和封装技术的早期采用者。英特尔周二在领英上发布的一篇文章称,该公司“大规模设计、制造和封装超高性能芯片的能力”将帮助马斯克的Terafab实现其每年生产1太瓦计算能力以支持人工智能的宏伟目标。许多芯片,例如中央处理器 (CPU),采用 2D 封装。而像 GPU 这样更复杂的芯片则需要额外的封装方式,这正是台积电 (TSMC) 的 CoWoS 技术所擅长的领域,它是一种 2.5D 封装技术。对于这类芯片,一层被称为中介层的高密度布线可以实现更紧密的互连,从而使高带宽内存能够直接安装在芯片周围,有效消除通常所说的“内存墙”。“你无法在计算芯片内部容纳足够的内存来充分利用其性能。因此,当我们推出 CoWoS 技术时,我们能够以非常高效的方式将 HBM 内存紧贴计算芯片,”台积电的 Rousseau 表示。台积电于 2012 年率先推出了 2.5D 技术,此后该技术经历了多次迭代。台积电表示,英伟达 (Nvidia) 的 Blackwell GPU 是首款采用其最新一代 CoWoS-L 技术的产品。正是这最新的产能让所有人担忧,因为据报道英伟达已经预定了其中的大部分。英特尔领先的封装技术名为嵌入式多芯片互连桥(EMIB)。它的工作原理与台积电使用的工艺类似,但用硅桥代替了中介层。英特尔的加德纳表示:“通过将这些非常小的硅片嵌入到需要的位置,可以降低成本。”英特尔将其方法称为Foveros Direct,而台积电的方法称为系统级集成芯片(SoIC)。卢解释说:“现在我们不再将芯片并排放置,而是将它们一个叠一个地放置。”他补充道:“这样它们就能真正像一个芯片一样协同工作,从而带来更高水平的性能提升。”卢表示,我们还需要几年时间才能看到台积电采用SoIC封装的产品。与此同时,三星、SK海力士和美光等存储器公司拥有自己的先进封装工厂,利用3D封装技术将芯片堆叠成高带宽存储器。为了加快芯片的交付速度,存储器和逻辑芯片制造商也在寻求用一种名为混合键合的新方法,用铜焊盘取代凸点,从而提高堆叠芯片的数量。我们可以用焊盘到焊盘的连接代替凸点,这种连接方式的距离几乎为零,因此可以提高功耗性能,”Vardaman解释道。“由于最短路径就是最佳路径,因此也能提高电气性能。”

*免责声明:文章内容系作者个人观点,半导体芯闻转载仅为了传达一种不同的观点,不代表半导体芯闻对该观点赞同或支持,如果有任何异议,欢迎联系我们。

喜欢我们的内容就点“在看”分享给小伙伴哦~

![]()