关注公众号,点击公众号主页右上角“ · · · ”,设置星标,实时关注旺材芯片最新资讯

芯片封装流程是决定芯片性能与可靠性的关键环节,看似复杂却步骤分明。为助于直观理解这一重要过程,我们以传统封装芯片为例,用图片逐一展示 12 个关键环节,让抽象流程变得具体可感。

来料检查(Incoming Inspection)

来料检查,即 IQC(Incoming Quality Control),是芯片封装流程中保障原材料品质的第一道防线。这一步骤会对晶圆、引线框架、焊线及封装材料等核心物料,进行外观完整性、尺寸精度、电性能参数与成分构成的全面检测,确保所有原材料均符合预设的设计标准。唯有通过严格筛查,才能从源头规避后续封装环节可能出现的质量隐患。

晶圆来料检查

以晶圆为例,其检查过程涵盖多维度的严格筛查:利用光学显微镜对表面进行精细观察,排查是否存在污染、划痕或裂纹等影响质量的外观缺陷;通过轮廓仪或激光测距仪等精密仪器,准确测量晶圆的厚度与翘曲度,确保其物理尺寸符合封装要求;此外,还需开展电性能测试以验证其电气特性,以及进行成分分析来确认材料构成达标。

晶圆减薄,也称作 Wafer Thinning,其操作是运用金刚石砂轮对晶圆基材实施磨削处理,一般会将晶圆从最初 500~700um 的厚度缩减到 50~300μm。进行晶圆减薄,能够起到降低封装高度、提升芯片散热效率、改善电性能以及减少晶圆切割加工量等多方面的作用。晶圆减薄过程

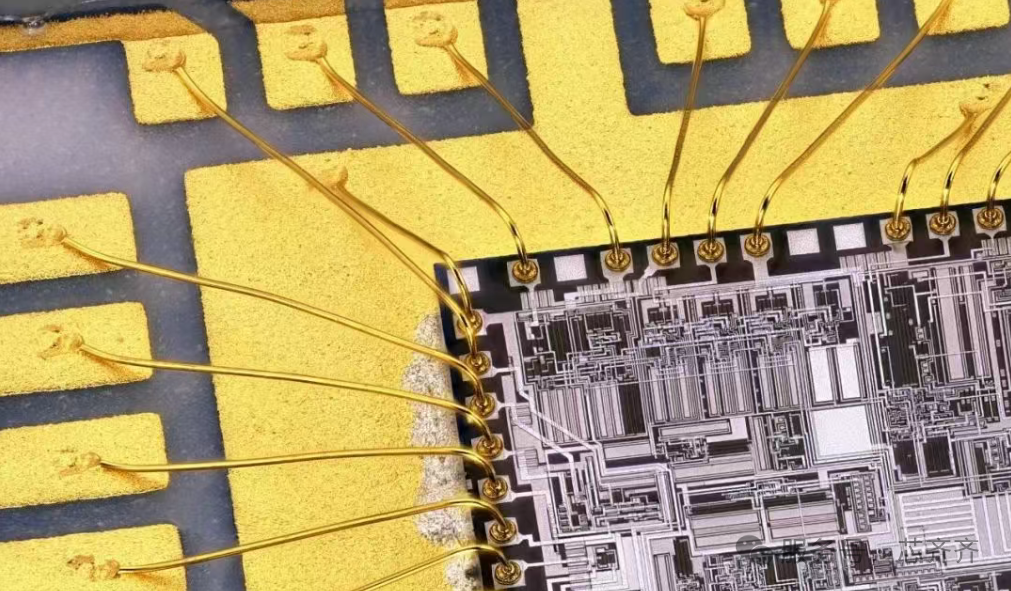

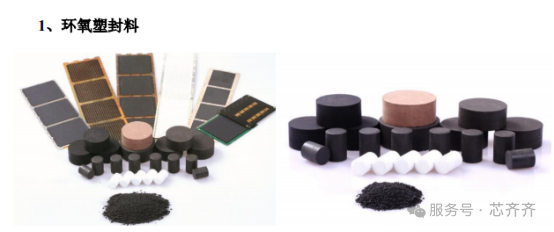

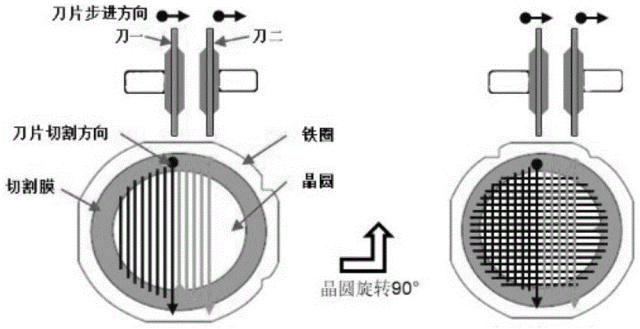

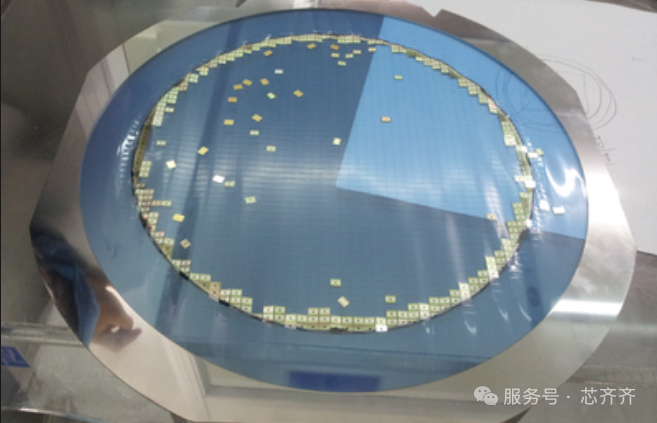

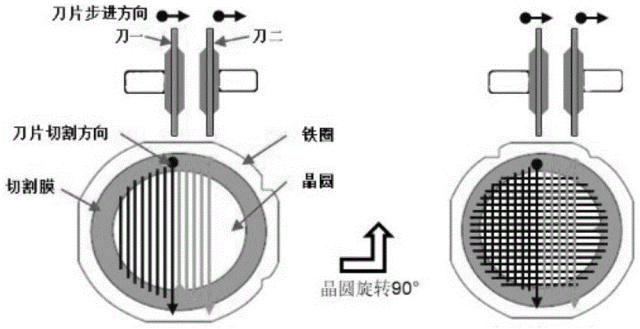

晶圆贴膜指的是先将胶带(像 UV 胶带或蓝膜这类)粘贴到晶圆背面,之后再把晶圆固定在金属环上的操作。这一步的关键作用在于,能有效防止在后续切割环节中芯片出现散落的情况。所使用的胶带既需要有足够强的粘性来稳固芯片,又要能在切割完成后,通过紫外线照射或者机械扩张的方式降低粘性,从而方便后续对芯片进行拾取。晶圆切割,又称作Wafer Sawing,是把整片晶圆分割成一个个裸芯片(Die)的工序。目前常用的切割方式主要有刀片切割与激光切割两种。其中,刀片切割是利用高速旋转的金刚石刀片进行机械切割,这种方式适用于常规的硅基晶圆,有着成本低、效率高的特点。切割过程中,搭配高精度光学对准系统(精度可达 ±1μm)以及去离子水冷却,能够有效保证切割的质量。 而对于厚度小于 50μm 的超薄晶圆,或是 GaAs、SiC 等脆性材料晶圆,激光切割则更为适合。作为一种非接触式切割方式,它能避免机械应力对晶圆造成损伤,还能实现更窄的切割道(<10μm),不过其设备成本相对较高。芯片贴装(Die Bonding),俗称固晶,具体是指通过导电胶或焊料,将裸芯片(Die)精准固定到引线框架上的过程。这一环节通常包含四个步骤:芯片拾取、胶水涂敷、芯片放置以及焊接固化,每个步骤都需精准操作以确保芯片与引线框架的稳定结合。如下图,芯片拾取是使用真空吸嘴从蓝色切割膜上吸取裸芯片,随后借助高精度视觉系统调整芯片位置,确保其与引线框架精准对齐;胶水涂敷:采用点胶或印刷工艺,将导电胶或焊料均匀涂布在引线框架的指定区域,为后续芯片的固定打好基础;引线键合是键合技术的重要分支,与之并列的还有倒装芯片键合(Flip Chip)、载带自动键合(TAB)和混合键合(Hybrid Bonding)等。其核心原理是借助热、压力或超声波的作用,通过细小的金属引线将芯片的焊盘与引线框架的焊盘连接起来,从而实现电气导通。在具体应用中,引线键合主要采用球形键合(Ball Bonding)和楔形键合(Wedge Bonding)两种焊接方式,业内常简称为球焊和楔焊。其中,球形键合(Ball Bonding)是通过高温电弧将金属线(如金线)末端熔化成球,再将其压焊到芯片焊盘上以形成电气连接的技术。该技术的特点是键合点强度高、接触电阻低,因此在引线键合中得到了广泛使用。而楔形键合(Wedge Bonding)则是通过超声波或热压方式,将金属线(如铝线)直接压焊到芯片或引线框架上的技术,无需预先将金属线末端形成球状。它的特点是键合点呈扁平状、间距更小,这使得它适用于高频或高密度封装场景。塑封成型是键合完成后的重要步骤,指的是用环氧树脂等塑封材料将键合好的芯片包裹起来,形成保护性外壳的过程。这一步骤的作用显著,既能为芯片提供可靠的机械保护,抵御外界的物理冲击和振动,又能实现电气绝缘,避免芯片与外部环境发生不必要的电气干扰,同时还能辅助芯片散热,保障其稳定工作。塑封成型的工艺流程为:预热→注塑→固化→后处理,这些流程都可以在全自动塑封设备内完成,高效且精准地实现对芯片的塑封保护。

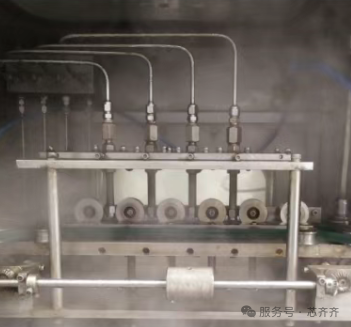

而对于厚度小于 50μm 的超薄晶圆,或是 GaAs、SiC 等脆性材料晶圆,激光切割则更为适合。作为一种非接触式切割方式,它能避免机械应力对晶圆造成损伤,还能实现更窄的切割道(<10μm),不过其设备成本相对较高。芯片贴装(Die Bonding),俗称固晶,具体是指通过导电胶或焊料,将裸芯片(Die)精准固定到引线框架上的过程。这一环节通常包含四个步骤:芯片拾取、胶水涂敷、芯片放置以及焊接固化,每个步骤都需精准操作以确保芯片与引线框架的稳定结合。如下图,芯片拾取是使用真空吸嘴从蓝色切割膜上吸取裸芯片,随后借助高精度视觉系统调整芯片位置,确保其与引线框架精准对齐;胶水涂敷:采用点胶或印刷工艺,将导电胶或焊料均匀涂布在引线框架的指定区域,为后续芯片的固定打好基础;引线键合是键合技术的重要分支,与之并列的还有倒装芯片键合(Flip Chip)、载带自动键合(TAB)和混合键合(Hybrid Bonding)等。其核心原理是借助热、压力或超声波的作用,通过细小的金属引线将芯片的焊盘与引线框架的焊盘连接起来,从而实现电气导通。在具体应用中,引线键合主要采用球形键合(Ball Bonding)和楔形键合(Wedge Bonding)两种焊接方式,业内常简称为球焊和楔焊。其中,球形键合(Ball Bonding)是通过高温电弧将金属线(如金线)末端熔化成球,再将其压焊到芯片焊盘上以形成电气连接的技术。该技术的特点是键合点强度高、接触电阻低,因此在引线键合中得到了广泛使用。而楔形键合(Wedge Bonding)则是通过超声波或热压方式,将金属线(如铝线)直接压焊到芯片或引线框架上的技术,无需预先将金属线末端形成球状。它的特点是键合点呈扁平状、间距更小,这使得它适用于高频或高密度封装场景。塑封成型是键合完成后的重要步骤,指的是用环氧树脂等塑封材料将键合好的芯片包裹起来,形成保护性外壳的过程。这一步骤的作用显著,既能为芯片提供可靠的机械保护,抵御外界的物理冲击和振动,又能实现电气绝缘,避免芯片与外部环境发生不必要的电气干扰,同时还能辅助芯片散热,保障其稳定工作。塑封成型的工艺流程为:预热→注塑→固化→后处理,这些流程都可以在全自动塑封设备内完成,高效且精准地实现对芯片的塑封保护。具体操作时,首先将引线框架置于模具当中,确保每个芯片都能对应一个独立的模腔;接着放入块状的 EMC(Epoxy Molding Compound,环氧树脂模塑料)材料;当设备加热至 150~180°C 时,EMC 材料会逐渐熔化并流入各个模腔,慢慢将芯片覆盖,最终实现完整包裹;之后经过降温处理,EMC 材料固化成型。

注塑流程示意图

或许有人会疑惑,既然注塑封成型的温度在 150~180°C,而 SMT 回流焊的峰值温度能达到 230~250°C,为什么芯片塑封不会熔化呢?这就要从塑封材料 EMC(环氧树脂模塑料)的特性说起。EMC 由环氧树脂、二氧化硅粉末和固化剂等成分构成,其中环氧树脂本身受热可以熔融,但在注塑过程中,它会与固化剂发生不可逆的交联反应,形成稳定的三维网状结构,这使得其耐温性能可达到 260℃,所以芯片在回流焊时依然能保持结构的完整性。

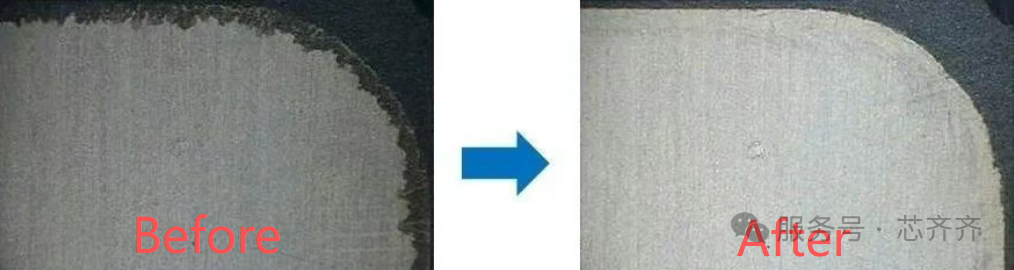

引脚处理包含去溢料(Deflashing)与电镀(Plating)两个部分。其中,去溢料也被叫做 “去飞边”,主要是清除塑封过程中溢出的多余模塑料。常用的去溢料方法多样,包括机械方式(像干式喷砂、湿式喷砂以及高压水流等)、激光处理、化学电解和溶剂浸泡等,通过这些方式可确保引脚区域的洁净与规整。电镀作为引脚处理的另一重要环节,是通过电化学沉积的方式,在芯片引脚表面形成一层金属镀层。这层镀层的作用在于提升引脚的导电性、可焊性与抗腐蚀性,从而保障芯片在后续使用中的稳定性能。目前常用的电镀工艺为化学镀镍和电镀锡。激光打标,又称激光雕刻(Laser Engraving),其原理是利用激光在芯片表面刻蚀信息,像厂家的标志、芯片型号、生产批次等内容都可以通过这种方式呈现。

在传统的封装工艺中,通常会选择在切筋成型这一步骤之前,直接在引线框架上对所有芯片进行统一打标,这样做的目的是为了提升整体的工作效率。而对于 BGA、WLCSP 这类采用先进封装技术的芯片来说,打标的时机则更为灵活,既可以在芯片切割成单个之后再进行打标,也能够将芯片放置在托盘内进行批量打标操作。

芯片丝印示例

切筋成型是引线框架类芯片独有的一道工序,它包含两个关键环节:切筋环节主要是去除引线框架外围的连接筋以及多余的溢料;而成型环节则是通过压制,将芯片的引脚加工成特定形状,比如直插形、鸥翼形和 J 形等。最终测试是针对完成封装的芯片所开展的全方位检测,这一过程通常会借助自动测试设备(ATE, Automatic Test Equipment)来进行。其测试内容涵盖广泛,主要包括电参数测试、功能测试、高低温测试以及老化测试等多个方面。芯片经过测试后,就进入到最后的包装环节。常见的包装方式主要有两种,分别是载带卷盘(Tape & Reel, T&R,通常被称为卷带)和托盘(Tray)。

其中,卷带包装是利用塑料载带与透明塑料膜来对芯片进行固定,之后将其卷绕成盘。这种包装方式便于 SMT 自动化贴片操作,比较适合小尺寸封装的芯片。而托盘包装则是采用带有矩阵式凹槽的塑料托盘来放置芯片,它适用于大尺寸、高引脚数的芯片,同时也能配合 SMT 自动化贴片使用。

为了确保芯片具备防潮和防静电的保护,载带卷盘与托盘需要被放入铝塑材质的防静电袋中进行真空密封处理。同时,袋内还会加入湿度指示卡(HIC)和干燥剂,以此进一步保障芯片的存储环境。经过以上从晶圆到芯片的12 道封装工序的逐步图解,此刻再观察芯片结构图,您是不是觉得每个部分的功能和位置都清晰易懂了呢?最后,用一句话对芯片封装的每个步骤做如下概括:

- 来料检查:对晶圆等原材料的质量进行查验,为后续生产打下坚实基础。

- 晶圆减薄:减小晶圆的厚度,让后续各道工序能够顺利进行。

- 晶圆贴膜:在晶圆上贴好蓝膜,避免切割时芯片出现散落现象。

- 晶圆切割:将晶圆分割成一个个独立的裸芯片,为封装工作做好前期准备。

- 芯片贴装:把裸芯片粘贴到引线框架上,完成初步的组装与固定。

- 引线键合:通过金属线将裸芯片和引线框架连接起来,搭建电气连接的通道。

- 塑封成型:使用 EMC 材料对芯片进行包裹,形成具有保护功能的外壳。

- 引脚处理:清理引脚上的溢料并进行电镀操作,提升引脚的性能。

- 激光打标:运用激光技术在芯片表面刻上厂家 logo、型号等标识信息。

- 切筋成型:切掉引线框架上多余的部分,同时将引脚压制成特定的形状。

- 最终测试:依靠专业设备对芯片的功能和性能进行全面检测,确保产品品质。

- 包装出货:采用卷带或托盘的方式对芯片进行包装,以便进行运输和出厂。

来源:1E实验室

而对于厚度小于 50μm 的超薄晶圆,或是 GaAs、SiC 等脆性材料晶圆,激光切割则更为适合。作为一种非接触式切割方式,它能避免机械应力对晶圆造成损伤,还能实现更窄的切割道(<10μm),不过其设备成本相对较高。

而对于厚度小于 50μm 的超薄晶圆,或是 GaAs、SiC 等脆性材料晶圆,激光切割则更为适合。作为一种非接触式切割方式,它能避免机械应力对晶圆造成损伤,还能实现更窄的切割道(<10μm),不过其设备成本相对较高。