公众号记得加星标⭐️,第一时间看推送不会错过。

作为当今半导体制造中常用的各种金属的替代品,钼的前景越来越光明,尤其是在前沿节点。

芯片制造商正在逐步淘汰先进节点上的金属。虽然钌衬垫已接近量产阶段,但这种金属还不足以取代高度可扩展互连中的铜。钌价格昂贵,目前的制造工艺也无济于事。此外,imec 研究员 Zsolt Tőkei 表示,镶嵌工艺中“过度沉积和抛光”步骤产生的废料量令人担忧。虽然减材金属化可以减少废料量,但它需要对整个工艺进行更大规模、更昂贵的改造。

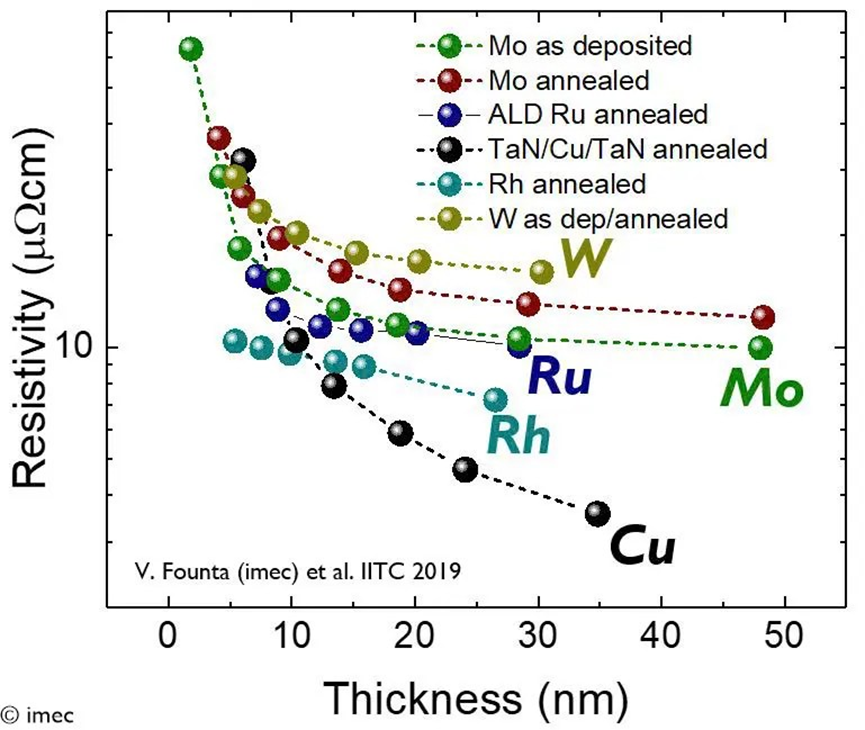

铜并非唯一一种寿命短的金属。晶体管触点、存储器中的字线以及类似应用通常使用钨、钴和其他金属,而不是铜。然而,它们面临着许多与铜相同的缩放问题。与铜一样,随着特征尺寸的缩小,钨的电阻率也会增加。它还需要一个阻挡层来避免电介质污染。在 3D NAND 器件中,Kioxia 的研究人员报告称,通常用于钨沉积的 WF 6前体中的氟残留物会滞留在空隙中,最终侵蚀周围的电介质材料。随着特征尺寸的缩小和电流密度的增加,钨也面临电迁移问题。

那么下一步是什么?对于这些应用来说,至少目前而言,一个越来越有吸引力的选择似乎是钼。Tőkei 表示,钼相对于现有材料和钌等替代品都具有多种优势。钼的电阻率比钨更高,不需要阻挡层,而且与钌相比,钼更便宜,并且与电介质的附着力更好。

在混合金属化方案中,钼作为无阻挡层接触金属尤其具有吸引力,因为预填充通孔后接铜镶嵌线。由于通孔底部或其他垂直特征的阻挡层会产生额外的串联电阻,因此底部阻挡层决定了接触和通孔的电阻。

Lam Research高级半导体工艺与集成工程师 TaeYeon Oh及其同事证明,无障碍混合钼方案相对于传统的铜双镶嵌设计,可将总电阻降低约 56%。他们的研究成果在最近的 IEEE 互连技术会议上进行了展示。

Tőkei表示,将钼与这样的工艺流程集成,除了金属沉积模块本身之外,可能只需要进行少量改动。钼比钌更容易氧化,因此更容易通过CMP去除。

然而,比利时微电子研究中心 (imec) 的 Jean-Philippe Soulié 及其同事进行的深入分析警告称,金属的本体特性在评估其在实际器件中的性能方面价值有限。对于钼——以及其他纳米线——其电学、热学和电迁移特性均取决于沉积薄膜的晶粒尺寸和晶界结构。而这些又取决于前驱体、工艺参数、底层电介质的表面特性等等。

管理电迁移界面和晶界是电迁移的主要途径,同时也会导致电子散射和电阻率下降。

为了集成钼,金属沉积模块需要能够处理 MoO2Cl2 和 MoCl5 等固体前驱体。固体前驱体在半导体制造中越来越常见,除了钼之外,还有基于氯的铪、铝和钨等前驱体。然而,与气体甚至液体前驱体相比,固体前驱体往往热稳定性较差,材料通量也不太均匀。

Lam Research 的研究人员在其工艺工程师 David Mandia 的报告中表示,他们通过循环沉积技术实现了精确的晶粒尺寸控制,并根据需要混合使用热法和等离子法工艺,以达到预期效果。他们表明,大晶粒钼薄膜对于成功集成至关重要。在他们的研究中,小晶粒钼的电阻率与厚度的依赖性与钨相当。相比之下,大晶粒钼的电阻率对厚度的依赖性要小得多,并且在厚度低于约 7 纳米时优于钨、钌,甚至铜。

当钼中存在晶界时,掺杂钴等元素有助于减少散射,正如韩国科学技术院的研究人员Yeongjun Lim和Mincheol Shin进行的模拟研究所示。在低浓度下,由于电荷补偿效应,电阻率下降。然而,在较高浓度下,电阻率急剧上升。额外的杂质态导致载流子局域化,从而扰乱了电子传输。

在背面电源应用中,预测金属行为尤其具有挑战性。背面电源设计旨在减小标准单元尺寸。然而,这会导致背面电源网络增加电流密度,从而增加电迁移的风险。由于类似的原因,它们也容易出现热点。

虽然背面功率配置中的电迁移和散热问题尚未得到彻底分析,但钼具有一些明显的优势。作为一种难熔金属,即使在极高的温度下也具有机械稳定性。它与电介质的附着力更强,不易形成空洞。此外,钼的导热性也比钌更好。由于所有这些原因,钼的抗电迁移性能可能比钌更好,尽管这两种金属的性能都应该令人满意。中山大学研究员蔡琳琳解释说,更好的抗电迁移性能使设计人员能够更紧密地封装晶体管,从而减少器件的整体面积。

虽然还需要更多实验结果,但早期的钼集成研究已颇具前景。Kioxia 团队发现,钼相对于钨的电阻率较低,这使得他们能够在保持 RC 不变的情况下将字线间距减小 7.3%。存储器孔间距缩小了 3.7% 以上,总体比特密度提高了 16.3%。

总体而言,Tőkei 表示,钼非常适合用于接触和字线应用。它与现有的集成方案非常契合。但从长远来看,钌或许可以扩展到更小的器件。

参考链接

https://semiengineering.com/scaling-memory-with-molybdenum/

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

END

今天是《半导体行业观察》为您分享的第4161期内容,欢迎关注。

推荐阅读

加星标⭐️第一时间看推送,小号防走丢