公众号记得加星标⭐️,第一时间看推送不会错过。

在日前的TSMC OIP生态论坛上,台积公司资深院士兼研发/设计与技术平台副总裁Dr. LC Lu在一个演讲中指出,人工智能的普及推动了电力需求的指数级增长。从超大规模数据中心到边缘设备,人工智能正渗透到各个领域,为日常生活中的各种新应用注入新的活力。

这些不断发展的模型,包括具身人工智能、思维链推理和代理系统,需要更大的数据集、更复杂的计算和更长的处理时间。这种激增导致人工智能加速器在五年内每封装功耗增加了3倍,部署规模在三年内增加了8倍,因此能源效率对于人工智能的可持续增长至关重要。

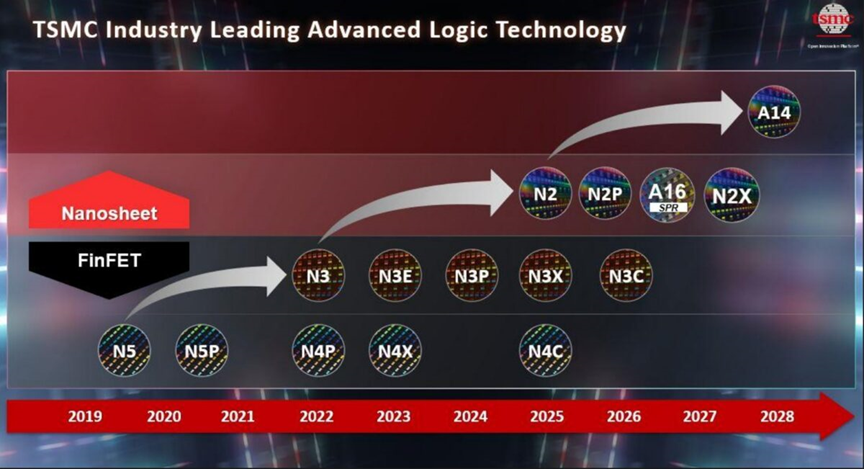

对此,台积电把战略重点放在先进逻辑和3D封装创新,并结合生态系统协作,以应对这一挑战。从逻辑微缩开始,台积电的路线图非常稳健:N2将于2025年下半年投入量产,N2P计划于明年投入量产,A16将于2026年底实现背面供电,A14则进展顺利。

至于N3 和 N5 的增强功能持续提升价值。从 N7 到 A14,等功率下的速度提升了 1.8 倍,而功率效率提升了 4.2 倍,每个节点的功耗比上一代降低约 30%。A16 的后端功耗针对的是具有密集网络的 AI 和 HPC 芯片,与 N2P 相比,速度提升 8-10%,功耗降低 15-20%。

N2 Nanoflex DTCO 优化了高速低功耗双单元设计,实现了 15% 的速度提升或 25-30% 的功耗降低。基础 IP 创新进一步提升了效率。优化的传输门触发器(transmission gate flip-flops)在速度(2%)和面积(6%)的权衡下,功耗降低了 10%,有时甚至优于状态门变体(state gate variants)。

双轨(Dual-rail) SRAM 搭配 Turbo/Nomin 模式,效率提升 10%,Vmin 降低 150mV,同时优化了面积损失。内存计算 (CIM) 技术脱颖而出:台积电基于数字 CIM 的深度学习加速器,相比传统 4nm DLA,可提供 4.5 倍 TOPS/W 和 7.8 倍 TOPS/mm² 的计算性能,并可从 22nm 扩展到 3nm 及以上。

台积电表示,AI 驱动的设计工具进一步放大了这些优势。

据介绍,新思科技的 DSO.AI在强化学习 PPA 优化方面处于领先地位,能将 APR 流程的电源效率提高了 5%,金属堆栈的电源效率提高了 2%,总计提升了 7%。对于模拟设计,与台积电 API 的集成可实现 20% 的效率提升和更密集的布局。AI 助手通过自然语言查询获取电源分配洞察,将分析速度提升 5-10 倍。

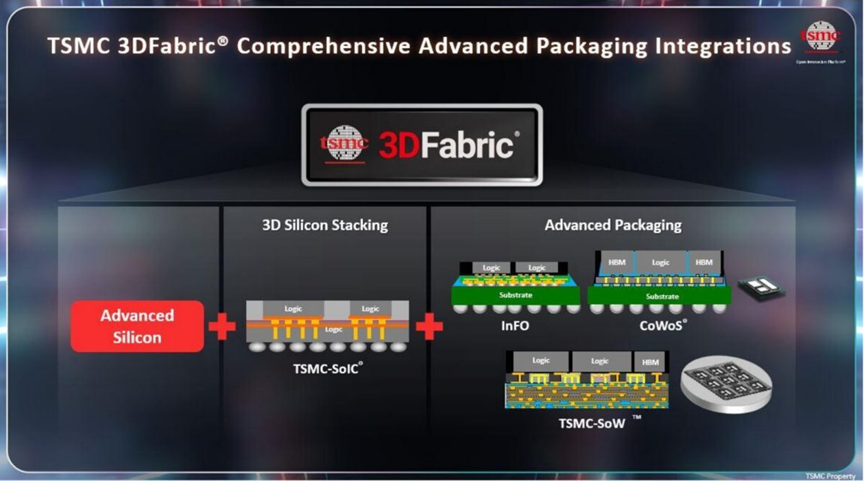

与此同时,台积电的 3D Fabric 技术已转向 3D 封装,包括用于硅片堆叠的SoIC 、用于移动/高性能计算 (HPC) 芯片集的InFO 、用于逻辑-HBM 集成的CoWoS,以及用于晶圆级 AI 系统的 SoW。

节能通信方面,2.5D CoWoS 的微凸块间距从 45µm 降至 25µm,效率提升 1.6 倍。3D SoIC 的效率比 2.5D 提升 6.7 倍,但集成面积较小(1 倍光罩 vs. 9.5 倍)。

至于符合 UCIE 标准的 Die-to-Die IP 也可从 AlphaWave 和新思科技等合作伙伴处获得。

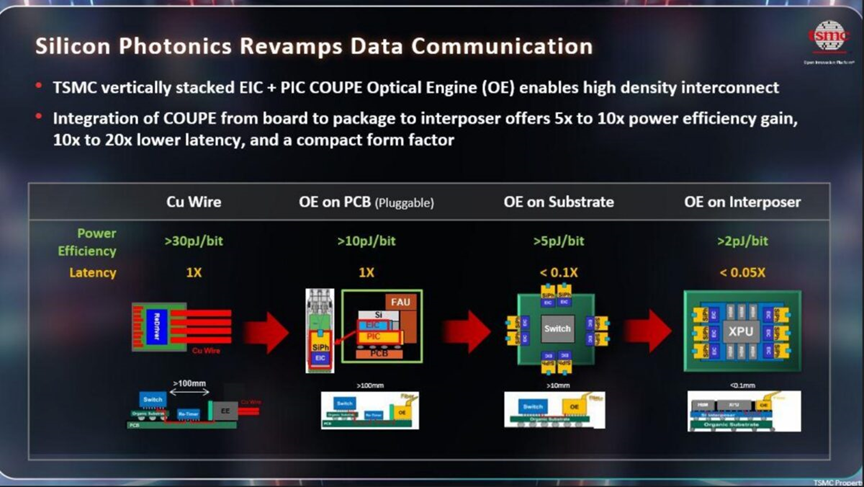

HBM 集成技术不断进步:台积电 N12 逻辑基片上的 HBM 4 可提供比 HBM3e DRAM 基片高 1.5 倍的带宽和效率。N3P 定制基片将电压从 1.1V 降至 0.75V。通过共封装光学器件实现的硅光子技术,相比可插拔式设计,效率提升 5-10 倍,延迟降低 10-20 倍,并且外形更加紧凑。Synopsys/ANSYS 的 AI 优化通过协同设计将效率提升了 1.2 倍。

采用超高性能金属-绝缘体-金属和嵌入式深沟槽电容器的去耦电容创新技术,可在不损失完整性的情况下实现 1.5 倍功率密度,该技术由 Synopsys/ANSYS 工具建模。EDA-AI 可实现 EDTC 插入(生产效率提高 10 倍)和基板布线(生产效率提高 100 倍,同时保持最佳信号完整性)的自动化。

总结而言,摩尔定律依然有效。从 N7 到 A14,逻辑微缩使效率提升了 4.2 倍,CIM 提升了 4.5 倍,IP/设计创新贡献了 7-20%。从 2.5D 到 3D,封装效率提升了 6.7 倍,光子技术提升了 5-10 倍,HBM/去耦电容技术进步提升了 1.5-2 倍,而 AI 则将生产效率提升了 10-100 倍。

参考链接

https://semiwiki.com/semiconductor-manufacturers/tsmc/362030-tsmcs-push-for-energy-efficient-ai-innovations-in-logic-and-packaging/

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

END

今天是《半导体行业观察》为您分享的第4176期内容,欢迎关注。

推荐阅读

★

★

★

★

★

★

★

★

加星标⭐️第一时间看推送,小号防走丢