PCB设计不是堆砌电路,而是一个“细节筑基”的系统工程。你可能因为一个焊盘出线不对称,造成器件立碑;也可能因为一个信号跨分割,导致整块板子EMI爆表……

今天这篇文章,我们不讲空理论,只讲那些让无数工程师抓狂的实战细节陷阱!

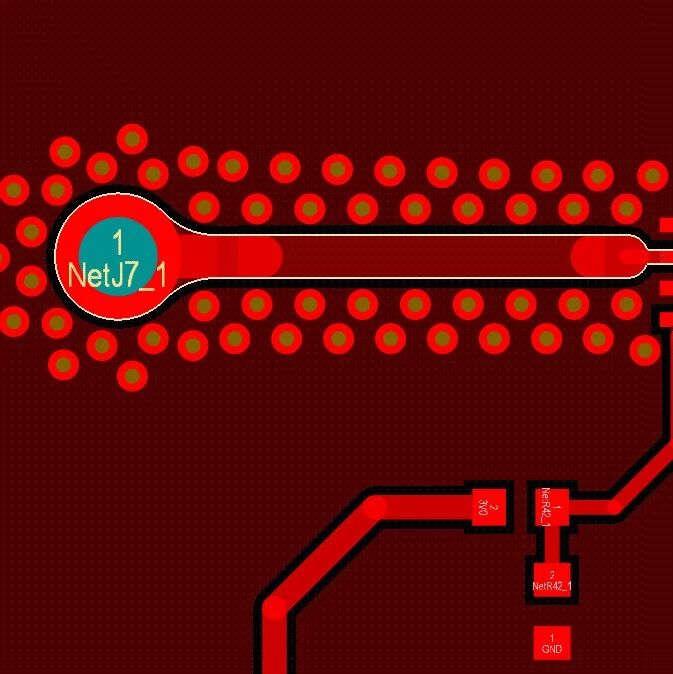

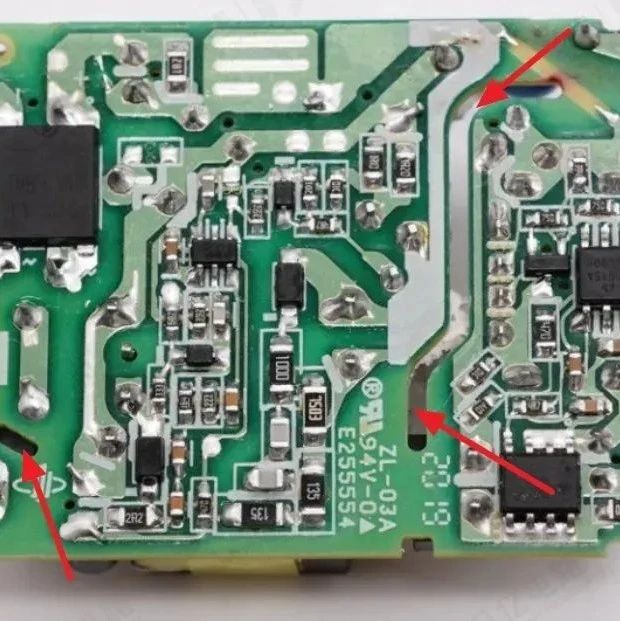

在开关电源类PCB中,往往存在高压强电与低电压弱电共板设计。这时,强电部分(如MOS管、功率电感)与控制信号(如PWM、反馈信号)必须严格分区,避免高电压噪声“窜入”控制电路,导致误动作,甚至炸板。

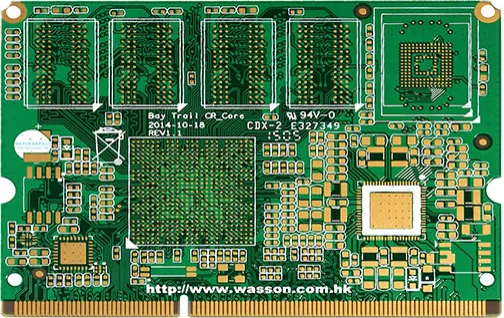

图1 — 强弱电信号隔离布局

晶体振荡器输出能力有限,尤其在高速数字系统中,晶振远离主控芯片会导致:

信号衰减

方波畸变

时钟不同步,系统卡顿

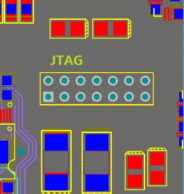

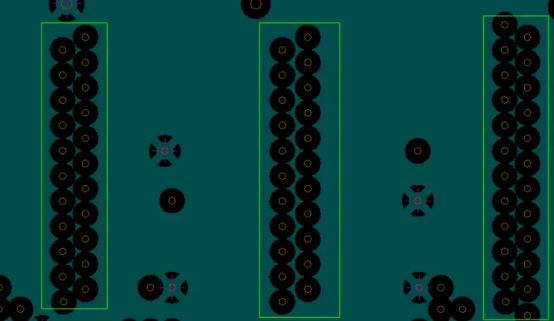

比如你在设计一个8路输入、8路驱动的控制板,模块重复性高,推荐使用PCB设计软件中的“模块复用”功能,统一布局、对称布线,不仅节省时间,还大大降低出错率。

图3 — 模块复用对称布局

调试时,你的手、你的探针、你的热风枪都需要空间!

小器件旁边不要放大器件,避免遮挡

可调电阻、电容、跳线器件旁留空

插件元件避免交叉重叠

图4 — 便于调试的元件排布设计

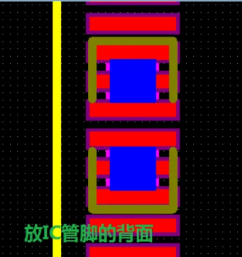

电源进入芯片的瞬间,可能伴随电压波动、尖峰噪声。去耦电容就是芯片的“安全气囊”,吸收这些波动。

电容靠近IC电源引脚(越近越好)

形成电源—电容—地最小闭环

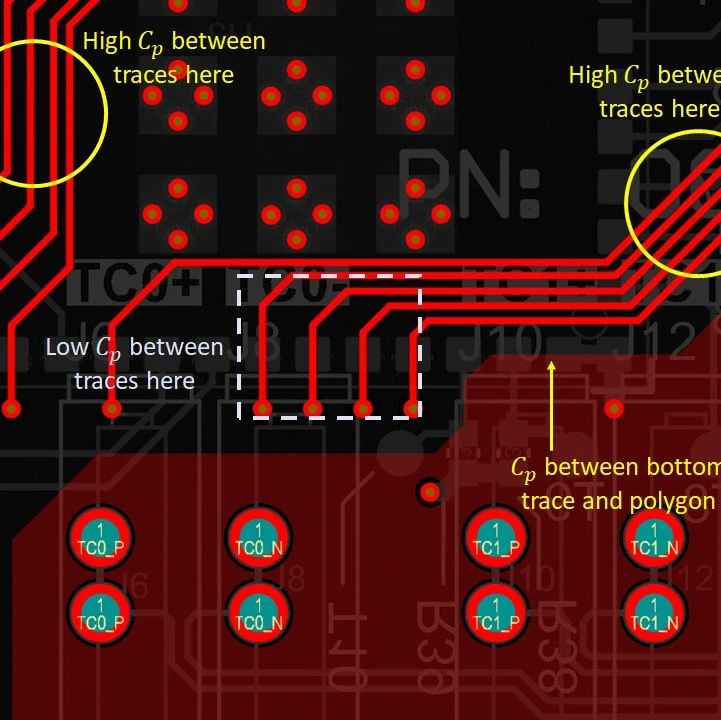

在多层PCB中,如果信号线从一个参考面跨越到另一个不同的区域(比如从GND层跨到空白层),信号回流路径断裂,EMI滋生,信号质量大幅下降。

尤其是高速信号线,一定要避免跨分割布线!

图6、图7 — 跨分割误区与正确示意

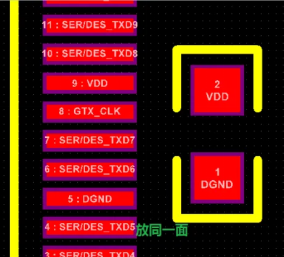

焊盘引线如果从对角出线,再加上阻焊偏差,会出现元件焊接旋转或偏移,影响焊接质量。

解决方法:

扇出走线保持沿长轴对称

若能保持短轴对称,能进一步防止偏移

图8、图9 — 焊盘出线引起旋转与修正方法

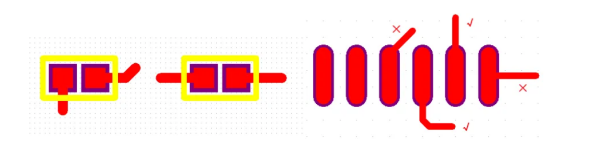

很多人误以为“差分线只要间距一样就行”,这是误区。真正影响信号同步的是线长!

差分线必须成对走线

匹配长度优先于一致间距

预留蛇形线用于调节长度

时钟、USB、LVDS等高频信号,若不做电磁隔离,会:

串扰邻线

引发EMI问题

包地(尽量三边围地)

若空间不足,至少保持3W间距

图12 — 高频信号包地与间距规范

多层PCB布线时,如果打孔过多或密集排列,会割裂GND/VCC参考面,导致:

信号回流路径延长

阻抗突变

噪声杂散

金手指长期插拔,阻焊层若未开窗会逐渐脱落,导致:

接触电阻升高

接触不良

在封装层加入开窗区域

PCB阻焊层绘制时注意完全开窗

图14 — 金手指正确开窗示意图

立碑现象=两端受力不均,主要由:

焊盘面积不对称

焊盘形状不一致

2025-06-25

2025-06-27

2025-06-19

扫码添加客服微信,备注“入群”拉您进凡亿教育官方专属技术微信群,与众位电子技术大神一起交流技术问题及心得~

分享 点赞 在看❤️ “三连”支持!