表8‑7MII接口介绍

简述 | Pins | 速率计算 | |

MII | 基本的100Mbps/10Mbps接口 | RXD[3:0]、TXD[3:0] TX_ER、TX_EN RX_ER、RX_DV TX_CLK、RX_CLK CRS、COL | Clock=25MHz or 2.5MHz 数据位宽4bit(一个时钟周期传输4bit数据) 100Mbps=25 MHz *4bit 10Mbps=2.5 MHz *4bit |

RMII | 在MII基础上精简的100Mbps/10Mbps接口; 通过提升Clock频率保持与MII一样的速率; | RXD[1:0]、TXD[1:0] TX_EN RX_ER CLK_REF CRS_DV | Clock=50MHz 数据位宽2bit(一个时钟周期传输2bit数据) 100Mbps=50 MHz *2bit 10Mbps是利用10个周期采样一次数据,相当于 10Mbps=50MHz/10*2bit |

SMII | 串行MII100Mbps/10Mbps接口; 进一步提升Clock频率保持与MII一样的速率; | RXD[1:0] TXD[1:0] TX_EN RX_ER CLK_REF CRS_DV | Clock=125MHz 数据位宽1bit(一个时钟周期传输1bit数据) 串行数据帧:一帧10bit(8bitdata+2bit control) 计算有效带宽时需要去掉控制位 100Mbps=125 MHz *(8bit/10bit) 10Mbps是利用10个周期采样一次数据,相当于 10Mbps=(125 MHz/10)*(8bit/10bit) |

GMII | 在MII接口基础上提升了数据位宽和Clock频率成为1000Mbps接口 | RXD[7:0]、TXD[7:0] TX_ER、TX_EN RX_ER、RX_DV GTX_CLK、RX_CLK CRS、COL | Clock=125MHz 数据位宽8bit(一个时钟周期传输8bit数据) 1000Mbps=125 MHz *8bit |

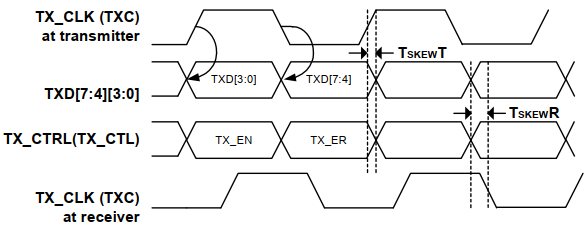

RGMII | GMII的简化版本 | RXD[3:0]、TXD[3:0] TX_EN RX_DV TX_CLK、RX_CLK CRS、COL | Clock=125MHz 数据位宽4bit(一个时钟周期里,上升沿取TX\RX的0-3bit,下降沿取TX\RX的4-7bit,所以实际还是在一个时钟周期里传输8bit数据) 100 0Mbps=125 MHz *8bit 100Mbps=25 MHz *8bit 10Mbps=2.5MHz *8bit |

SGMII | 串行GMII,在此基础上提升了时钟频率达到1000Mbps | RXD[0]、TXD[0] RX_CLK | Clock=125MHz 数据位宽1bit(一个时钟周期传输1bit数据) 串行数据帧:一帧10bit(8bit data+2bit control) 计算有效带宽时需要去掉控制位 1000Mbps=125 0MHz *(8bit/10bit) |

图8‑18RGMII发送端信号时序(来源88E1512datasheet,下同)

图8‑19RGMII发送端非延时模式(来源88E1512datasheet,下同)

图8‑20RGMII发送端延时模式(来源88E1512datasheet,下同)

图8‑21RGMII接收端信号时序

图8‑22RGMII接收端非延时模式(来源88E1512datasheet,下同)

图8‑23RGMII接收端延时模式(来源88E1512datasheet,下同)

代码8‑1IDDR 的原语

1.// IDDR : In order to incorporate this function into the design, 2.// Verilog : the following instance declaration needs to be placed 3.// instance : in the body of the design code. The instance name 4.// declaration : (IDDR_inst) and/or the port declarations within the 5.// code : parenthesis may be changed to properly reference and 6.// : connect this function to the design. Delete or comment 7.// : out inputs/outs that are not necessary. 8. 9.// <-----cut code="" below="" this="" line----=""> 10. 11. // IDDR: Input Double Data Rate Input Register with Set, Reset 12. // and Clock Enable. 13. // Artix-7 14. // Xilinx HDL Language Template, version 2018.3 15. 16. IDDR #( 17. .DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE" 18. // or "SAME_EDGE_PIPELINED" 19. .INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1 20. .INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1 21. .SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC" 22. ) IDDR_inst ( 23. .Q1(Q1), // 1-bit output for positive edge of clock 24. .Q2(Q2), // 1-bit output for negative edge of clock 25. .C(C), // 1-bit clock input 26. .CE(CE), // 1-bit clock enable input 27. .D(D), // 1-bit DDR data input 28. .R(R), // 1-bit reset 29. .S(S) // 1-bit set 30. ); 31. 32. // End of IDDR_inst instantiation 33. 34. |

图8‑24DDR_CLK_EDGE 3 种模式(来源UG741)

代码8‑2ODDR原语

1.// ODDR : In order to incorporate this function into the design, 2.// Verilog : the following instance declaration needs to be placed 3.// instance : in the body of the design code. The instance name 4.// declaration : (ODDR_inst) and/or the port declarations within the 5.// code : parenthesis may be changed to properly reference and 6.// : connect this function to the design. Delete or comment 7.// : out inputs/outs that are not necessary. 8. 9.// <-----cut code="" below="" this="" line----=""> 10. 11. // ODDR: Output Double Data Rate Output Register with Set, Reset 12. // and Clock Enable. 13. // Artix-7 14. // Xilinx HDL Language Template, version 2018.3 15. 16. ODDR #( 17. .DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE" 18. .INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1 19. .SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC" 20. ) ODDR_inst ( 21. .Q(Q), // 1-bit DDR output 22. .C(C), // 1-bit clock input 23. .CE(CE), // 1-bit clock enable input 24. .D1(D1), // 1-bit data input (positive edge) 25. .D2(D2), // 1-bit data input (negative edge) 26. .R(R), // 1-bit reset 27. .S(S) // 1-bit set 28. ); 29. 30. // End of ODDR_inst instantiation 31. 32. |

图8‑25DDR_CLK_EDGE两种模式

代码8‑3IDELAYE2 原语

1.// IDELAYE2 : In order to incorporate this function into the design, 2.// Verilog : the following instance declaration needs to be placed 3.// instance : in the body of the design code. The instance name 4.// declaration : (IDELAYE2_inst) and/or the port declarations within the 5.// code : parenthesis may be changed to properly reference and 6.// : connect this function to the design. All inputs 7.// : and outputs must be connected. 8. 9.// <-----cut code="" below="" this="" line----=""> 10. 11. // IDELAYE2: Input Fixed or Variable Delay Element 12. // Artix-7 13. // Xilinx HDL Language Template, version 2018.3 14. 15. (* IODELAY_GROUP = 16. 17. IDELAYE2 #( 18. .CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE) 19. .DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN) 20. .HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE") 21. .IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE 22. .IDELAY_VALUE(0), // Input delay tap setting (0-31) 23. .PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE 24. .REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0). 25. .SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal 26. ) 27. IDELAYE2_inst ( 28. .CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output 29. .DATAOUT(DATAOUT), // 1-bit output: Delayed data output 30. .C(C), // 1-bit input: Clock input 31. .CE(CE), // 1-bit input: Active high enable increment/decrement input 32. .CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input 33. .CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input 34. .DATAIN(DATAIN), // 1-bit input: Internal delay data input 35. .IDATAIN(IDATAIN), // 1-bit input: Data input from the I/O 36. .INC(INC), // 1-bit input: Increment / Decrement tap delay input 37. .LD(LD), // 1-bit input: Load IDELAY_VALUE input 38. .LDPIPEEN(LDPIPEEN), // 1-bit input: Enable PIPELINE register to load data input 39. .REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input 40. ); 41. 42. // End of IDELAYE2_inst instantiation 43. 44. |

1.// ODELAYE2 : In order to incorporate this function into the design, 2.// Verilog : the following instance declaration needs to be placed 3.// instance : in the body of the design code. The instance name 4.// declaration : (ODELAYE2_inst) and/or the port declarations within the 5.// code : parenthesis may be changed to properly reference and 6.// : connect this function to the design. All inputs 7.// : and outputs must be connected. 8. 9.// <-----cut code="" below="" this="" line----=""> 10. 11. // ODELAYE2: Output Fixed or Variable Delay Element 12. // Kintex-7 13. // Xilinx HDL Language Template, version 2018.3 14. 15. (* IODELAY_GROUP = 16. 17. ODELAYE2 #( 18. .CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE) 19. .DELAY_SRC("ODATAIN"), // Delay input (ODATAIN, CLKIN) 20. .HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE") 21. .ODELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE 22. .ODELAY_VALUE(0), // Output delay tap setting (0-31) 23. .PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE 24. .REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0). 25. .SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal 26. ) 27. ODELAYE2_inst ( 28. .CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output 29. .DATAOUT(DATAOUT), // 1-bit output: Delayed data/clock output 30. .C(C), // 1-bit input: Clock input 31. .CE(CE), // 1-bit input: Active high enable increment/decrement input 32. .CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input 33. .CLKIN(CLKIN), // 1-bit input: Clock delay input 34. .CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input 35. .INC(INC), // 1-bit input: Increment / Decrement tap delay input 36. .LD(LD), // 1-bit input: Loads ODELAY_VALUE tap delay in VARIABLE mode, in VAR_LOAD or 37. // VAR_LOAD_PIPE mode, loads the value of CNTVALUEIN 38. 39. .LDPIPEEN(LDPIPEEN), // 1-bit input: Enables the pipeline register to load data 40. .ODATAIN(ODATAIN), // 1-bit input: Output delay data input 41. .REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input 42. ); 43. 44. // End of ODELAYE2_inst instantiation 45. 46. |

代码8‑5IDELAYCTRL 原语

1.// IDELAYCTRL : In order to incorporate this function into the design, 2.// Verilog : the following instance declaration needs to be placed 3.// instance : in the body of the design code. The instance name 4.// declaration : (IDELAYCTRL_inst) and/or the port declarations within the 5.// code : parenthesis may be changed to properly reference and 6.// : connect this function to the design. All inputs 7.// : and outputs must be connected. 8. 9.// <-----cut code="" below="" this="" line----=""> 10. 11. // IDELAYCTRL: IDELAYE2/ODELAYE2 Tap Delay Value Control 12. // Artix-7 13. // Xilinx HDL Language Template, version 2018.3 14. 15. (* IODELAY_GROUP = 16. 17. IDELAYCTRL IDELAYCTRL_inst ( 18. .RDY(RDY), // 1-bit output: Ready output 19. .REFCLK(REFCLK), // 1-bit input: Reference clock input 20. .RST(RST) // 1-bit input: Active high reset input 21. ); 22. 23. // End of IDELAYCTRL_inst instantiation 24. 25. |

图8‑26DS182 中描述

8.5.1.3 RGMII发送接口设计

图8‑27RGMII 发送接口的设计方案

代码8‑6时序约束

1.settx_clk [get_clocks -include_generated_clocks -of [get_pins clk_wiz_0/inst/mmcm_adv_inst/CLKOUT1]] 2.create_generated_clock -name phy_tx_clk -source [get_pins clk_wiz_0/inst/mmcm_adv_inst/CLKOUT1] -multiply_by1 [get_ports phy1_rgmii_tx_clk] 3.set_output_delay -clock [get_clocksphy_tx_clk] -max -0.900 [get_ports {phy1_rgmii_tx_ctl phy1_rgmii_tx_data[*]}}] 4.set_output_delay -clock [get_clocksphy_tx_clk] -min -2.900 [get_ports {phy1_rgmii_tx_ctl {phy1_rgmii_tx_data[*]}}] 5.set_output_delay -clock [get_clocksphy_tx_clk] -max -0.900 [get_ports {phy1_rgmii_tx_ctl {phy1_rgmii_tx_data[*]}}] -clock_fall - 6.add_delay 7.set_output_delay -clock [get_clocksphy_tx_clk] -min -2.900 [get_ports {phy1_rgmii_tx_ctl {phy1_rgmii_tx_data[*]}}] -clock_fall -add_delay |

1.set_false_path -fall_from $tx_clk -rise_to [get_clocksphy_tx_clk] -setup 2.set_false_path -rise_from $tx_clk -fall_to [get_clocksphy_tx_clk] -setup 3.set_false_path -fall_from $tx_clk -fall_to [get_clocksphy_tx_clk] -hold 4.set_false_path -rise_from $tx_clk -rise_to [get_clocksphy_tx_clk] -hold |

1.set_multicycle_path 0 -setup -end -rise_from $tx_clk -rise_to [get_clocksphy_tx_clk] 2.set_multicycle_path 0 -setup -end -fall_from $tx_clk -fall_to [get_clocksphy_tx_clk] |

8.5.1.4 RGMII接收接口设计

图8‑30RGMII 接收接口的设计方案

1.create_clock -period 6.000 -name phy1_rx_clk [get_ports phy1_rgmii_rx_clk] 2.set_input_delay -clock [get_clocks phy1_rx_clk] -max 2.800 [get_ports {{phy1_rgmii_rx_data[*]} phy1_rgmii_rx_ctl}] 3.set_input_delay -clock [get_clocks phy1_rx_clk] -min 1.200 [get_ports {{phy1_rgmii_rx_data[*]} phy1_rgmii_rx_ctl}] 4.set_input_delay -clock [get_clocks phy1_rx_clk] -clock_fall -max -add_delay 2.800 [get_ports {{phy1_rgmii_rx_data[*]} phy1_rgmii_rx_ctl}] 5.set_input_delay -clock [get_clocks phy1_rx_clk] -clock_fall -min -add_delay 1.200 [get_ports {{phy1_rgmii_rx_data[*]} phy1_rgmii_rx_ctl}] |

1.set_property IODELAY_GROUP iodelay_grp_bank13 [get_cells {idelayctrl_inst1 rgmii_receive_module1/delay_rgmii_rx_ctl 2.{rgmii_receive_module1/RGMII_RX_DATA_BUS[*].delay_rgmii_rxd}}] 3.set_property IODELAY_GROUP iodelay_grp_bank13 [get_cells {rgmii_receive_module2/delay_rgmii_rx_ctl 4.{rgmii_receive_module2/RGMII_RX_DATA_BUS[*].delay_rgmii_rxd}}] 5.set_property IODELAY_GROUP iodelay_grp_bank14 [get_cells {idelayctrl_inst2 rgmii_receive_module3/delay_rgmii_rx_ctl 6.{rgmii_receive_module3/RGMII_RX_DATA_BUS[*].delay_rgmii_rxd}}] 7.set_property IODELAY_GROUP iodelay_grp_bank14 [get_cells {rgmii_receive_module4/delay_rgmii_rx_ctl 8.{rgmii_receive_module4/RGMII_RX_DATA_BUS[*].delay_rgmii_rxd}}] |