前不久我们撰文剖析了预计明年初上市、面向笔记本的Panther Lake处理器技术要点——而基于相同核心IP的至强处理器也更新了。虽说和代号Panther Lake的酷睿Ultra处理器一样,代号Clearwater Forest的至强6+处理器产品信息也没有公布——上市时间可能要等到明年下半年,产品大方向的宣传却已经开始了。

如Panther Lake处理器架构分析文章中提到的,基于chiplet的Clearwater Forest也在计算模块(compute tile)上采用最新的Intel 18A工艺,CPU核心IP则为Darkmont——也就是Panther Lake的E-core;

但有所不同的是,除了服务器CPU追求更大的吞吐量,有着更多核心(至多288个Darkmont核心)、内存通道、更大的缓存(最大576MB LLC),同时讲究高效计算与可信安全,在我们看来Clearwater Forest产品更有意义之处还在于它全面用上了Foveros Direct先进封装,也就是铜对铜的混合键合(hybrid bonding)3D堆叠方案。

如果Clearwater Forest能如期量产,这对Intel尤其Intel Foundry的意义无疑是重大的。

先看制造和封装:18A + 3D混合键合

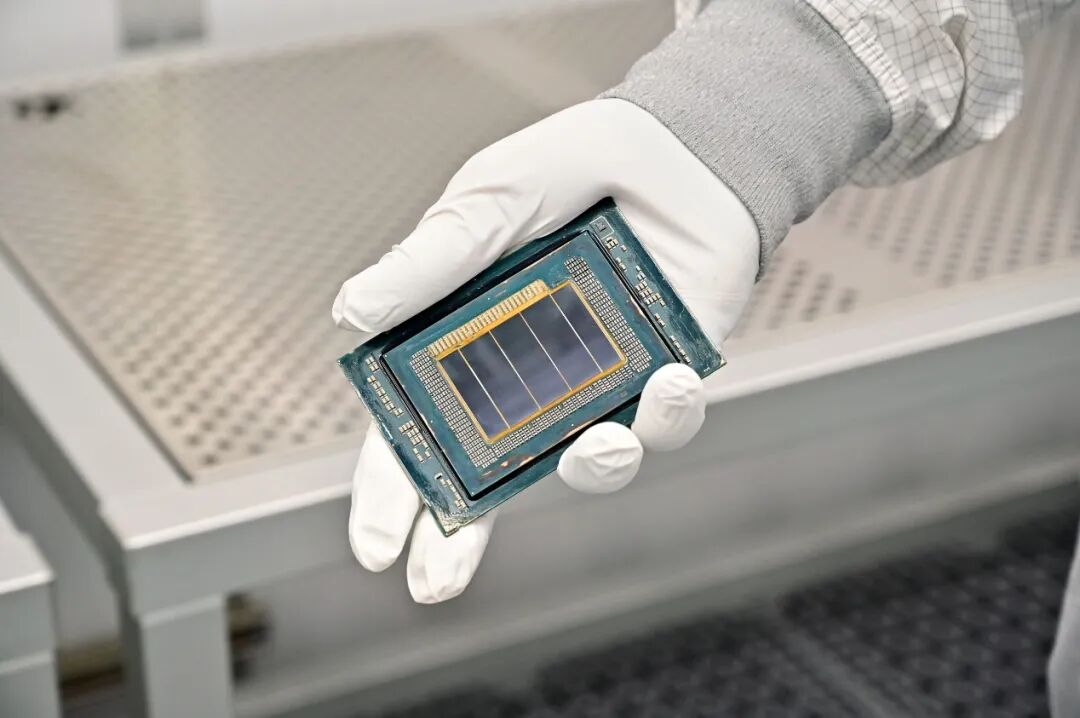

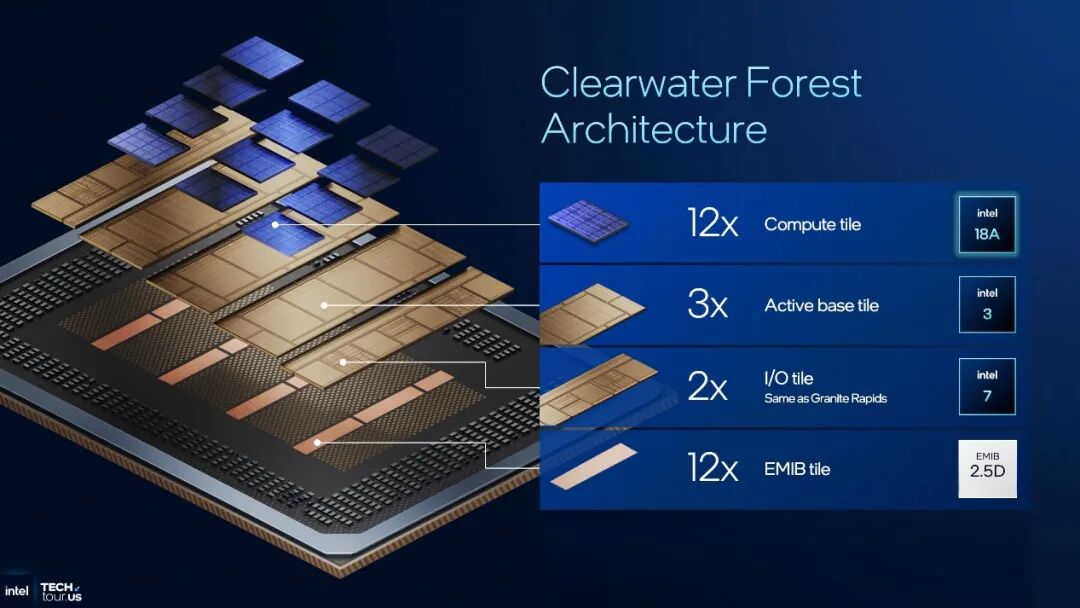

和Panther Lake篇一样,还是先看看Clearwater Forest芯片所用的制造和封装工艺。下面这张图展示了Clearwater Forest的封装级构成,最上层的蓝色部分是计算die(compute tile)——主要就是CPU核心,总共12片die、228个核心——这些die就采用Intel 18A工艺。

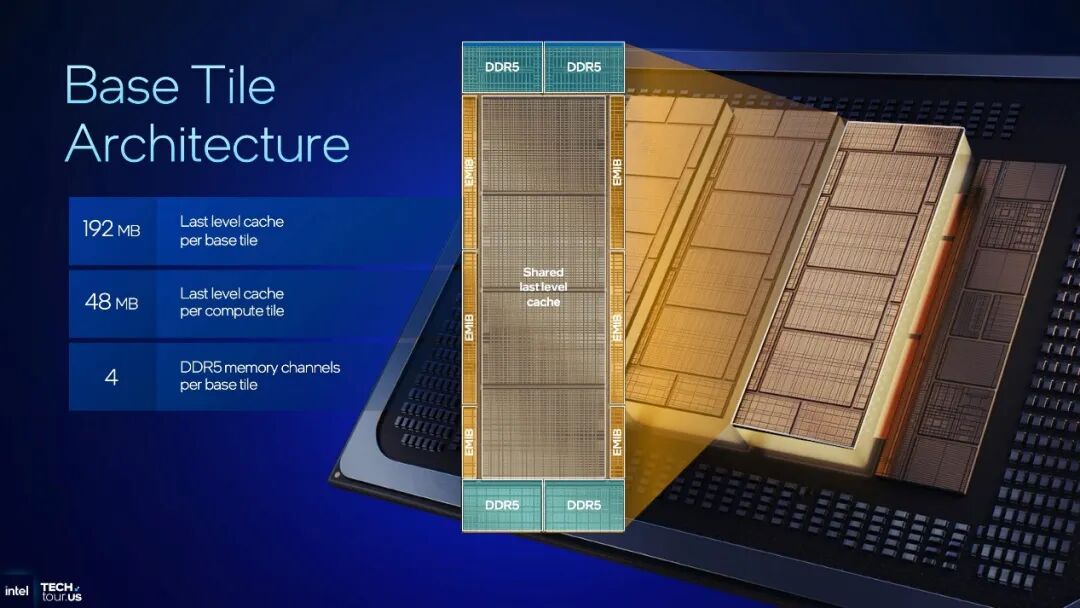

计算die堆叠在下层的3片有源base tile上——这部分可不是简单的2.5D封装中常见的silicon interposer硅中介,其中还带LLC(应该是L3 cache,有3D V-cache那味儿了...)、DDR5内存通道——所以用上了Intel 3工艺;上层的compute tile与下层的base tile就基于Foveros Direct 3D堆叠,也就是传说中的混合键合;

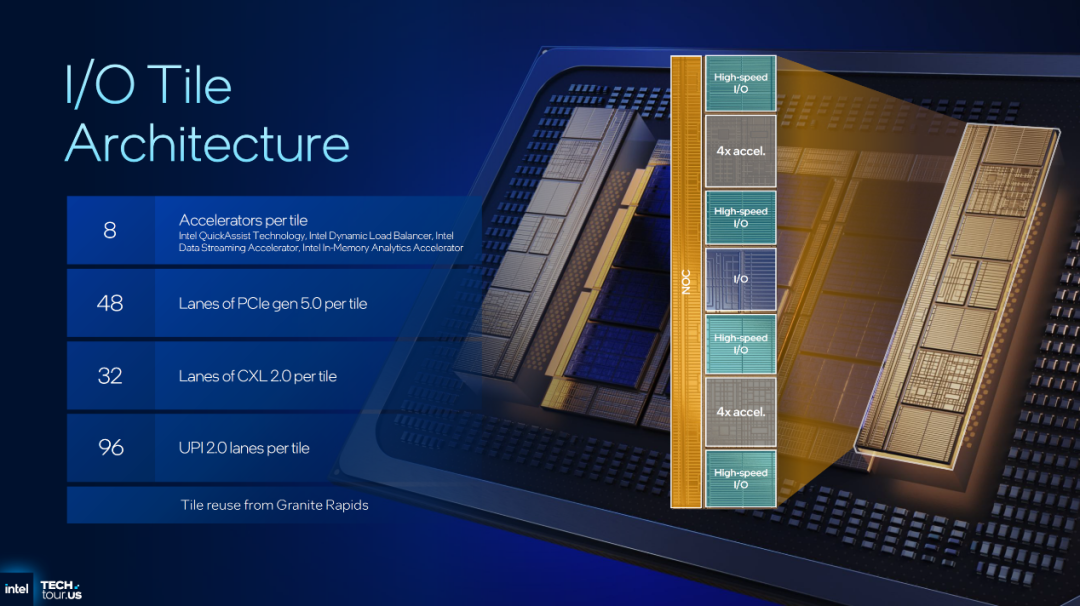

另外base tile的两侧还配有两片I/O tile,Intel特别标明了这部分和Granite Rapids(至强6的P-core版)保持一致,其中涵盖PCIe、加速器等组成部分,基于Intel 7工艺。

Base tile之间(以及I/O tile与base tile之间)再用EMIB硅桥方案做2.5D互联,所以总共还需要12片EMIB硅桥......就封装层级来看,至强6+虽然只是在至强6的名字之后加了个+号,但前者的复杂度应该说是上了强度的。如果把硅桥也算在内,则这样一片Clearwater Forest芯片,总共有29片die。

单纯从信号在不同die之间的流转来看,设想某个中间位置的CPU核心要走PCIe通道,则它首先需要垂直方向“走到”下方的die,然后经过EMIB硅桥抵达临近的base tile,再经过一次硅桥,才能访问到I/O tile。这里不是为了说明延迟或路径可能给性能造成影响,而是这样的芯片的确浓缩了当代几乎所有最尖端的半导体制造工艺。

Intel在宣传中强调的自然主要就是Intel 18A前道工艺和Foveros/EMIB后道工艺了。我们已经在Panther Lake技术解析文章里谈过这两部分,此前电子工程专辑也就这两项核心技术数度撰文,本文不再就此多谈。

对于Intel 18A工艺,重点一是RibbonFET器件结构,也就是GAAFET;一是PowerVia背面供电的应用。有关RibbonFET器件,除了尺寸缩减、更好的沟道电流控制、每瓦性能提升,还有面向设计客户时可通过nanosheet宽度与多阈值电压实现可调性。

PowerVia背面供电,则在将供电轨移往晶圆/die背面以后,达成了信号布线的优化、“优化宽间距导线层的布局”,实现了更高的单元密度,Intel的数据是“单元利用率超过90%”(提高10%);另外背面供电在中间部分用上了“纳米级”TSV“实现高效电源供电”,从封装到晶体管更短的供电路径,“降低约4-5%的功率损耗”。

不过需要指出的是,Intel在这波宣传中都没有提到本代产品相较上代的CPU单核峰值性能提升(包括Panther Lake vs Lunar Lake/Arrow Lake-H,以及Clearwater Forest vs Sierra Forest),而只是在提IPC提升或同功耗下的性能提升——对于Intel 18A工艺而言,这可不是个特别好的信号(或正待工艺良率爬坡)。

封装方面如前所述,compute tile和base tile之间采用Foveros Direct 3D堆叠,应该也是我们首次看到Intel混合键和工艺技术的大规模商用;相邻base tile之间、base tile与I/O tile之间,再用2.5D EMIB-M硅桥做互连。这种3D与2.5D封装方案的联用,也常被称为3.5D封装。

Intel这次也谈到了Foveros Direct 3D堆叠的部分关键参数,包括键和间距9μm(bump pitch)——和此前预告的≤10μm一致,也和此前AMD公开谈到3D V-Cache的3D SoIC键和间距大致相似——早期宣传的密度数据(wires/mm²)上,Intel似乎是略微占优的;

基于这次的base tile之上也是有存储与数字逻辑电路的,L3 cache在其中占据了大头;配套数据传输效率做到了~0.05pJ/bit——也和3D V-Cache达成的数字相似,每比特能耗约为常见2.5D封装方案的1/10(前些年Intel在Hot Chips上公布过Meteor Lake所用基于micro-bump的Foveros互连大约0.2-0.3pJ/bit的能耗效率)。

实际上Foveros Direct的采用,将更占空间的共享L3 cache放到了核心的下层,也让CPU有更大的空间去堆核,同时能放进更大的cache。从Intel在媒体会上的分享来看,compute tile上似乎的确只有CPU核心及配套的L1、L2 cache,不知道这么做对L3的延迟影响会有多大。

Tile与CPU核心架构:核心换代,LLC史诗级提升

再简单看一下每片die的内部构成:Intel未在国内媒体会上就这部分做详解,从外媒的资料可以看到compute tile、base tile和I/O tile之中具体都有些什么。

计算die也就是compute tile总共可切分成6个模块(module),每个模块之上有4个CPU核心;所以每片计算die分布着24个核心,那么12片计算die也就是总共288个核心;另外每个模块的共享L2 cache为4MB,那么L2 cache的总容量就是288MB。

如前文所述LLC也就是L3 cache位于下层的base tile之上——Foveros Direct 3D堆叠技术的采用,让Clearwater Forest有了显著大于上代的LLC容量。从Intel的PPT来看,每片base tile之上总共堆了192MB LLC,3片也就是576MB——于是这颗芯片的L2+L3 cache存储资源实际就达到了864MB,算是个史诗级提升。

这张PPT里头的48MB应该是指面向单片compute tile之时,直接共享的LLC大小。当然每片base tile之上还有4个DDR5内存控制器,使得整个封装的内存通道支持数为12通道。

I/O tile之上的组成部分则如上图所示:除了一些专用加速器(16个加速器,包括4xQuickAssist,4x动态负载均衡器,4x数据流加速器,4x存内分析加速器)之外,每片tile还包括有48通道的PCIe Gen 5,32通道CXL 2.0,96通道的UPI 2.0。两片I/O tile则将上述数字都x2。

另外,这里再稍微谈一谈Clearwater Forest所用的CPU核心Darkmont。关注上代至强6产品线的读者应该知道,Intel已经将至强切分成P-core、E-core两条产品线,满足不同目标市场需求。Clearwater Forest就是E-core能效核版,即Darkmont核心;而预计很快也将发布、与Clearwater Forest同代的P-core版应该是Diamond Rapids。

用Intel的话来说,很难借助同样的架构来满足不同客户的需求。E-core版至强处理器是在“满足一定性能要求前提下,最大化优化每核/每瓦的性能指标,更适用一些高核心密度以及需要快速进行横向工作负载扩展、吞吐量扩展的场景”。尤其“部分客户因为部署环境的原因,对极致性能要求没那么高,而要求在达到一定性能的同时更具性价比、更高能耗比的产品”。

虽然Darkmont核心已经在Panther Lake解析文章里谈过,毕竟Panther Lake的E-core同为Darkmont——但那更侧重Darkmont与Skymont(酷睿Ultra 200系列的E-core)的对比。

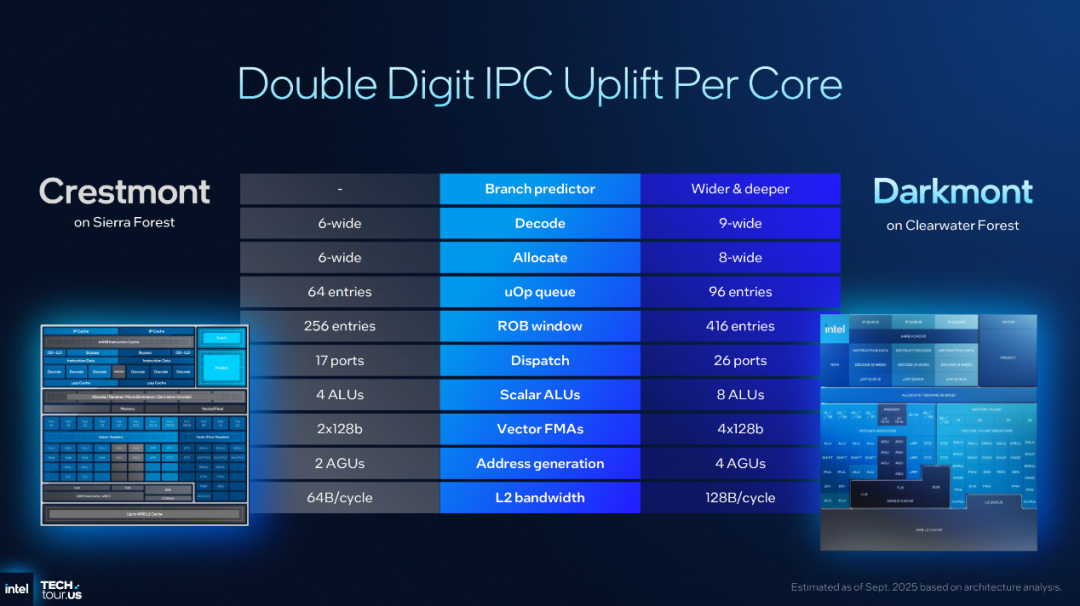

由于上代Sierra Forest处理器所用的核心是Crestmont,所以上面这张图是Intel总结的Darkmont相较Crestmont在核心微架构层面的主要改进——着眼于宽度和深度上的提升。虽说在Panther Lake技术解析文章里,我们说Darkmont可算是Skymont的改款,但它相较Crestmont的确是大幅度的微架构革新:

包括前端9-wide解码、nanocode引入实现了相较microcode更大程度的并行、μOp队列扩增、64KB I-cache、分支预测能力加强;乱序执行引擎部分,8-wide allocation和16-wide retire可带来的显著收益,416条目的OoO窗口大小、26执行端口,都给到了更充沛的资源;

执行引擎资源相关,标量引擎部分8个整数ALU、3个load和4个store AGU端口、3个jump端口、2个整数数据store端口(store data ports);矢量引擎部分则有4 vector/float ALU,2 vector/float数据store端口,4 vector/float stacks(4条执行管线都有其调度堆栈)——都是资源方面更大幅度的扩展;

存储子系统部分,前文已经提到每4核集群4MB L2 cache,带宽相较Crestmont也翻了一倍;L1本身与L1传输也更快与可预测等等…

所以Intel表示Darkmont带来了17%的IPC提升——当然这是相较Crestmont而言的。不过还是那句话,在不清楚Darkmont的频率以前,我们仍然不知道核心峰值性能的提升水平。

为什么是至强6+,而不是至强7?

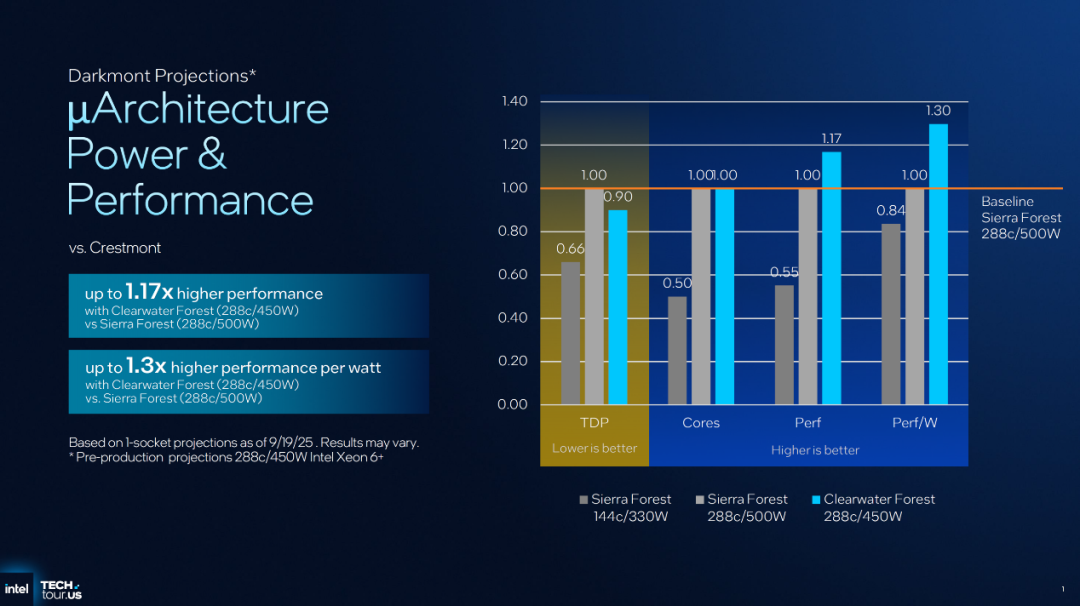

Intel倒是提供了Clearwater Forest相较Sierra Forest的性能改进,虽然这是个偏多线程吞吐性能的对比:相较至强6780E(144核/330W),288核预生产版的至强6+带来了90%的性能提升…

这似乎部分表明了Clearwater Forest之上的Darkmont单核峰值性能没有太大程度的提升,不知道是否Intel 18A可达成高频的限制亦或产品定位差异所致——这一点在最终酷睿Ultra与至强产品问世时就会有答案。

另外就能效层面,相较Crestmont,至强6+“在整体负载范围内带来高达23%的能效提升”——这应该是在不同负载占比的整个区间达成的平均成绩。注意看右图,这不是寻常意义上的能效曲线:横轴表示负载占比,纵轴则表示每瓦性能。

这里更重要的应该是所谓“8:1服务器整合”,具体是指只需要基于Clearwater Forest处理器的20个机架180台服务器,就能达到第二代至强处理器(Cascade Lake)70个机架1400台服务器的性能水平(基于SPECInt Rate 17):整机空间占用因此减少71%,功耗降低750kW,能耗比提升3.5倍,每个机架的虚拟机部署数量提升2.3倍。这个对比强调的是至强服务器客户换代,所能达成机架密度大幅提升、TCO的大幅降低。

值得一提的是,从外媒报道来看,Intel还给了一组性能对比数据:相比288核/500W的Sierra Forest,Clearwater Forest以更低的TDP功耗(450W)达成至多1.17x性能提升,每瓦性能提升幅度1.3倍。如下图所示:

就企业客户角度来看,Clearwater Forest显然不是对Sierra Forest的换代——毕竟服务器CPU产品对数据中心客户而言并不是一年一换的。Intel在媒体会上也说 “至强6+通过大幅增加CPU核心数量适用于吞吐型应用”——比如5G核心网、web服务请求等;还说至强6适合“有更高turbo需要”的场景;同时确认了至强6+与至强6会在市场上并行、“同时存在”。

这可能也是Clearwater Forest产品名为“至强6+”而非“至强7”的原因。不过更重要的是,由于288核Clearwater Forest同样基于Birch Stream AP平台(LGA7529大插槽),则原本使用Granite Rapids-AP、Sierra Forest-AP处理器的客户是可以平滑替换Clearwater Forest-AP的,是“在同一个平台上做了三组不同的产品”(暗示Diamond Rapids是不同平台?)…

最后更具体地看看Clearwater Forest处理器的规格。Clearwater Forest的主要规格信息浓缩如下图:

其中亮点除了Intel 18A工艺和Foveros Direct及EMIB封装工艺的采用,还包括总共288个Darkmont核心(Sierra Forest实则还在用Crestmont),内存速率提升到了8000 MT/s(Sierra Forest为6400 MT/s),还有借助3D堆叠达成了576MB LLC——相比Sierra Forest是史诗级提升,和相较竞争对手的部分短板补足(虽然还是不及Epyc的堆料)。

另外Intel还强调了至强6+针对高效计算,配套引入了Intel AET(应用能耗监测);且在“可信&安全”方面,包括可信计算、Intel软件防护扩展(SGX)和可信域扩展(TDX),同时针对SHA-512、SM3和SM4等加密算法也有硬件加速。

其他包括总共96条PCIe Gen 5通道(x16, x8, x4, x2)、64条CXL 2.0通道等已经在前文注解;兼容上代至强6900P,单双路系统的TDP热设计功耗范围300-500W。

虽然还没有产品层面的信息,但Clearwater Forest至强6+处理器预计会在明年下半年上市:Foveros Direct及Intel 18A工艺的全面结合对Intel而言是意义重大的,即便后者会率先在Panther Lake之上看到。这些新技术的引入,也让我们格外期待在这个特殊时期Intel给PC和数据中心市场同时交出的新答卷。