【内容目录】

二、Chiplet与3D封装成高增长赛道

三、路径一(垂直):3D堆叠的极限演进(从 TSV 到 混合键合)

四、路径二(平面):Chiplet异构集成的生态重构(从CoWoS到UCIe)

五、国内格局:算力(HPC)与存储封装的双线竞逐

六、发展方向:从玻璃基板(TGV)到光电共封装(CPO)

七、结语:封装即算力

本文涉及企业

一、先进封装演进路径

存储行业正迎来二十年未有的“超级周期”。以江波龙为代表的模组厂市值破千亿,背后是AI算力需求与原厂(三星、SK海力士、美光)产能策略调整共振的结果。

*凭借AI内存(技术的)里程碑式进展,SK海力士股价涨至历史新高

正如近期(2025年10月15-17日)在深圳举办的“湾芯展先进封装系列论坛”所凝聚的产业共识:先进封装已不是附属工序,而是定义系统性能的核心。

未来十年,“3D垂直堆叠”与“Chiplet异构集成”是这条“黄金赛道”上最清晰的两条演进路径,它们正从根本上重塑HPC(高性能计算)与存储两大产业。

二、Chiplet与3D封装成高增长赛道

大模型对算力的需求指数级攀升,但2D单片SoC微缩已遭遇“成本”、“功耗”和“物理极限”三堵高墙。后摩尔时代延续算力增长,只剩下两条路:

* Arm Neoverse CMN-600 and a 2×2 mesh implemented in 3D.

1.3D垂直堆叠 (Vertical Stacking): 当平面面积不够,就向“天空”要空间。通过晶圆堆叠,实现超高密度和超短互连,主要解决带宽瓶颈。

2.Chiplet异构集成 (Heterogeneous Integration): 当单颗大芯片良率太低、成本太高,就“化整为零”。将大芯片拆分为多个“芯粒”(Chiplet),再通过2.5D等技术“水平”拼装,主要解决成本、灵活性和上市周期。

这两大路径,正分别(且共同)主导着全球HPC算力与存储产业的未来。

三、路径一(垂直):3D堆叠的极限演进(从 TSV 到 混合键合)

3D垂直堆叠”是当平面面积耗尽时,向“天空”要密度和带宽的革命。

·TSV + 微凸点:3D堆叠的实现 HBM的第一次革命由**TSV(硅穿孔)开启。TSV技术在DRAM Die之间垂直打孔,首次实现了真正的3D堆叠,再依靠Micro-bump(微凸点)**进行电气连接。这一“TSV + 微凸点”的经典架构,支撑了从HBM1到HBM3E的带宽飞跃(>1.2 TB/s),是当前3D封装的主流。

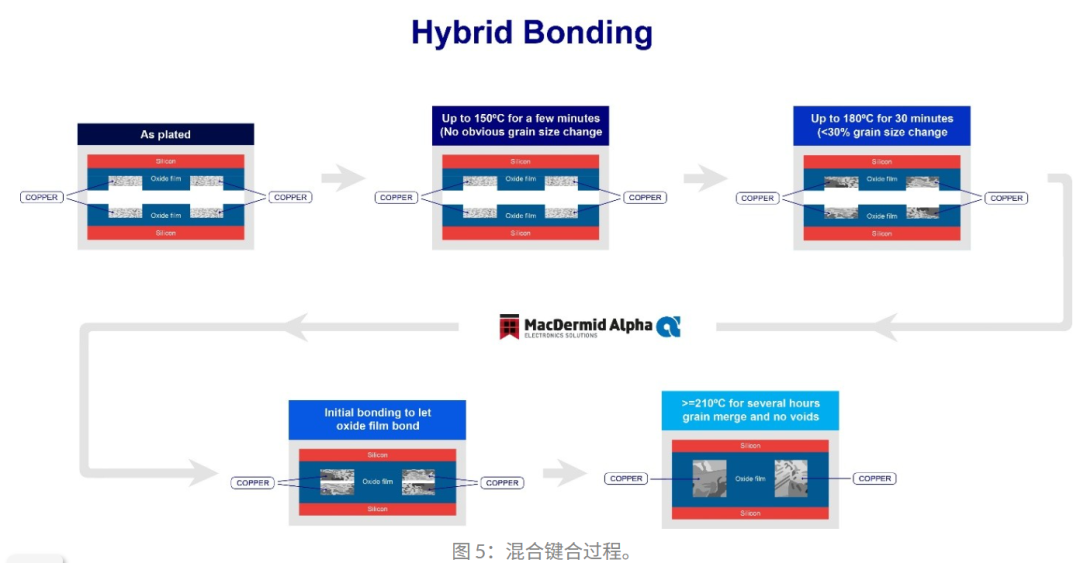

·混合键合:混合键合 (Hybrid Bonding) HBM3E已达极限。HBM4要求2048-bit位宽,I/O数翻倍,传统的Micro-bump(间距~40µm)在密度、信号和散热上均已触顶。 混合键合 (Cu-Cu Bonding) 成为必然选择。它是一种“无凸点”的铜-铜直连技术,互连间距可降至10µm以下,I/O密度提升10倍以上。

·低温键合:低温键合工艺 3D垂直堆叠的最大挑战之一是热应力。正如先进封装设备巨头EV Group (EVG) 的技术路径所示,实现异构材料(如DRAM与逻辑芯片)堆叠的关键,在于低温键合。EVG通过其等离子体激活(Plasma Activation)等核心技术,使得高强度的熔融键合(Fusion Bonding)和混合键合能在室温或低温(~200°C)下实现,这彻底解决了不同材料因热膨胀系数不同而导致的损伤,是HBM4及未来“算存一体”3D堆叠的基石。

四、路径二(平面):Chiplet异构集成的生态重构(从CoWoS到UCIe)

如果说3D堆叠是“向高走”,Chiplet就是“化整为零,再水平拼装”。

·Chiplet:HPC算力的“成本”与“灵活”革命 NVIDIA H100、AMD MI300这类巨型AI芯片,已逼近光刻掩膜版图的极限,成本和良率堪忧。Chiplet理念将大芯片“拆分”为多个独立的小芯粒(可采用不同工艺节点),再通过先进封装“拼装”成一个系统。

·核心技术:2.5D集成(CoWoS / EMIB) 当前主流的Chiplet集成方式是2.5D封装。它通过一块硅中介层(Silicon Interposer)(如台积电的CoWoS)或高密度RDL(重布线层),在“水平”方向实现芯粒间的高密度互连。当今所有的AI加速器(GPU/TPU),其本质都是“2.5D Chiplet异构集成”—— 即将“算力Chiplet”与“HBM(3D堆叠的存储Chiplet)”水平拼装在一起。

·产业共识: 正如Prismark顾问王郑天野在深圳论坛上指出的,AI加速器已是封装市场最核心的驱动力。而Chiplet架构正是满足AI算力需求的最优解。随着UCIe等开放互连标准的成熟,一个可互联互通的“芯粒”生态正加速形成。

五、国内格局:算力(HPC)与存储封装的双线竞逐

面对国际巨头的技术演进,本土产业链正沿着这两条路径“以封测补制造”,加速追赶。

1.HPC算力封装:

·现状: 以昇腾(Ascend)AI芯片为代表,已率先采用先进的Chiplet集成方案(如CoWoS-like)。同时,寒武纪等HPC芯片设计公司,正与本土OSAT(如长电科技、通富微电、华天科技)紧密合作。

·路径: 本土OSAT厂正全力突破。例如,长电科技的XDFOI(一种高密度扇出型封装,无需硅中介层,成本更低)和通富微电(AMD核心封测厂)的2.5D能力,都在为国产HPC芯片提供Chiplet集成的关键“底座”。

2.存储封装:

·现状: 本土在HBM领域刚起步,但在“容量型”存储封装上已形成独特且强大的生态,即SiP (系统级封装)。

·SiP技术解构: 这绝非简单的PCB组装。以江波龙、佰维为代表的模组厂,其SiP能力是将多颗超薄减薄的NAND Die垂直堆叠,再与一颗主控Die,共同封装在同一块BGA基板上。这是一种高密度的“3D(NAND堆叠)+ 2D(Die并排)”的异构集成,是UFS、eMMC等嵌入式存储的核心壁垒。

·特色生态: 本土形成了“颗粒厂(长存/长鑫) + 公共封测平台(沛顿科技) + 模组厂(江波龙/佰维/德明利)”的高效协同生态。沛顿已非“美光专属”,它转型为开放的第三方封测平台,承接颗粒厂和模组厂的Wafer Test和SiP封装代工,极大赋能了整个本土存储产业。

六、发展方向:从玻璃基板(TGV)到光电共封装(CPO)

3D垂直堆叠与Chiplet异构集成并非割裂,它们的未来必将走向融合。

·演进一:3D异构集成(“算存一体”) 未来的终极形态之一,是将计算Die(如CPU/GPU)与存储Die(如DRAM)通过晶圆级混合键合(W2W Hybrid Bonding)直接垂直堆叠(如AMD的3D V-Cache)。这是“算存一体”的极致,将彻底消除延迟。

·演进二:玻璃基板(TGV)的应用 随着Chiplet封装体尺寸越来越大(超过100mm x 100mm),传统有机基板的翘曲问题(Warpage)已成良率杀手。正如深圳先进封装论坛上,矩阵多元、三叠纪等企业所展示的,玻璃通孔(TGV)技术正成为关键。玻璃基板更平坦、热稳定性更好,是承载未来超大尺寸Chiplet集成的必然选择。

*图源:云天半导体

·演进三:光电共封装(CPO) 当AI集群的I/O带宽需求突破Tbit/s,铜线(电互连)的损耗已无法承受。光电共封装(CPO)将成为必然。它将交换芯片(Switch)与硅光子芯片(SiPh)“共封装”在一起,实现“光进光出”,彻底解决带宽墙。

七、结语:封装即算力

无论是先进封装的3D垂直堆叠,还是AI GPU的Chiplet异构集成,亦或是国内存储的SiP封装,这些技术趋势都清晰地表明:半导体产业的价值重心正发生结构性转移,封装已成为决定系统性能上限的核心环节。 谁掌握了最顶尖的封装集成能力,谁就掌握了后摩尔时代的“价值锚点”。

*参考文献

[1] Yole Développement. "3D Packaging & Hybrid Bonding: Market and Technology Trends." Yole Group Report, 2025.

[2] Prismark Partners LLC 王郑天野. "Semiconductor Packaging Market and AI Demand." 2025.10.16.

[3] SK Hynix. "SK Hynix Unveils HBM4 Development Plan with Hybrid Bonding." SK Hynix News, 2024.

[4] EV Group. "Low-Temperature Fusion and Hybrid Bonding for Heterogeneous Integration." EVG Technical Publication, 2024.

[5] 江波龙. "Longsys System-in-Package (SiP) Technology for Embedded Storage." Longsys Technical Brief.

[6] CXL Consortium. "Compute Express Link (CXL) 3.0 Specification and its Impact on Memory Subsystems." CXL Consortium Brief, 2023.

[7] AMD. "AMD 3D V-Cache™ Technology." AMD Technology Brief, 2023.

[8] 长电科技. "XDFOI™: An Ultra-High-Density Fan-Out Solution for Heterogeneous Integration." JCET Technical Publication, 2024.

[9] 矩阵多元科技 扶庆. " PLP & TGV种子层金属化解决方案." 2025.10.16.

[10] SiemensEDA (王志宏). "重塑运算未来:Chiplet 与 3D IC 引领的先进封装创新。",2025.10.16.