UCIe协议诞生背景

过去几十年,摩尔定律一直是半导体行业发展的核心驱动力,芯片上晶体管数量每18-24个月翻倍,性能随之大幅提升。但近年来这一定律明显放缓,芯片制程向7nm、5nm甚至3nm推进时,技术难度呈指数级增长,研发成本飙升,且物理极限日益逼近,传统通过提升制程提高性能的路径愈发艰难。

为应对这一困境,Chiplet技术应运而生。它将大型芯片分解为多个小型芯粒,各芯粒可按功能需求采用最适配的工艺制造,既能提高良率、降低流片成本,又能增强设计灵活性。不过在发展初期,由于缺乏统一互连标准,不同厂商的芯粒无法兼容互通,每次设计都需重新开发互连方案,严重制约了Chiplet技术的规模化应用。

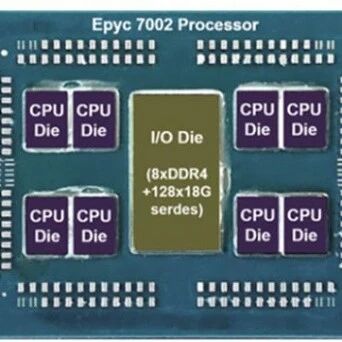

正是在这一背景下,UCIe(通用芯粒高速互连标准)协议应运而生。其核心目标是建立开放的Die-to-Die互连标准,打破厂商间的技术壁垒,实现不同功能芯粒的灵活组合。2022年3月,英特尔、AMD、ARM、台积电等十家行业巨头联合推出UCIe并成立联盟,这一举措为Chiplet技术提供了标准化支撑,解决了互联互通的关键难题,正式开启了Chiplet技术标准化发展的新阶段,也为半导体行业突破摩尔定律限制提供了新路径。

UCIe协议原理

分层协议架构

UCIe协议是一种分层协议,主要分为PHY 层、Adapter层和Protocol层,各层之间通过标准接口连接,PHY层和Adapter层之间接口为RDI(Raw Die - to - Die Interface),Adapter层和Protocol层之间接口为FDI(Flit-Aware Die-to-Die Interface)。这种分层架构使得各层功能明确,各司其职,便于协议的通用和复用。

UCIe接口架构示意图

·PHY层:负责物理信号的传输,包括电气物理层和逻辑物理层。电气物理层方面,UCIe支持Standard及Advanced Package两种封装形式,支持低功耗模式,单Lane支持的传输速率有4,8,12,16,24,32 GT/s。逻辑物理层主要负责UCIe链路的初始化及链路训练,将Adapter发来的数据分发到各条Lane上、进行Lane序重排、坏Lane修复及时钟校正等工作。例如,数据包以Byte形式发出,一个Byte占用一个Lane使用4个clk传输,Main_band采用DDR的双沿采样。UCIe单个Adapter可对接1、2或4个物理层Module。配置为2个Module的示意图如图所示。

Two module configuration for standard package

(图源:【UCIe】初识 UCIe-CSDN博客)

·Adapter层:主要功能包括CRC(循环冗余校验)、FEC(前向纠错)、Retry(重传)等,以确保数据可靠传输。当协议层发送64B Flit数据时,会在前加上2B hdr(Protocol ID, Stack ID)和后面加上2B CRC值;对于 256B Flit需要额外增加2B CRC。此外,它还通过Sideband消息跟对端的UCIe设备进行协商,确定采用的协议及一些参数,并且支持多个协议层架在统一Adapter上,通过Adapter中的Arb/Mux实现多个协议层的分时复用。

UCIe 与Adapter的连接

(图源:【UCIe】初识 UCIe-CSDN博客)

·Protocol层:支持PCIe 6.0、CXL 2.0/3.0协议,同时还支持Streaming Protocol(用于映射自定义传输协议),允许用户根据自身需求定制协议。在传输模式上,分为Raw Mode和Flit Mode。PCIE6.0、CXL2.0/3.0都支持 Raw Mode,在该模式下,所有64B或者 256B数据都由协议层来负责填充,绕过适配层,CRC、FEC和Retry都由协议层处理;而在Flit Mode下,适配层要对协议层数据添加2B hdr和2B CRC,并在协商过程中,通过FDI接口把这些信息作为Link Trainning的一部分传给协议层。

UCIe Protocol层对应接口运行机制

数据传输机制

UCIe提供了Mainband及Sideband两大数据通路。

·Mainband:主要用来传输业务数据流,采用 DDR双沿采样方式。例如,对于标准封装 x16,8个UI传输1个Byte,若有16Lane,传输256B数据需要128UI。不同条件下单Lane 支持多种传输速率,可满足不同应用场景对带宽的需求。

·Sideband:主要用来处理链路训练、链路管理、参数交换及寄存器访问等非数据传输业务,作为Mainband的Back Channel。它能够简化UCIe中的链路训练、链路管理和D2D参数交换过程,提升Mainband的带宽利用率并简化其设计复杂度。UCIe Sideband支持配置读写(CfgRd/Wr)、内存读写(MRd/Wr)、完成(Cpl/Cpld)及消息(Msg/MsgD)4种不同的数据包,通过这些数据包实现寄存器访问、Message传递等功能,在D2D参数交换、链路训练、链路管理及寄存器访问等方面发挥着不可或缺的作用。

链路训练

UCIe采用分层的链路状态机(LSM),包括 FDI FSM、RDI FSM 和 PHY LSM,来进行链路训练。链路训练是UCIe中非常重要的环节,通过链路训练,UCIe设备能够建立起稳定可靠的数据传输链路,确定链路的各项参数,如传输速率、编码方式等,确保数据在不同的UCIe设备之间能够准确无误地传输。在链路训练过程中,各层状态机协同工作,通过一系列的信号交互和参数协商,完成链路的初始化和配置,为后续的数据传输做好准备。

UCIe与Chiplet发展的紧密联系

为Chiplet提供标准化互连

在UCIe协议出现之前,Chiplet之间的互连缺乏统一标准,导致不同厂商的Chiplet难以实现互联互通,极大地限制了Chiplet技术的应用范围。UCIe协议的诞生填补了这一空白,它定义了一套通用的、开放的Die-to-Die互连标准,包括支持的封装类型(带有标准凸点的标准封装和带有微凸点的各种高级封装)、物理层和协议层规范、软件堆栈模型等,使得不同厂商生产的Chiplet能够按照统一标准进行连接和通信,实现了Chiplet在芯片封装内的即插即用,为Chiplet技术的大规模推广和应用奠定了坚实基础。

UCIe协议凭借自身优异特性,成为助力 Chiplet技术发挥优势的关键。它具备高速、低延迟、低功耗、高带宽密度等特点,且拥有极低的误码率,低速时BER<1e-27,高速时BER<1e-15。这些特性为Chiplet之间的数据传输提供了坚实保障,让不同功能的Chiplet 能在稳定高效的环境中协同工作。以数据中心的高性能计算芯片为例,通过UCIe连接多个Chiplet后,能显著提升计算性能,同时降低功耗,很好地满足了数据中心对算力和能效的高要求。

与此同时,UCIe联盟的成立以及协议的不断更新完善,吸引了众多行业巨头参与其中。这推动了Chiplet产业生态在设计、制造、封装等各个环节的完善。像英伟达等芯片厂商已采用相关设计方案,将Chiplet技术与UCIe协议结合应用到产品中。

该协议获得了英特尔、AMD、台积电等巨头的支持,技术标准也在持续演进。从2022年的1.0版本到2024年的2.0版本,不断优化提升。目前已有基于该协议的Chiplet产品面市,其在性能、成本等方面的良好表现,验证了UCIe协议的可行性。可以说,UCIe为Chiplet技术的发展提供了有力支撑,未来有望推动半导体行业迈向新高度。

使用SIDesigner进行仿真

以UCIe为典型代表的Chiplet互连技术,面临多重物理层挑战:其单通道最高传输速率达32Gbps的高速特性、单位面积内密集的信号网络布局,以及对误码率(如部分场景需低至 1e-27)的严苛要求,共同构成了设计难点。

当采用先进封装技术实现多芯片模块高效互连时,信号完整性问题会显著凸显 —— 具体包括信号传输中的串扰与损耗、时序偏移(Skew)、寄生参数干扰、电源完整性恶化、热 - 电耦合效应,以及如何满足极端严苛的误码率标准等。

这也使得Chiplet的高速信号完整性仿真成为技术难题。此类仿真需融合SerDes与DDR总线的双重仿真特性:既要应对高速率、高误码率要求,处理多信号线并行传输场景;又要适配单端信号传输模式,依赖单端IBIS-AMI模型进行仿真,并需完成电压传输函数(VTF)等专项仿真验证。而通过IBIS-AMI模型以及S参数模型可以简化这一复杂的过程,同时保证仿真的高精度和高准确性。

使用巨霖仿真软件SIDesigner搭建UCIe信号完整性的仿真电路,原理图如下:

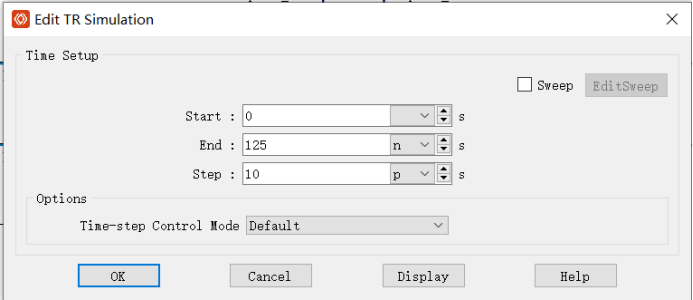

使用瞬态仿真进行眼图的测量,仿真设置如下:

信号传输速率为16Gbps,使用NRZ调制方式。模式选择瞬态仿真,约1500个UI叠加眼图。

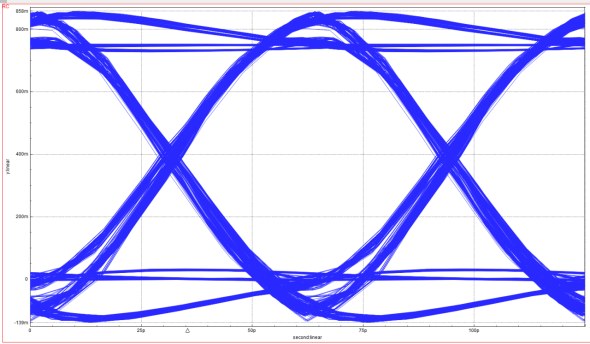

仿真眼图结果如下:

工程师可以依据眼图直观反映信号是否满足高速传输的物理条件(如速率、误码率),还能定位损耗、抖动、串扰等具体问题,为设计优化提供精准依据。对于UCIe这类高带宽、高密度、高可靠性要求的Chiplet互连技术,眼图分析是验证设计可行性、保障最终性能的核心环节。

点击下方“阅读原文”即可访问巨霖科技官网(www.julin-tech.com)申请试用软件,如有任何疑问可随时联系support技术人员,我们期待与您交流!

文章中部分图片来自网络,如有侵权,请联系删除。