2025年10月11日,以“设计封装协同,共筑芯未来”为主题的第三届集成芯片和芯粒大会在武汉盛大开幕。北极雄芯携自主研发的货架芯粒解决方案精彩亮相,向近千名行业专家、企业代表展示了以HUB+X开放架构为核心的芯粒技术突破,为高端芯片降本增效、灵活适配下游需求提供了全新路径,引发产业界广泛关注。

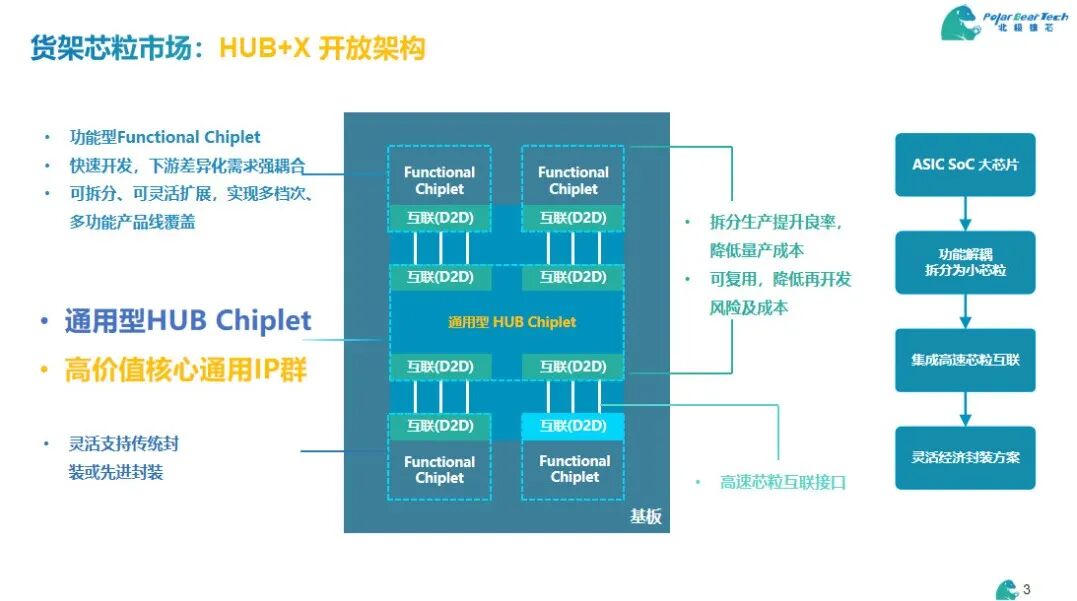

本次大会上,北极雄芯重点推介了“功能解耦、灵活集成”的货架芯粒方案——通过通用型HUB Chiplet与功能型Functional Chiplet的组合,打破传统ASIC SoC大芯片研发周期长、成本高、风险大的痛点。其中,通用型HUB Chiplet搭载12核ARM Cortex A72 CPU,支持PCIe 5.0 8lane、78GB/s DDR带宽及256GB/s D2D高速互联,集成视频/图像处理等核心通用IP,可直接复用至多类产品;功能型Chiplet则覆盖GPU、NPU两大核心品类,GPU芯粒具备1.3TFLOPS@FP32算力与32GPix/s像素填充率,NPU芯粒INT8精度算力达50TOPS,且支持INT4/8/16及FP16多精度运算,能深度匹配AI计算、图形渲染等差异化场景需求。

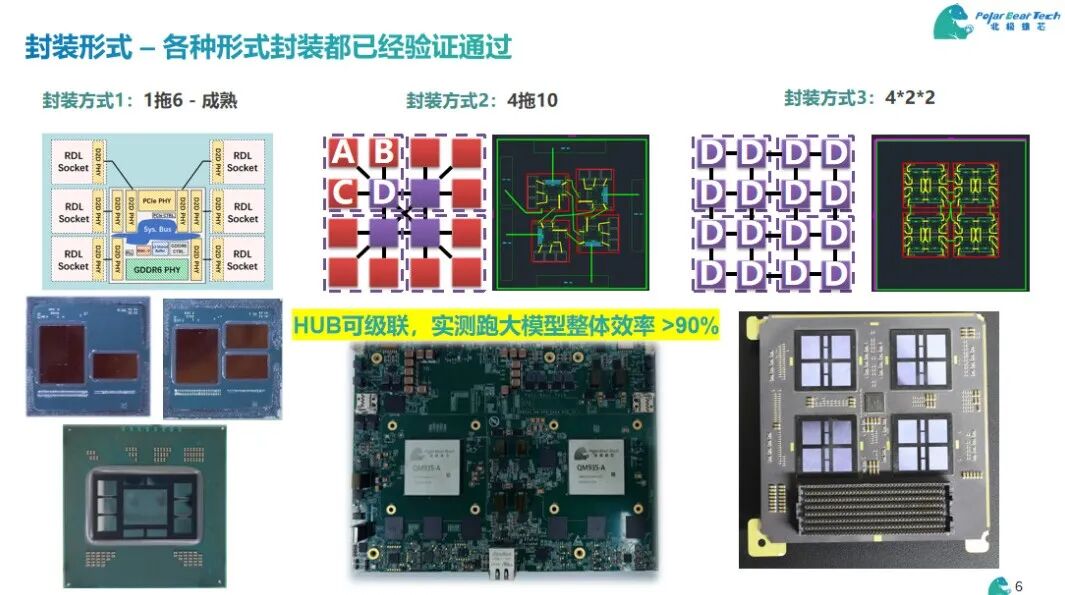

为解决芯粒互联与封装难题,北极雄芯自主研发的PB-Link车规级芯粒接口成为一大亮点。该接口遵循国内ACC1.0标准,支持8通道×32Gbps传输带宽,误码率<10-15,可适配2D/2.5D封装及不同工艺制程互联,且已通过-40℃~125℃全温度范围测试与ASIL-D认证,搭配全国产化封装、基板、测试供应链,为芯粒稳定应用提供坚实保障。同时,公司展示的多类封装方案均已验证成熟,包括1拖6、4拖10、4×2×2等形式,HUB芯粒可灵活级联,实测跑大模型整体效率超90%,满足不同算力规模需求。

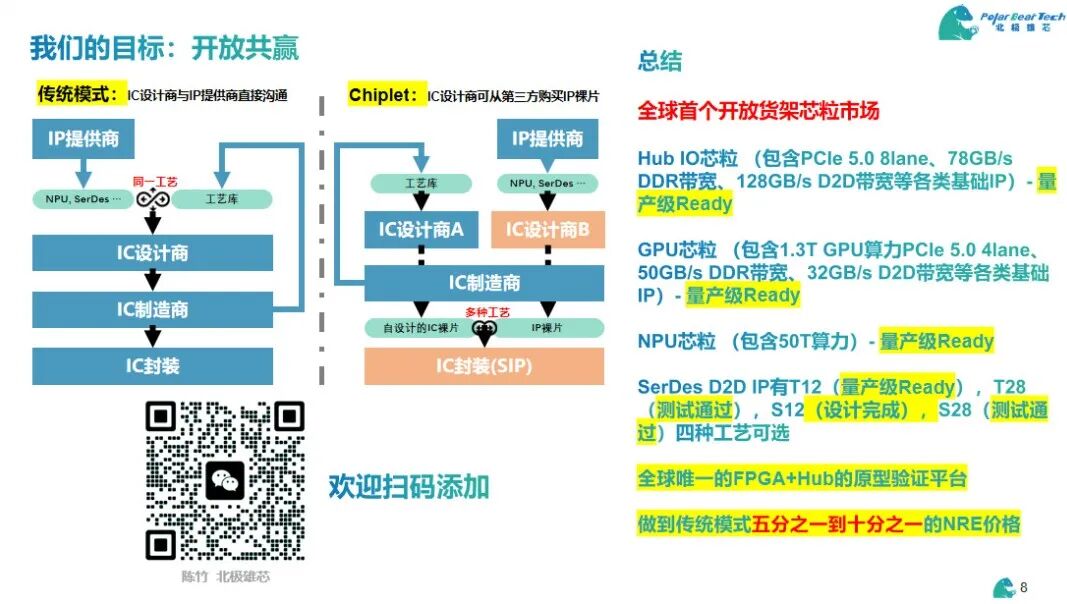

值得关注的是,北极雄芯还在大会上预告了全球唯一的HUB+FPGA原型验证平台,该平台集成12核ARM Cortex A72处理器、80TOPS高性能可重构协加速器及丰富外设接口,预计12月正式推出,将为客户提供从方案验证到量产落地的全流程支持。更关键的是,依托货架芯粒的复用性与模块化设计,北极雄芯可将传统芯片研发的NRE费用降至五分之一到十分之一,大幅缩短产品上市周期,降低企业创新门槛。

当前,全球集成电路产业正从“尺寸微缩”向“异构集成”战略转型,芯粒技术成为破解高端芯片发展瓶颈的关键。北极雄芯此次推出的货架芯粒方案,不仅实现了核心IP的量产级突破,更以开放架构构建起“IC设计商-IP提供商-封装企业”的协同生态——IC设计商可直接采购标准化IP裸片,灵活组合成定制化方案,无需重复投入大IP流片。

未来,北极雄芯将持续完善芯粒产品矩阵,以高性价比、高灵活性的解决方案,助力更多企业快速切入AI、汽车电子、工业控制等高端芯片领域,共筑芯粒产业新未来。

如需了解北极雄芯货架芯粒产品参数、原型验证平台细节或合作方案,可扫描下方二维码联系,获取专属技术支持与采购咨询服务。