先睹为快:USB2.0 与 USB3.0 的核心差异

USB2.0 和 USB3.0 在传输性能上有着明显差距:USB2.0 传输速率高达 480Mbps,而 USB3.0 的最大传输带宽能达到 5Gbps,并且引入了全双工数据传输模式。

想要搞懂它们的 PCB 设计,先得认识它们的 “身份标识”—— 管脚定义。

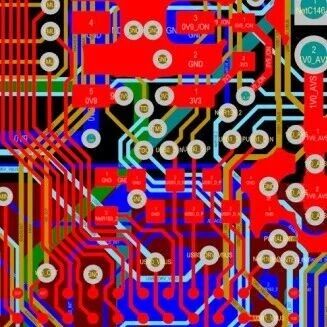

布局是 PCB 设计的基础,这一步没做好,后续再怎么优化都可能事倍功半。

- 接口位置要 “靠边”

:USB 接口得靠近板边或按照结构定位放置,除了直插类型,最好伸出板边一定位置。这就像咱们家里的插座,装在顺手的墙边才方便插拔,接口位置合理了,日常使用才顺畅。 - 保护器件 “排好队”

:ESD、共模电感器件要紧紧挨着 USB 接口,而且顺序不能乱,得是 ESD 在前,接着是共模电感,最后才是阻容元件。这就像咱们出门,先穿外套(ESD 防住静电 “寒气”),再戴口罩(共模电感过滤 “杂质” 干扰),最后拿上钥匙(阻容元件稳定 “状态”),一步都不能错。 - ESD 与 USB 留 “间距”

:要注意 ESD 和 USB 之间的距离,得给后焊留有余地。就像摆家具,得留够人走动的空间,不然后续想调整都难。 - 差分线路 “越短越好”

:布局时尽量让差分线路最短,缩短距离才能减少信号损耗。这好比两个人传话,距离越近,信息失真就越小。

布线就像给信号 “铺路”,路铺得好不好,直接影响信号传输的速度和稳定性。

- 差分走线有 “规矩”

:USB 要走差分线,阻抗控制在 90 欧姆,还要进行包地处理,总长度最好不超过 1800mil。这就像建高速公路,路面宽度(阻抗)得标准,两边的防护栏(包地)得到位,路程(长度)也不能太长,这样车子(信号)才能跑得又快又稳。 - 走线长度 “能短则短”

:尤其是高速 USB 差分(RX、TX 差分)的布线,要优先考虑缩短长度,而且尽量减少换层过孔。过孔就像路上的 “坑洼”,会让线路阻抗不连续,少用过孔才能更好地控制阻抗,避免信号反射。如果实在需要打孔换层,得在换层的地方加一对回流地过孔,帮信号 “顺畅掉头”。 - 保护地与 GND “划清界限”

:如果 USB 两边定位柱接的是保护地,分割时要保证它与 GND 的距离是 2MM,而且在保护地区域多打孔,确保充分连接。

外壳GND和信号GND的隔离

图中清晰展示了外壳 GND(保护地)和信号 GND 的隔离要求,2mm 的间距就像一道 “安全线”,能减少相互干扰。

- 差分线长 “求匹配”

:由于管脚分布、过孔、走线空间等因素,差分线长容易不匹配,这会导致时序偏差、共模干扰,降低信号质量。所以得进行补偿,让线长匹配,长度差通常控制在 5mil 以内。这就像跑步比赛,选手们得在同一起跑线(线长匹配),才能公平竞争(信号稳定传输)。

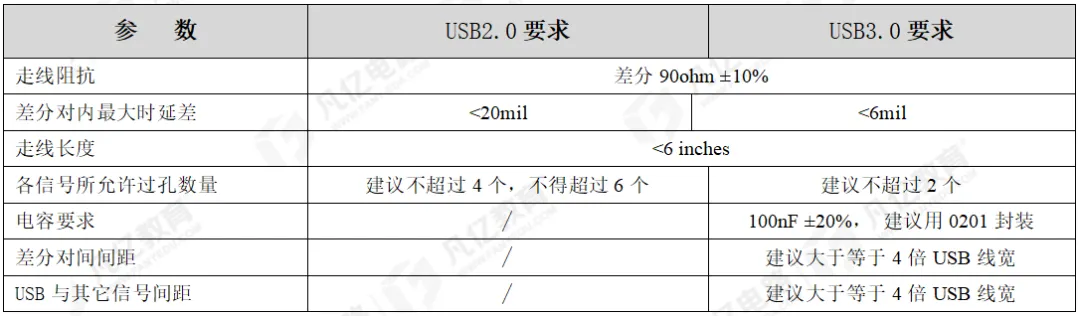

再看看 USB2.0 与 3.0 在 PCB 布线要求上的具体差异:

USB2.0与USB 3.0的PCB布线要求

从表格能清楚看出,USB3.0 在差分对内最大时延差、过孔数量等方面的要求比 USB2.0 更严格。比如差分对内最大时延差,USB2.0 要求 < 20mil,USB3.0 则要求 < 6mil,这也体现了 USB3.0 对高速传输的高标准。

下面两张图分别展示了 USB 2.0 和 USB 3.0 的布局与布线情况,能更直观地感受到它们的设计特点。

USB 2.0的布局与布线

USB 3.0的布局与布线

USB Type C(USB-C)接口凭借纤薄的设计、最高 10Gbps 的传输速度和最高 100W 的电力传输能力,以及双面可插的特点,在各类设备中应用越来越广泛。但要注意,Type-C 只是接口形式,和 USB 版本没关系。

先来看 Type-C 接口的管脚定义:

Type C接口的管脚定义

从图中能看到 Type-C 接口管脚众多,功能丰富,包含了高速数据传输路径、USB 2.0 接口等相关管脚。

Type C 接口的 PCB 设计有这些要点:

- 保护器件 “位置优”

:ESD、共模电感器件要靠近 Type C 接口,顺序也是 ESD→共模电感→阻容,同时注意 ESD 和 Type C 的距离,考虑后焊情况,这和前面说的 USB 接口类似,都是为了更好地保护信号。 - 耦合电容 “放得对”

:TX 信号线的耦合电容要靠近接口放置,RX 信号线的耦合电容则由设备端提供。

TX信号线的耦合电容

图中展示了 TX 信号线耦合电容的放置位置,靠近接口才能更好地发挥作用。

- 差分走线 “高标准”

:阻抗控制在 90ohm±10%,要有良好的参考平面,不跨分割,信号打孔换层不超过 2 个,保证阻抗连续。 - 差分线 “数量多,要求严”

:Type-C 有 RX/TX1-2 四组差分信号,两组 D+/D - 差分信号,共六对差分线。这些差分信号线至少要紧邻一个地平面,两边都紧邻地平面更好,走线要尽量短,最长不超过 6inchs。 - 线长与间距 “有规范”

:差分线长要匹配,对内等长误差 < 6mil;对内间距以及与其他信号的间距,建议都大于等于 4 倍 Type C 线宽,减少相互干扰。 - CC 引脚 “要加粗”

:CC1/CC2 引脚很关键,负责探测连接、区分正反面、区分主从设备等,走线时要加粗处理,就像给重要的 “指挥线路” 拓宽道路,保证指令畅通。

另外,当 Type-C 连接器工作速率≥8Gbps 时,要按照相关连接器优化建议设计处理。

Type-C连接器布线示意

图中展示了 Type-C 连接器布线的相关情况,能帮助我们更好地理解其布线设计。

看完这些,是不是对 USB2.0、USB3.0 和 Type-C 接口的 PCB 设计有了更清晰的认识?原来小小的接口背后,藏着这么多设计学问,正是这些细节,决定了我们使用设备时的传输体验。下次再用 USB 设备,你是不是也能多一份 “专业视角” 呢?