HPC的[中年危机],传统架构困在枷锁里

高性能计算(HPC)是科技领域的[基建],从天气预报到新药研发,从量子模拟到AI训练,都离不开它的支撑。

但近年来,支撑HPC的传统CPU与GPU架构,正逐渐显露出力不从心的疲态。

NextSilicon首席执行官Elad Raz曾尖锐地指出行业痛点:大规模代码重写、噩梦般的移植工程、飙升的能耗,以及微乎其微的性能增益,已成为常态。

这背后,是沿用80年的冯·诺依曼架构的固有局限,数据必须在内存和计算单元之间来回传输,形成了难以突破的内存墙;

更关键的是,为了支持通用计算,传统芯片把98%的硅面积都用在了分支预测、乱序执行、指令解码等[控制开销]上,真正用于核心计算的部分仅占2%。

当科研人员用C++写了一段流体力学模拟代码,若想迁移到英伟达GPU上加速,必须用CUDA语言重写;即便成功移植,GPU也会因为无法动态适配稀疏计算、图结构处理等场景,导致能效比骤降。

更尴尬的是,随着摩尔定律逼近极限,CPU/GPU的性能提升越来越慢,想要获得2倍算力,往往需要付出2倍以上的功耗和成本,这对需要大规模集群的HPC领域来说,无疑是不可持续的死循环。

行业急需一种新范式,既能保留通用计算的灵活性,又能拥有ASIC的高效能;既不用重写代码,又能动态适配不同任务。NextSilicon的Maverick2,正是冲着这个“不可能三角”来的。

Maverick2的核心创新,集中在两个词上:运行时可重构与数据流架构。这两个技术组合,彻底打破了传统芯片的[刚性思维]。

①运行时可重构:纳秒级[精准打击]热点代码

传统可重构芯片想要调整硬件逻辑,必须重启设备,根本无法适配实时变化的工作负载。

而Maverick2的运行时可重构,能在程序执行过程中,以纳秒级速度动态调整硬件结构,相当于芯片有了即时优化能力。

Maverick2的智能软件会实时监控应用,精准识别这些热点,然后立刻重构硬件,专门为这些关键代码打造定制化计算通道。

如果把传统GPU比作通用工厂,无论生产什么都用一套流水线;Maverick2就是灵活工坊,发现需要生产齿轮,立刻调整机床;

接下来要做螺丝,瞬间切换工具,全程不用停工。这样一来,宝贵的硅面积和功耗不再浪费在极少执行的代码上,效率自然飙升。

②数据流架构:绕开冯·诺依曼内存墙

为了彻底解决数据传输瓶颈,Maverick2采用了数据流架构,而非传统的冯·诺依曼架构。

在这套架构里,芯片的绝大部分面积都给了计算单元(ALU),远超CPU的2%占比,甚至比GPU的计算单元密度更高。

具体来说,数据不再是从内存到计算单元来回跑,而是像流水一样在ALU之间流动。

当数据到达某个ALU时,计算自动触发,结果直接流向需要它的下一个ALU;中间通过保留站(RS)暂存数据,内存入口点(MEPs)精准调度内存访问,全程没有多余的数据移动。

更关键的是,Maverick2的编译器能自动完成任务拆分,串行逻辑交给主机CPU,计算密集型任务则被转化为“中间表示”,映射到可重构硬件上,还能复制到多个ALU实现并行。

比如做AI推理时,芯片先配置为执行ReLU激活函数,几纳秒后就重构成矩阵乘法单元,全程无需人工干预。

③最大惊喜:不用改代码,直接加速

数据流架构过去一直难以普及,核心问题是编程难,必须用领域特定语言(DSL),兼容性极差。

而NextSilicon解决了这个历史性难题:Maverick2的软件栈支持C++、Fortran、Python、CUDA、ROCm、oneAPI,甚至主流AI框架TensorFlow、PyTorch。

也就是说,用户手里的旧代码,不用改一行,就能在Maverick2上获得加速。编译器会自动完成代码分割、硬件映射,运行时系统还会通过片上遥测持续优化。

如果两个子模块频繁通信,硬件会自动把它们的物理位置拉近;如果出现瓶颈,就动态复制计算单元提升并行度——这些操作,开发者完全看不见。

[再强大的硬件,若无法编程,便毫无价值。]NextSilicon联合创始人Ilan Tayari的这句话,正是Maverick2能落地的关键。

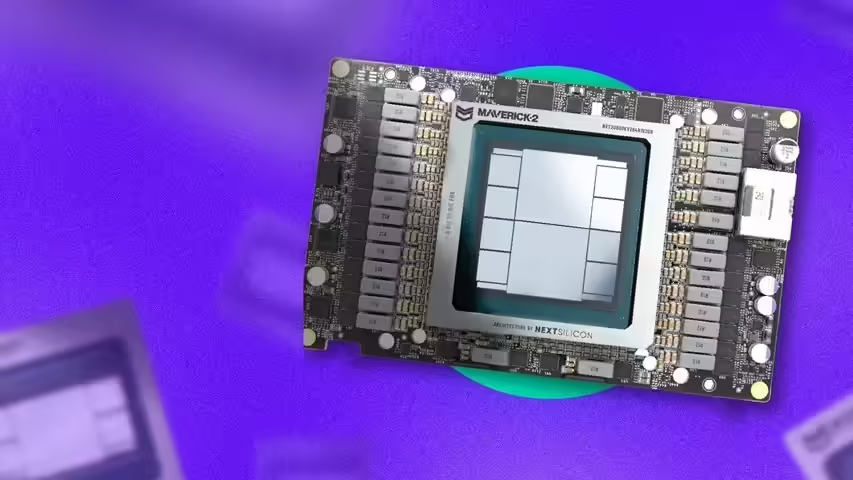

空谈技术不够,基准测试数据才是硬实力。Maverick2基于台积电5nm工艺制造,提供单芯和双芯两个版本。

单芯版集成96GB HBM3e显存,TDP 400W(风冷);双芯版集成192GB HBM3e,TDP 750W。在多项HPC测试中,它的表现让传统芯片相形见绌。

内存带宽(STREAM测试):达到5.2 TB/s,远超主流GPU的内存带宽上限,意味着数据传输速度更快;

内存更新性能(GUPS):460W功耗下实现32.6 GUPS,比CPU快22倍,比GPU快近6倍;

真实HPC负载(HPCG):750W功耗下实现600 GFLOPS,性能对标英伟达高端GPU,但功耗仅为后者的一半;

图算法(PageRank):吞吐量达40 gigapages/s,小规模图性能是GPU的10倍,还能处理超过25GB的大型图结构——而同类GPU根本无法运行这么大的图。

最后一块拼图,Arbel RISC-V CPU对标巨头

如果说Maverick2是加速引擎,那么NextSilicon最新披露的Arbel CPU,就是让这个引擎跑得更顺的关键,它要补上通用计算的短板,实现CPU+加速器的垂直整合。

Arbel是一款基于RISC-V架构的高性能CPU,定位直接对标英特尔的Lion Cove(Xeon系列核心)和AMD的Zen5(Epyc系列核心)。

其核心参数相当亮眼,台积电5nm工艺,最高主频2.5GHz,10发射宽核设计,配备480条重排序缓冲区,还有4个128位矢量单元,支持SIMD工作负载。

在架构上,Arbel有几个关键创新:

①宽指令流水线:10宽发射宽度能一次处理更多指令,核心利用率大幅提升;

②高效内存子系统:64KB L1指令缓存+64KB L1数据缓存+1MB L2缓存,解决内存延迟瓶颈;

③精准分支预测:Elite TAGE分支预测器减少错误预测,避免计算资源浪费。

NextSilicon做Arbel的逻辑很清晰,像英伟达用Grace CPU+Hopper GPU打造超级芯片一样,Arbel将与下一代Maverick3加速器搭配,形成通用计算+专用加速的全栈优化方案。

商业落地与未来,从国家实验室到AI新场景

目前,Maverick2已在数十家客户中部署,最受关注的是与桑迪亚国家实验室的三年合作。

桑迪亚国家实验室曾和NextSilicon合作设计和测试了Maverick-1数据流引擎,目前桑迪亚正在构建名为Spectra的新型架构超级计算机,这台超级计算机将使用Maverick-2数据流引擎构建。

NextSilicon的野心不止于HPC,按照规划,2027年推出的Maverick3将增加对低精度AI计算的支持,把可重构架构的优势拓展到AI训练与推理场景。

届时,Arbel CPU与Maverick3的组合,可能会在通用计算+AI+HPC的融合场景中,形成对英伟达Grace+Blackwell的直接竞争。

对行业而言,NextSilicon的意义远不止多了一款芯片,它证明了在摩尔定律放缓的时代,打破巨头垄断的关键,不是在现有架构上堆参数,而是用软件智能驱动硬件重构,用开放架构摆脱供应商锁定。

从英伟达凭借CUDA生态垄断HPC/AI加速器市场,到英特尔、AMD长期占据CPU领域,行业似乎已经习惯了巨头定义规则。

但NextSilicon的出现提醒我们:计算的未来,不该只有一种声音。

或许,NextSilicon未必能立刻颠覆英伟达、英特尔的地位,但它点亮的可重构+开放架构方向,已经为计算领域打开了一扇新门。

部分资料参考:AI科技汇:《NextSilicon发布运行时可重构架构》,芯片大师:《成立仅8年,这家初创公司,硬刚英伟达和AMD》,半导体行业观察:《一家芯片初创公司,单挑Nvidia和Intel》