DC-DC的电感值通常我们很少计算,会直接选择手册里面推荐的值,这在通常场景下快速展开设计和选型没有问题,但是当有特别的电源需求时,就需要自己手动计算电感并选型,才能满足我们的设计指标。

1.降压DC-DC的运转环路

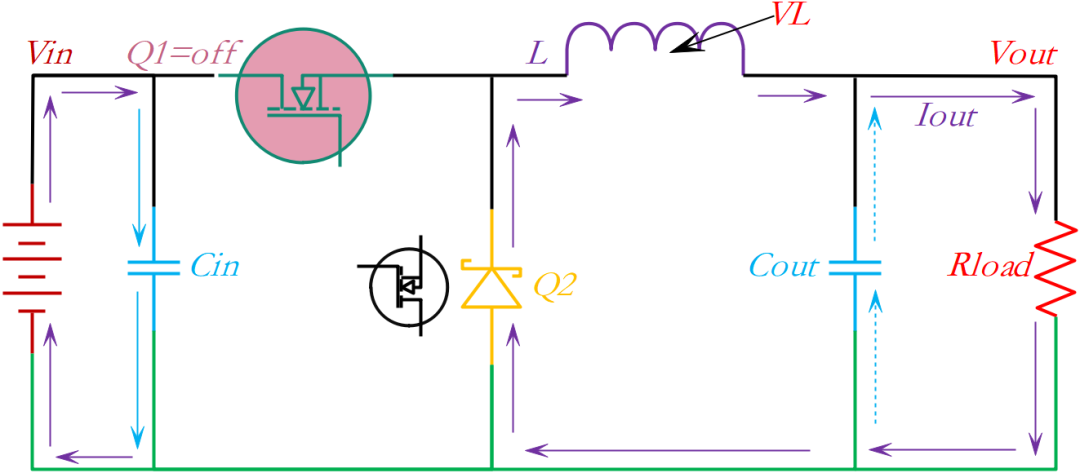

图15-1:Q1导通时的电流环路

如图15-1是在降压型DC-DC中,当开关器件Q1导通时,电流从Vin通过电感L给输出平滑电容Cout充电,并提供输出电流Iout。此时电感L上流过的电流会产生磁场,以此将电能变换成磁能并储存起来。

图15-2:Q2关断时的电流环路

如图15-2,当开关器件Q1关断时,续流二极管Q2导通,电感L里储存的能量向输出侧释放。在Q1导通阶段Cout已经储满电量,Q刚进入关断时,电感L反向电动势维持输出电流Iout,而后电感能量减弱,Cout就会开始参与放电维持Iout,注意看电容蓝色电流虚线。

2.电感的电流波形

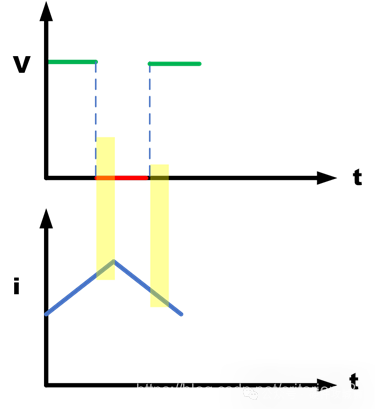

图15-3:流经电感L的电流波形

如图15-3是流经电感L的电流波形,Iout是电感电流的平均值。

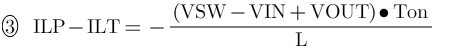

图15-1里开关器件Q1导通时电感L流过的电流,Q1导通ON的时间Ton,电感L上施加的电压VL(ON)用下式来表示:

其中VIN:输入电压;VSW:Q1导通时的压降;VOUT:输出电压

本身具有电感成分的电感L的电压VL和电流IL的关系用下式表示:

由公式(2)可以判断出给电感施加一定的电压,电压和反向电流会按照V/L的斜率增加,ILT是开关器件Q1在导通之前瞬间的电流,ILP是开关器件Q1在关断之前瞬间的电流。Ton时间段中电感流过的电流变化量可以根据公式(1)和公式(2)表示为下面公式。

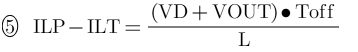

接着我们来求开关器件Q1在OFF时电感L流过的电流,Q1在OFF时,电感L上应加的电压VL(OFF)根据图15-2可以表示为下面公式:

其中VD:Q2的正向压降;VOUT:输出电压

通过公式(2)和公式(4),可以计算OFF时器件电感L的电流变化量

因为电感L流过电流的电荷量与输出电流的电荷量基本相等(伏秒定律),所以下面公式成立:

用公式(3)和公式(6)可以求出ON时器件的ILP:

用公式(5)和公式(6)可以求出OFF时器件的ILP,下面公式成立:

3.On duty的计算

On Duty是相对于开关振荡周期Tsw,开关器件的导通时间的比率。用下面公式表示:

从公式(7)、(8)、(9)可以求出D,如下面公式:

对于公式(10),如果忽略开关器件Q1的压降VSW和二极管Q2的压降,可以得到On Duty由输入电压和输出电压的比来决定:

4.线圈电流的最大值

由公式(9)和公式(10)可以算出Ton如下式:

把公式(12)代入到公式(7),可以得到电感L的电流最大值ILP如下式:

把公式(13)代入到公式(6),可以得到电感L的电流最小值ILT如下式:

电流的变化量 (ILP-ILT) 如下式:

由公式(13)和公式(15)可以推出最大电流和电流变化量随着电感L的增大、开关频率提高,电流值会减小。

5.电感值的计算

流过电感L电流的变化量 (ILP-ILT) 和输出电流Iout的比是电流纹波比R

把公式(15)代入到公式(16)

由公式(17)求出的电感L值的公式如下:

当输出电压VOUT很高的时候,公式可以简化如下:

要缩小R的话,增大电感,抑制ΔIL就可以了,但是电感器变大,变得不实用,所以降压型转换器通常设定在0.2~0.5的范围内。

6.线圈能流过的最大电流

电感能流过的最大电流可以用下式求得:

电感流过的电流是输出电流+纹波电流。输出短路等故障发生时,负载过渡状态中,没有软启动功能的IC在电源上升时,有时电感电流会超过上述计算的最大电流。在过渡状态下,电感电流可能会增加到IC的开关电流限制值。因此,最安全的方法不是按照大于电感电流最大值选择电感,而是选择额定饱和电流大于开关电流限制值的电感。

7.线圈流过的有效电流

三角波的有效值如下式表示:

把公式(13)和公式(14)代入公式(20)可以得到下列公式:

8.电感计算实例

列出降压型转换器的动作条件:

- 输入电压:VIN=12V;

- 输出电压:VOUT=3.3V;

- 输出电流:Iout=2A;

- 输出电流纹波比:R=0.3;

- 开关器件Q1导通时的压降:VSW=0.30;

- 续流二极管Q2的正向压降:VD=0.26,同步整流的时候,按照下管开关器件Q2在导通时的压降进行计算。

- 开关频率:fsw=380kHz

代入公式(18-1)和公式(18-2),求电感的感量,由公式(18-1)得:

由公式(18-2)得:

由公式(19)计算电感的最大电流:

由公式(20)计算电感的额定有效电流:

在设计的时候,选择满足计算值的电感,选择最接近的标准值10µH。选择的电感值和计算值有差异的时候,用公式(17)计算电流纹波值R,把这个值代入公式(19),再次计算线圈的最大电流:

回答: 刚刚好最好,过大过小都不好。

由公式可知:

电感值越大,其Ripple越小,亦即电流越稳定,进而降EMI辐射干扰;但过大的电感值,会使得瞬时反应变慢,亦即电流变化跟不上电压变化。有可能Switch Off时,电流却还在上升阶段;有可能Switch On时,电流却还在下降级段。

从自我谐振频率的角度分析:

一般来讲,功率电感的自我谐振频率至少要切换频率的10倍以上。例如, 若切焕频率2.5MHz,则自我谐振频率至少要大于25MHz。但我们也发现:功率电感值越大,则自我谐振频率越低,亦即越难达成上述目标。

从内阻的角度分析:

电感值越大,表示绕圈数越多,内阻越高,这会使得转换效率下降,以及加大IR Drop,所以我们归纳一下 功率电感值加大时的好处跟坏处。

很明显有好有坏,所以说:功率电感的值不是越大越好,不是越小越好,而是刚刚好最好。

A: 屏蔽电感对EMI等噪声干扰的屏蔽性相对会更好一些

Q: 计算公式是稳态CCM模式下推导的吗

A: 一般电感的计算公式都是参考临界连续或连续模式下的相对关系进行推导的,可以参考电力电子相关的电路设计公式推导过程哦

Q: 电感选型时需要关注哪些参数啊,包括使用环境、温度啥的

A: 通常电感的尺寸、额定电流、饱和电流、直流电阻等参数都需要考量,可以参考直播视频中讲解的重要影响参数。

Q: 电感的啸叫产生原因一般有哪些?

A: 电感啸叫通常与电感中流过的人耳范围内低频电流有关,这个可能由于负载电流的变化或者芯片本身的工作稳定性有关

Q: 通过感值变低的程度是不是可以判断电感的饱和电流?

A: 是的您说的对,一般电感下降到一定程度就可以判定此时电感是否饱和,实际可参考规格书中给出的具体值。

Q: 相同感值下的情况是不是饱和电流越大体积越大啊?

A: 通常来说,为了让电感有更强的磁通能力,饱和电流更大的相应尺寸也会稍有增大,具体可以参考我们官网的电感产品,可以看到更为详细的参数信息汇总。

Q: 过负载过电流情况是不是会造成电感损坏?

A: 过负载过电流情况得结合电感的饱和电流,若此时的负载电流比饱和电流过大,使得电感饱和现象加剧导致感量急剧下降时,就很可能造成电感的损坏。

Q: 电感的选型要依据什么?

A: 电感的选型可以参考MPS官网的计算工具,可为您推荐合适的电感

Q: 耐温最高可以达到多少度?

A: 您好,电感根据不同的材质和类型,耐温也有所不同,MPL的AL系列可达155度的高温。

Q: 实际电路中电感的损耗可以直接测量么

A: 电感的损耗可以参考视频中讲解,包括磁滞损耗、涡流损耗等多种类型需要分别考量,也可以根据效率及其他器件的损耗作初步估算。

Q: 在buck电路中,如果不太能确定负载电流具体有多大,电感取值怎么计算

A: 可以初步根据负载电流的范围设计一个电感,后续如果负载电流变化较大再作调整。

Q: 在石油石化领域的高温环境下有应用案例吗?其中耐受的最高温度是多少?

A: 高效率一体成型电感和半屏蔽电感可选,工作温度高达155°C。

Q: 电流RIPPLE的变化量是对应电感量变化量?

A: 增大电感,可以有效减少电感纹波电流,从而减小输出纹波电压。

Q: 电感饱和电流指标怎么知道?

A: 每个电感有对应的规格书可以供您参考,规格书里有详细说明各自的饱和电流。

Q: 请教一下,为增大电感量,使用四个电感器串联可以吗

A: 相同规格参数的电感串联可以使感值增加

Q: MPS可以做在线设计仿真吗?与其它品牌方案相比,有哪些优势呢?

A: 您好,可以进行在线设计仿真。我们的优势是:表面贴装电感适用于各类供电芯片和功率变换器应用。一体成型电感和半屏蔽式串联电感的电感范围为0.33μH至22μH,饱和电流范围为0.8A至64A。

Q: 开关电源中电感值怎么选择,与哪些因素有关系?

A: MPS电源芯片都有对应的电感设计方法及公式供参考,与电源的输入输出电压、开关频率、纹波电流设计等因素有关。

Q: 一体成型的电感为啥会比较好?

A: 一体成型磁屏蔽功率电感,软饱和感量特性良好,高温性能稳定,可以降低交流电和脉冲波频率所产生的音频噪声。

Q: 无线充线圈电感要分起绕点吗?起绕点接SW还是接谐振电容C

A: 起绕点接SW会更好些哦~

Q: 在选择开关频率后纹波的大小,输出电容怎么选择啊

A: MPS的电源芯片规格书中一般都会给出输出电容设计的相关公式,包含纹波的设计,可以根据实际的需求进行选取

Q: 在buck拓扑电路中,由于走线和器件的封装会带来杂散电感,此电感和开关器件的寄生电容结合造成LC振荡,请问在栅驱动电路中如何选取栅电阻可以有效减小该振荡

A: 栅极驱动电阻的取值参考官方手册来选取,结合其对开关损耗的影响,通常在满足IGBT正常工作的范围内,将电阻值尽可能取小。

Q: 有没有像芯片一样的电感器?SMT贴片类的产品,又轻薄又方便使用?

A: MPS提供的主要就是屏蔽式和一体成型式的表面贴装电感,可以登陆MPS官网查找合适规格的电感型号及规格书作参考。

Q: 在实际应用中,如何判断电感是否达到了饱和?有哪些方法?

A: 通常电感饱和后由于电感值的骤减会导致电路中的电流突然增大,斜率突然增大,可以观测实际的电感电流波形。

Q: 深度饱和时,带来的直接影响是什么?

A: 通常电感饱和后由于电感值的骤减会导致电路中的电感电流突然增大。

Q: MP9942输出5V 1A时,最低输入电压要多少?

A: 最低输入电压与芯片的最大占空比及线路中的电压损耗有关,需根据实际的电路板设计评估哦

Q: 饱和电流值也要大于OCP值吗?

A: 一般情况下,为了防止发生OCP短路造成电感饱和的现象,通常选取饱和电流大于OCP值更为安全。

Q: 电感设计时的裕量怎么设计考虑?

A: 通常需要考虑正常工作时的电感电流峰值及芯片的过流保护点。

Q: BUCK用工字电感,磁芯材料是什么材料

A: 工字电感的常见磁芯材质主要有:镁芯、镍芯和锰芯这三种类型。MPS主要提供屏蔽式和一体成型式的表面贴装电感为主。

Q: 请问开关电源电感啸叫是什么原因?

A: 电感啸叫通常与电感中流过的人耳范围内低频电流有关,这个可能由于负载电流的变化或者芯片本身的工作稳定性有关。

Q: 产生啸叫的时候通常怎么处理?

A: 电感发生异常啸叫一般是此时电感达到饱和状态,可以考虑重新选择适当饱和电流的电感。

Q: 电感和芯片的开关速度有没有关系?

A: 有的,电感量设计时需考虑开关电源的开关频率,可以参考MPS电源规格书中的电感设计推荐

Q: 电感附近不能布什么器件?

A: 电感附近主要放置的还是DC-DC中的控制芯片及功率器件,通常不建议布比较敏感的信号线路

Q: 自己制作电源,或者电源滤波等的时候,电感值如何计算选取,有什么规律和计算公式吗?

A: 通常需要根据系统的共模和差模噪声得到插入损耗再根据实际的滤波电路结构分别计算电感和电容的取值。MPS电源芯片一般都有相应的典型电路及滤波参数推荐,再结合实际的测试结果进一步调节。

Q: 电感电流理论上是锯齿波,时间常数是R/L,在什么情况下会导致时间常数不够,让电感电流看起来是弯的?

A: 当电感感量下降到邻近饱和或饱和状态时,电感的波形就会发生变化,出现您说的那种弯波,故通过实际测得的电感曲线也是一种直观判断电感饱和的方法。

Q: 减少emi问题的关键要素?

A: 针对系统来说EMI是一个综合考量的问题,需要考量噪声源和传播路径等所有相关因素,电感的话要注意尺寸、相连SW节点的面积及周围layout的走线等方面。

Q: 屏蔽电感一定是用的扁平铜线吗?

A: 我们的AL系列电感用的是扁平铜线设计的,扁平线的横截面积更大,阻抗低,通流能力好

Q: 刚才评判电流饱和时,ripple变化是指什么?

A: 指的是电感纹波电流变化。

Q: 如何测量精密电感值?

A: 可以选用LCR测试仪等专门的测试仪器哦

Q: 电感产品是不是都带屏蔽的?用于DCDC的小型电感一般有哪些封装应用?车规电感器要符合哪种标准?

A: 电感有屏蔽式电感和非屏蔽式电感的区分,屏蔽电感对EMI等干扰的屏蔽效果会更好,车规针对集成电路IC、LED以及电感这种被动器件都有相应的标准需要满足,如AECQ-100、AECQ-200等。

Q: 高温对电感值有多大影响?

A: 可以参考具体电感型号的规格书,但普遍来说,我电感感值受温度影响很小。

四、相同电感值下,优先选低DCR型号,减少发热损耗;高频电路(如射频)需关注自谐振频率,避免电感失效;工业场景建议预留20%电感值余量,应对电流波动。

五、DC-DC下方电感是否需要铺地处理?

DC-DC电源中一个很重要的元器件-电感。电感在该电路中主要发挥着储能的作用,在未达到电流饱和之前,流过电感的电流会持续上升,会产生变化率近似恒定的磁场,如果此时下方存在一块金属板,此时会在金属板上感应出近乎恒定的电压,由于金属板不可能电阻处处相等,将会在金属板上产生涡流,产生热损耗,如果频率更高,还会产生趋肤效应,磁滞损耗等能耗,而由于电感的定义是当导体通过单位安培的电流时其周围磁力线数量的度量,由于以上能耗的存在,此时电感的数值应是减小的,鉴于此,电感下方的金属板会消弱电感数值,但是对于屏蔽一体型电感,由于磁通量近乎不会泄露出去,因而就近乎不存在磁场能量消耗,因而电感感值不会明显降低。

以上都是理论分析,参考MPS demo板的实验:

对于DC-DC电源,Ldi/dt=Vout,通过电源内部调节,Vout是恒定不变的,dt也是恒定不变的,当L减小时,di则会相应增加,由于峰值电流增大了8%,可以推断此时电感感值有所下降。而对于屏蔽型电感,峰值电流近乎没有发生变化,可以推断此时电感感值近乎没有变化。

结合以上分析,下方铺地对屏蔽一体成型电感的感值是没有明显影响的。鉴于此,还是推荐下方进行完整GND铺地,一方面可以抑制辐射干扰,也可以降低接地阻抗,降低产生由于接地阻抗过高而产生的共模。