【编者按】

我们向万能的DeepSeek提出一些简单的半导体相关问题,看其回答能否满足你的要求。

1 技术目标与工艺要求的差异化

半导体薄膜沉积技术在现代集成电路制造中扮演着至关重要的角色,但在前道制造(FEOL/BEOL)和先进封装环节的应用存在显著差异。这种差异源于两者截然不同的技术目标和工艺要求,主要体现在结构复杂性、精度需求以及环境限制等多个维度。

1.1 前道制造:纳米级精度与原子级控制

在前道制造领域,薄膜沉积是构建晶体管等核心器件的基础工艺。随着制程节点不断微缩至3nm以下,对薄膜的厚度均匀性和成分控制提出了近乎苛刻的要求:

高k金属栅极(HKMG):需沉积超薄(纳米级)的高k介质层(如HfO₂)替代传统SiO₂,大幅降低栅极漏电流。微导纳米开发的High-k原子层沉积设备已实现量产应用,厚度控制在原子层级(0.1nm精度),满足28nm以下逻辑芯片需求。

互连层铜扩散阻挡:采用Ta/TaN等阻挡层防止铜扩散至低k介质,要求薄膜具有超高致密性和无针孔特性。台积电在5nm工艺中通过优化Ta/TaN阻挡层,成功将Cu互连的RC延迟降低30%2。

三维结构保形性:在FinFET和GAA晶体管中,薄膜需在高深宽比结构(>10:1)表面实现均匀覆盖。原子层沉积(ALD)技术凭借其自限制反应机制,可在沟槽侧壁和底部实现单原子层精度沉积,避免传统CVD可能出现的“封口”缺陷。

表:前道制造关键薄膜沉积应用及技术要求

1.2 先进封装:异质集成与应力管理

先进封装领域的薄膜沉积聚焦于实现异质芯片集成和机械应力控制,对精度的要求相对宽松(微米级),但面临独特挑战:

再布线层(RDL):需在有机基板或硅中介层上沉积Ti/Cu种子层,要求薄膜具有低残余应力和高附着力,避免后续电镀过程中发生剥离。扇出型封装(Fan-Out)中,薄膜需耐受>200℃的工艺温度而不翘曲。

硅通孔(TSV)绝缘层:在3D堆叠芯片中,TSV孔壁需沉积SiO₂或SiN绝缘层。深宽比通常达10:1以上,要求沉积具备优异台阶覆盖性。ALD技术在此领域展现出独特优势,如三星在176层3D NAND中实现SiCN绝缘层缺陷密度<0.1个/cm²。

EMIB中介层阻挡:英特尔嵌入式多芯片互连桥(EMIB)技术中,需在超低k介质(k<2.5)表面沉积阻挡层,击穿场强需>10MV/cm,同时避免损伤脆弱的多孔结构。

1.3 温度敏感性与兼容性挑战

温度限制是两大领域差异最显著的因素之一:

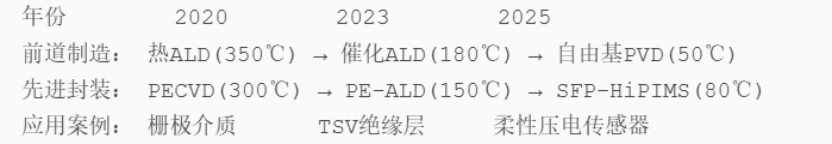

前道工艺:高温沉积(>400℃)可提升薄膜质量,如LPCVD-SiO₂需稳定在±1℃内控制热应力。但HKMG后段工艺需限制在450℃以下,避免损伤金属栅。

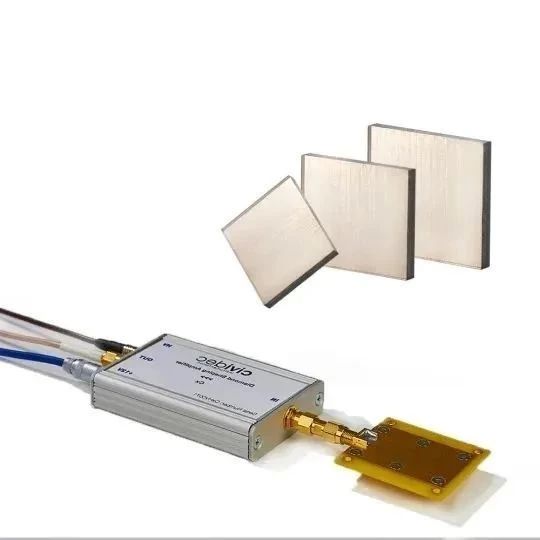

先进封装:有机材料和已完成前道工艺的芯片对温度极为敏感,通常要求低温工艺(<250℃)。等离子体增强ALD(PE-ALD)技术通过在低温下激活反应,可在聚酰亚胺(PI)基板上沉积Al₂O₃阻隔层,水汽阻隔率达4.8×10⁻⁴ g/m²/day。瑞士Empa实验室最新开发的SFP-HiPIMS技术甚至能在绝缘基底上实现低温高质量压电薄膜沉积,为RF滤波器等封装集成器件开辟新路径。

图:薄膜沉积温度窗口对比示意图

2 材料与设备特性的针对性选择

半导体薄膜沉积技术在材料体系、设备配置和工艺整合方面,前道制造与先进封装存在显著差异。这些差异源于两者不同的技术目标和物理限制,直接影响了薄膜材料的选择和设备设计的优先级。

2.1 阻挡层与功能薄膜的材料创新

在前道制造领域,薄膜材料需满足电学性能和尺寸微缩的双重要求:

High-k介质材料:HfO₂、ZrO₂等替代传统SiO₂作为栅极介质,介电常数提升至以上,等效氧化层厚度(EOT)降至0.5nm以下。微导纳米的High-k ALD设备已实现量产,通过精确控制前驱体脉冲时间(误差<1ms),确保原子级厚度均匀性。

金属扩散阻挡层:随着铜互连线宽缩至10nm级,传统TaN阻挡层占比过高(达30%以上),亟需超薄新材料。台积电在3nm节点引入RuMo合金阻挡层,厚度降至0.8nm,电阻率降低40%。

选择性沉积技术:通过表面预处理(如自组装单分子层)实现仅在特定区域沉积薄膜,避免光刻步骤。应用材料公司的Olympia系统可在铜线上选择性沉积CoCap层,显著提升电迁移可靠性。

在先进封装领域,材料选择更注重机械应力匹配和异质兼容性:

低应力复合阻挡层:TiW/Cu体系在硅转接板(Interposer)中广泛应用,通过梯度成分设计降低热膨胀系数(CTE)失配。三星在3D IC封装中采用Ti/Al/Ni/Au多层金属,接触电阻<0.1mΩ·cm²,良率达99.8%。

柔性封装薄膜:针对可穿戴设备需求,PE-ALD制备的Al₂O₃/SiO₂纳米叠层成为主流,通过残余应力调控(压应力↔拉应力平衡),使柔性基板在1.08%弯折应变下阻隔率仍保持<10⁻³ g/m²/day。

热界面材料(TIM):3D堆叠中需在芯片间沉积高导热聚合物(如聚酰亚胺衍生物),导热系数>5W/mK,同时具备电气绝缘性。

2.2 沉积设备与工艺整合差异

设备架构和工艺整合要求在前道与封装领域呈现明显分野:

前道沉积设备:追求原子级控制和超高洁净度

ALD反应腔:配备多重前驱体输送系统,支持多达8种不同前驱体的精确注入。微导纳米最新设备采用分区温控技术,实现晶圆内温度波动<0.1℃。

真空环境:腔体真空度维持<10⁻⁷ Torr,每月执行高温烘焙(>150℃)去除有机残留,金属污染控制<0.1ppb。

原位监测:集成椭偏仪和X射线反射(XRR),实时测量膜厚(精度0.1nm)及成分。

封装沉积设备:强调异质兼容和生产效率

卷对卷(R2R)ALD:适用于柔性基板连续沉积,如屹立芯创晶圆贴膜系统集成R2R供收膜模块,UPH(每小时产能)提升40%。

多工艺集成:真空贴压膜设备将沉积与压合功能整合,在高洁净真空环境(ISO Class 1)中完成无气泡贴膜,消除后续曝光缺陷。

基板适应性:设备需兼容硅、玻璃、有机树脂等不同基材。Empa开发的SFP-HiPIMS技术突破性解决绝缘基底电压施加难题,通过“电子淋浴”定时加速靶材离子,避免氩气掺入。

表:前道与封装薄膜沉积设备核心参数对比

2.3 缺陷控制与量测技术的分野

缺陷控制策略在两大领域呈现不同侧重点:

前道制造:聚焦纳米级缺陷检测

采用高灵敏度电子束检测(EBI),识别>10nm的微桥缺陷

晶圆边缘30%区域缺陷密度通常高出中心区,需特殊优化

AI驱动的缺陷预测模型(如台积电应用技术)准确率达95%,提前调整工艺参数

先进封装:应对宏观结构缺陷

X射线检测TSV孔填充率,避免微空洞产生

红外热成像识别界面分层,散热不均问题

真空贴膜工艺消除气泡缺陷,根源性提升良率

量测技术同样呈现差异化需求:

前道:透射电镜(TEM)分析界面原子结构,XPS检测薄膜化学态

封装:白光干涉仪测量铜柱高度差(精度±0.1nm),激光超声检测胶层固化度

3 先进技术发展动向与融合趋势

半导体薄膜沉积技术正以前所未有的速度演进,前道制造与先进封装领域在部分尖端技术上呈现交叉融合态势,同时各自发展出独特的技术路线。这种动态发展既受摩尔定律持续微缩的驱动,也受异质集成需求的深刻影响。

3.1 低温沉积技术的突破性进展

低温薄膜沉积已成为两大领域共同关注的焦点,但技术路线各有侧重:

前道制造中的低温突破:

热ALD低温化:通过前驱体分子设计(如含氯硅烷替代品),将SiO₂沉积温度从350℃降至150℃,避免后段工艺中的氢脆问题。关键突破在于反应能垒的降低,微导纳米研发的催化增强ALD技术,在100℃下实现膜质密度>2.2g/cm³。

自由基增强PVD:应用材料公司最新PVD设备集成远程等离子源,产生高密度氢自由基,使TiN阻挡层沉积温度降至50℃,电阻率较传统工艺降低30%。

先进封装的低温创新:

SFP-HiPIMS技术:瑞士Empa实验室的革命性成果,通过精准控制磁控管脉冲时序,利用“电子淋浴”原理在绝缘基底上实现低温高质量薄膜沉积。其核心技术在于:在氩离子飞越基板后的精准时刻施加电压,仅加速所需的靶材离子(如Al⁺),避免氩气掺入。该技术首次在玻璃基板上制备出压电性能媲美高温工艺的AlN薄膜。

等离子体增强ALD(PE-ALD):在柔性显示封装中广泛应用,华中科技大学开发的PE-ALD设备在80℃下沉积Al₂O₃/SiO₂叠层,水汽阻隔率达7.76×10⁻⁴ g/m²/day,弯折100次后仅上升至1.10×10⁻³ g/m²/day。

图:低温沉积技术温度演进路线

3.2 高深宽比结构工艺的革新

随着3D结构在两大领域的普及,高深宽比(HAR)沉积技术迎来爆发式发展:

前道制造中的HAR挑战:

DRAM电容深孔:深宽比超60:1,需在直径<100nm的深孔内沉积交替Al₂O₃/TiN层。关键突破在于空间ALD(Spatial ALD)技术,通过晶圆与喷头相对运动实现连续沉积,速率达传统ALD的10倍。

3D NAND通道孔:176层以上堆栈中,通道孔深>5μm,孔径<100nm。三星采用交替脉冲CVD技术,在孔内沉积复合阻挡层(SiN/AlO),厚度不均匀性<3%。

先进封装的HAR解决方案:

TSV绝缘层沉积:硅通孔深宽比达10:1,屹立芯创开发的气囊式压合技术结合PE-ALD,实现深孔内均匀成膜(覆盖性>95%),支持1:20深宽比结构。

混合键合界面:铜-铜直接键合要求表面超高平整度(<2nm RMS),低温ALD沉积超薄TiN扩散阻挡层(厚1nm),键合强度>10J/m²。

3.3 智能化与数字孪生技术的渗透

薄膜沉积工艺的智能化控制正成为两大领域的共性趋势:

前道制造的AI优化:

台积电建立神经网络模型,分析200+工艺参数与缺陷的关联性,将薄膜应力预测准确率提升至95%。

微导纳米在ALD设备中集成实时反馈系统,通过激光干涉仪监测膜厚,动态调整前驱体脉冲时间。

先进封装的数字孪生:

屹立芯创真空贴膜系统构建虚拟工艺平台,实现压力-温度-真空度的闭环控制,减少试错成本30%。

基于机器学习的薄膜应力匹配系统,预测Al₂O₃/SiO₂叠层残余应力分布,优化封装结构抗弯折能力。

3.4 绿色制造与材料创新的融合

环保前驱体开发:水基前驱体替代传统有机金属化合物,如微导纳米在High-k沉积中采用无氯Hf前驱体,降低碳足迹40%。

自修复薄膜:应用于先进封装的SiOCN介质层,含硅氧烷聚合物可在150℃下自动修复微裂纹,提升器件可靠性。

石墨烯阻挡层:实验室阶段突破,单层石墨烯作为铜互连扩散阻挡层,电阻率较TaN降低90%,有望颠覆传统材料体系。

4 产业竞合与供应链影响

薄膜沉积技术的演进正深刻重塑半导体产业链格局,前道制造与先进封装之间的传统界限日益模糊,催生出“中道工艺”(Middle-end-of-Line, MEOL)这一新兴领域,并引发晶圆厂、封装厂和IDM企业之间复杂的竞合关系。

4.1 中道工艺区的模糊化趋势

台积电率先提出“3DFabric”平台架构,将先进封装细分为前端与后端技术:

前端封装技术:包括SoIC(集成芯片系统)的CoW(Chip-on-Wafer)和WoW(Wafer-on-Wafer)等晶圆级堆叠工艺。此类技术需在前道晶圆厂内完成,涉及高精度薄膜沉积(如微凸块下扩散阻挡层)、晶圆减薄和混合键合等步骤。本质上是前道工艺的延伸,要求洁净室等级和工艺精度与传统前道产线一致。

后端封装技术:涵盖InFO(集成扇出型)和CoWoS(基板上晶圆上芯片)等异质集成技术,可在传统封装厂执行。薄膜沉积主要应用于RDL(再布线层)种子层和EMIB(嵌入式多芯片互连桥)中的绝缘层,对精度要求相对宽松(微米级),但需兼容多样化基材。

这种划分导致传统供应链重构:

晶圆厂向下延伸:台积电凭借CoWoS技术将业务延伸至封装领域,其南京工厂整合了12nm前道工艺与3D封装产线,实现单厂全流程制造。

封装厂向上突破:日月光通过收购矽品精密和成立Fan-Out Alliance,发展晶圆级封装能力,其FoCoS(Fan-out Chip on Substrate)技术整合了硅中介层沉积工艺。

设备商跨界整合:应用材料推出“集成材料解决方案”(IMS),将PVD、CVD和电镀设备整合为统一平台,满足从3nm前道到3D封装的全流程需求。

4.2 厂商战略布局与技术壁垒

不同背景厂商基于自身优势构建技术壁垒:

晶圆厂(Foundry)核心优势:

硅工艺积累:对Si/SiGe/SiC等材料的深刻理解

高精度设备:12寸晶圆处理能力,原子级控制技术

设计协同能力:与EDA工具深度整合,支持Co-design

代表案例:英特尔Foveros Direct技术,直接在晶圆厂完成3μm间距混合键合

封装厂(OSAT)突围路径:

异质集成经验:多材质(有机/无机/金属)复合结构处理

成本控制能力:高性价比解决方案

快速响应服务:灵活支持中小客户

代表案例:江苏长电科技XDFOI™技术,在有机基板上实现0.8μm线宽RDL

IDM差异化战略:

全流程优化:从设计到封装的协同优化

专有技术保护:如三星V-NAND中的独特堆叠工艺

垂直整合优势:存储器与逻辑芯片定制化封装

代表案例:三星I-Cube4技术,集成4颗HBM与逻辑芯片,TSV绝缘层采用专有SiCN配方

4.3 国产化机遇与挑战

中国半导体设备厂商在薄膜沉积领域迎来历史性机遇,但仍面临多重挑战:

前道设备国产化进展:

微导纳米ALD设备:国内首家量产High-k前道设备厂商,半导体薄膜沉积设备销售额从2021年0.25亿元增至2024年3.32亿元(CAGR 136.21%),在手订单达15.05亿元。近期募资11.7亿元建设智能化工厂,达产后预计年增收入15.65亿元。

北方华创PVD/CVD:28nm节点设备进入中芯国际产线,14nm设备验证中。

主要挑战:前驱体纯度不足(金属杂质>0.1ppm),设备稳定性(MTBA<200小时)与国际领先水平(>500小时)仍有差距。

封装设备突破亮点:

屹立芯创晶圆级真空贴压膜系统:解决先进封装气泡难题,专利软垫气囊技术支持1:20深宽比结构,已交付行业标杆客户。

中微公司TSV深孔刻蚀设备:深宽比达40:1,配套PECVD绝缘层沉积模块。

独特优势:贴近本土封装厂(如长电/通富微电),快速响应工艺优化需求。

表:中国薄膜沉积设备国产化现状与目标

结论:融合与分化并存的未来之路

半导体薄膜沉积技术在前道制造与先进封装领域正呈现技术融合与专业分化并行的演进态势:

技术融合点:

低温沉积成为共同焦点:前道工艺因后段热预算限制走向低温化(如催化ALD),封装因应有机材料需求开发超低温技术(如SFP-HiPIMS)。

3D结构需求驱动高深宽比工艺:无论是DRAM深孔还是TSV通孔,均需ALD等高保形技术支撑。

智能化控制成为标配:AI工艺优化与数字孪生平台在两大领域快速渗透。

专业分化点:

精度要求分层化:前道坚守原子级控制(0.1nm),封装侧重微米级均匀性与应力管理。

材料体系分道扬镳:前道聚焦High-k/金属栅等纳米材料,封装发展低k介质/柔性薄膜等复合体系。

设备形态差异:前道追求极限精度与纯净度,封装设备需兼顾多样化基材与高效率。

产业格局重构:

中道工艺区(MEOL)崛起,台积电3DFabric等平台模糊传统界限。

晶圆厂与封装厂相互渗透,竞合关系动态演进。

国产设备商迎来机遇期:微导纳米在前道ALD实现突破,屹立芯创在封装贴膜系统建立优势。

未来半导体薄膜沉积技术的发展将更加注重应用场景适配性——前道制造继续追求摩尔定律的物理极限,而先进封装则致力于拓展异质集成的边界。中国产业需在材料纯度、设备稳定性等基础领域持续突破,同时把握Chiplet技术带来的封装沉积新需求,构建差异化竞争优势。

*主要参考来源:

微导纳米拟发债募资不超11.7亿元 投建半导体薄膜沉积设备智能化工厂

https://finance.ifeng.com/c/8lWO2TtaNft?ch=ttsearch

半导体阻挡层薄膜材料注意事项:工艺优化与质量控制全解析

https://www.sohu.com/a/920605422_122053459?scm=10001.325_13-325_13.0.0.5_32

芯启未来,智创生态