我经常浏览电子和PCB论坛,经常看到一个反复出现的问题:为什么不应该在接地平面的分叉处布线?从创客到初涉高速PCB设计的专业设计师,每个人都会问这个问题。对于专业的信号完整性工程师来说,答案应该是显而易见的。

无论您是资深PCB布局工程师还是业余设计师,理解这个问题的答案都会有所帮助。答案总是被概括为“永远/永远”。我通常不喜欢用绝对的术语来回答PCB设计问题,但在这种情况下,答案很明确:切勿将信号布线穿过接地平面的间隙。让我们进一步深入探讨这个问题,了解为什么不应该将走线穿过接地平面的间隙。

接地平面间隙:低速和高速设计

要回答这个问题,需要考虑信号在直流、低速和高速下的行为方式。这是因为每种类型的信号都会在此参考平面上产生不同的返回路径。信号所遵循的返回路径会对电路板内部产生的EMI以及特定电路对EMI的敏感性产生一些重要影响。为了更好地了解PCB中返回路径的形成方式,请参阅这篇文章以及Francesco Poderico提供的实用指南。

如果您了解 PCB 中返回电流的形成方式,那么就很容易理解它如何影响 EMI 和信号完整性。这就是为什么它如此重要——它与跨接地平面间隙的布线有关。电路板中返回电流形成的环路决定了两个重要行为:

EMI 敏感度。电路中电源和返回电流形成的环路决定了电路板对 EMI 的敏感度。电流环路较大的电路寄生电感较大,因此更容易受到辐射 EMI 的影响。

开关信号中的振铃。电路中的寄生电感决定了信号在电平之间切换时电路瞬态响应所经历的阻尼水平。与电路中的寄生电容一起,这两个量决定了瞬态响应的固有频率和阻尼振荡频率。

让我们详细了解一下直流、低速和高速信号:

直流电压/电流

当电路板使用直流电源供电时,返回电流不会直接在信号走线下方产生;它会沿直线返回电源返回点。这意味着您实际上无法控制返回路径,并且由于较大的寄生电感,电路板可能容易受到电磁干扰 (EMI) 的影响。人们可能会认为,由于电源不切换,所以不会出现瞬态振荡,因此即使微带线走线穿过接地层间隙也无妨。即使没有振荡,仍然存在 EMI 敏感度问题。您应该尽量降低直流环路电感,避免穿过接地层间隙是降低环路电感的最佳方法。

低速信号

与直流信号一样,返回路径决定了电路的环路电感,从而决定了瞬态响应中的EMI敏感度和阻尼。如果环路电感较大,则阻尼率会较低,并且与直流信号的情况一样,通过接地层间隙布线会增加环路电感,从而影响信号完整性、电源完整性和EMI。

遗憾的是,低速信号已成历史,所有使用TTL及更快逻辑的电路板都会表现得像高速电路。对于低速信号(通常上升时间为数十纳秒甚至更慢),特定电路中的振铃幅度通常足够低,以至于难以察觉。因此,只要信号不经过接地层间隙,环路电感通常足够低,可以避免强烈的振铃、EMI敏感性以及相关的电源完整性问题(见下文)。

高速信号

如果我拿一块设计为低速运行的电路板,并用高速信号运行它,那么在给定电路环路电感的情况下,振铃幅度会更大。这再次说明了需要尽可能地减小电路板中的环路电感。目标是提供尽可能多的阻尼,以降低给定互连中的振铃幅度。同样,在接地层间隙上布线可以避免增加环路电感。此外,接地层应放置在承载高速电路的信号层下方,以确保整个互连中的环路电感尽可能低。

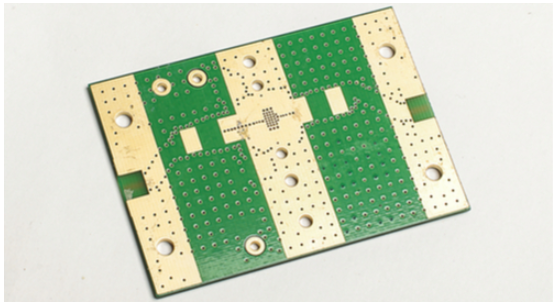

通过接地平面间隙的信号返回路径示例。

另一种看待接地平面间隙的方式是将其视为阻抗不连续。如果信号通过接地平面间隙进行布线,间隙上方区域的阻抗将大于互连其余部分的阻抗。这除了加剧上述振铃问题外,还会导致信号反射。阅读《信号完整性杂志》的这篇文章,了解更多关于接地平面间隙高速信号传输方面的问题。

上述关于数字信号的所有讨论同样适用于模拟信号。上述瞬态信号问题与电源完整性问题相关,尤其是在使用高门/引脚数元件的电路板上。电路板层堆栈应专门设计,以支持速度高于TTL的元件(见下文)。

电源轨和接地平面间隙

请注意,我们是从信号完整性的角度来探讨这个问题的,但同样的理念也适用于电源完整性。正如微带线不应跨越接地层间隙一样,也应避免将表层的电源轨跨越接地层间隙。如果为数字IC提供直流电源,IC在开启和关闭状态之间切换时会从电源汲取一些电流。这会在电源轨上产生电压纹波。

电源电压中的这种特殊瞬态响应表现为阻尼振荡。其幅度与PDN的阻抗成正比,与PDN的阻尼水平成反比。正如标准PCB互连中阻尼与环路电感成反比一样,PDN中的瞬态响应也是如此。这意味着,如果保持环路电感较小,就可以抑制电源轨上的瞬态响应。最佳方法是将接地层放置在与电源层直接相邻的层上,并避免将任何电源轨布线在任何接地层间隙上。

如果您使用的是双层电路板,并且没有足够的空间放置接地层,则应仔细规划电路板的返回路径,以保持环路电感较小。一种选择是在顶层和底层采用网格状的接地区域布局,并通过过孔将它们连接起来。但是,如果您处理的是高速信号(TTL 及更快),由于PDN 中的电容不足,您将看到电源轨上出现较大的电压波动。这是高速电路板中电源层和接地层位于相邻层,并且接地层直接位于信号/元件层下方的主要原因。

END

点击了解活动详情

点击了解活动详情往期精选:

请点下【♡】给小编加鸡腿